## A 59mW 10b 40Msample/ s Pipelined ADC<sup>\*</sup>

Li Jian<sup>1</sup>, Yan Jiefeng<sup>1</sup>, Chen Jun<sup>1</sup>, Zhang Jianyun<sup>1</sup>, Guo Yawei<sup>2</sup>, Shen Bo<sup>1,†</sup>, and Tang Ting 'ao<sup>1</sup>

(1 ASIC and System State Key Laboratory, Fudan University, Shanghai 200433, China) (2 Shanghai MicroScience Integrated Circuits Co., Ltd, Shanghai 200433, China)

Abstract: This paper describes a 3. 0V, 10b, 40M sample/s analog-to-digital converter (ADC) fabricated in a 0. 25µm CMOS technology. Through the sharing an amplifier between two successive pipeline stages, the converter is realized using just four amplifiers with a separate sample-and-hold block. It employs two key techniques: a high bandwidth low-power gain-boosting telescopic amplifiers technique and a low power low offset dynamic comparators technique. The ADC achieves a 8.1 effective number of bits a maximum differential nonlinearity of a 0.85 least significant bit (LSB), and maximum integral nonlinearity of 2. 2LSB for a 0.5MHz input at full sampling rate. It occupies 1. 24mm<sup>2</sup>, which also includes a bandgap and a voltage reference circuit and dissipates only 59mW.

Key words: analog-to-digital converter; low power; OPAMP sharing technique; gain-boosting technique EEACC: 1265 H; 1280; 2570D Article ID: 0253-4177 (2005) 07-1301-08

CLC number : TN432 Document code : A

#### 1 Introduction

High-speed, high-resolution A/D conversion is important in a wide variety of commercial applications, such as data communication and storage. These applications often use complex modulation and detection schemes such as quadrature amplitude modulation (QAM), which usually requires extensive digital signal processing at the receiver. Thus, the front end of such a receiver typically needs a high-speed A/D converter (ADC). Many of these applications make use of 10bit analog-to-digital converters (ADC's) sampling at around 40M Hz<sup>[1]</sup>. And ,in most applications ,the reduction of power consumption is one key design issue.

The ADC described in this paper has been designed to meet the 10bit 40Msample/s require-

ments and also features a low power consumption. The power reduction is achieved by using power efficient pipeline architecture, sharing an amplifier between two successive stages in the pipelined ADC, employing high bandwidth low-power gainboosting telescopic amplifiers and low-power lowoffset dynamic comparators, as well as using a capacitor size scaling down scheme. The measured results are much better than those of Refs.  $[9 \sim 11]$ which concern state-of-art AD converters. The power efficiency of this work is excellent ,even in real world situations.

#### ADC architecture 2

In general, pipelined ADCs have been proven to be power efficient architectures. In pipeline converters, power consumption can be optimized by an

Received 27 December 2004 , revised manuscript received 18 March 2005

<sup>\*</sup> Project supported by the Shanghai Municipality IC Design Innovation Project (No. 047062008)

Li Jian male, was born in 1980, PhD candidate. His main research interest focuses on analog-to-digital converters.

Tang Ting 'ao male, was born in 1939, professor, PhD advisor. His main research interests are in the area of process and design of integrated circuits.

Shen Bo male, was born in 1975, PhD. His main research interests are in the area of communication circuits design.

<sup>†</sup> Corresponding author, Email: boshen @fudan.edu.cn

appropriate selection of bits/ stage<sup>[2]</sup> and capacitor scaling down the pipeline<sup>[3]</sup>. Furthermore, using the amplifier sharing technique to share an opamp between two consecutive stages in the pipeline causes a further significant power reduction in a pipelined ADC<sup>[4]</sup>. An attractive method of realizing a high-speed ADC is to use a pipeline architecture where each stage has a resolution of 1. 5b<sup>[5]</sup>. This 1. 5bits/ stage architecture has two benefits. The first is to maximize the bandwidth of the SC (switched-capacitor) circuit. With such a resolution, the closed-loop gain equals 2, which allows for low load capacitance and a large feedback factor. As a result ,a large interstage amplifier bandwidth can be achieved. The second benefit is that it allows for a large correction range for comparator offsets in the flash ADC, where only two comparators are required for every stage. Thus comparator offsets up to  $\pm V_{\text{ref}}/4$  can be tolerated.

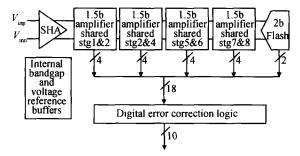

Consequently, a 1. 5bits/ stage pipeline with amplifier sharing topology is adopted for the converter. Figure 1 presents the architecture of the converter.

Fig. 1 Block diagram of the ADC

## 2.1 Sample and hold amplifier circuit

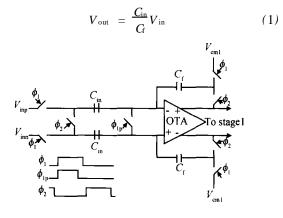

The implementation of the sample and hold amplifier (SHA) is shown in Fig. 2. The SHA is capable of dealing with high-frequency inputs with low distortion by using constant  $V_{GS}$  sampling switches, which use a bootstrapping circuit and are designed to observe device reliability considerations. The input voltage is sampled on capacitors  $G_{in}$  at the end of the sample phase  $\Phi_{ip}$ . During the hold phase  $\Phi_2$ , the charge from  $G_{in}$  is transferred to feedback capacitors Cf such that the output is

Fig. 2 SHA circuit

#### 2. 2 Amplifier sharing blocks

Each amplifier sharing block is made up of two consecutive stages sharing one amplifier and one clock generator. Each sharing block (actually equivalent to two conventional 1. 5bits stages) provides four bits of digital output. The four bits from the four sharing blocks and the two bits from the flash are transferred to the digital error correction logic block and ,in the end ,provide ten bits of digital output.

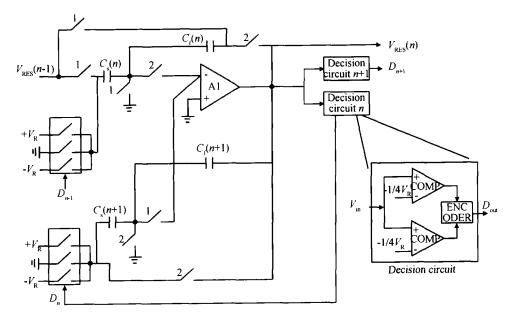

The implementation of each sharing stage is shown in Fig. 3. Here ,for simplicity ,a single-ended configuration is shown , though the actual implementation is fully differential.

Amplifier sharing is based on the fact that ,in switched-capacitor architecture, the amplifier is used for only one half of a clock cycle, which is during the amplification phase.

The operation of the sharing stage can be briefly described as follows. There are two switched-capacitor networks operating on opposite clock phases with the opamp alternating between them. During phase 1,  $C_s(n)$  and  $C_t(n)$  sample  $V_{\text{RES}}(n-1)$ . During phase 2, the residue  $V_{\text{RES}}(n)$  is produced by  $C_s(n)$ ,  $C_t(n)$ , and A1 operating under the control of the digital input  $D_{n-1}$ . This is sampled by  $C_s(n+1)$  and  $C_t(n+1)$  and is simultaneously processed by the decision circuit *n* to generate the digital signal  $D_n$ . During phase 1 of the next

Fig. 3 Amplifier shared stage

clock interval,  $C_s(n+1)$ ,  $C_f(n+1)$ , and A1 combine to generate the analog residue  $V_{\text{RES}}(n+1)$  under the control of  $D_n$ . This is processed by the decision circuit n+1 to generate the digital output  $D_{n+1}$ .

Amplifier sharing introduces two possible drawbacks<sup>[4]</sup>. Firstly, the additional switches that are used to implement amplifier sharing introduce series resistances, which will affect the settling behavior of the stage. The switch resistances can be reduced by using large switches at the expense of a potential increase in offsets due to charge feed through. Secondly, the nonzero input voltage of the amplifier is never resetted. Thus, every input sample is affected by the finite-gain error components from the previous sample. However, increasing the gain of the opamp could make the finite gain error negligible.

Also, in order to reduce power consumption, the scaling technique for the opamps and capacitors is applied. The value of the sampling capacitor of the SHA,  $C_s$ , should be obtained from noise and matching constraints. In this design  $C_s$  is limited by matching rather than noise.

## 3 Circuit techniques

There are mainly two key techniques for the

ADC, i. e. low-power high-bandwidth gain-boosting opamp technique and low-power low-offset dynamic comparator technique.

# 3. 1 Low power high band width gain boosting opamp

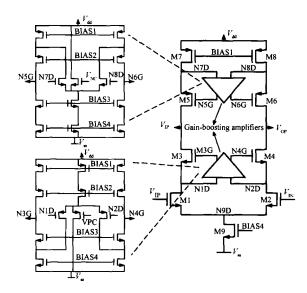

The amplifiers adopted in the SHA and other ADC stages are based on a fully differential gainboosting telescopic architecture (shown in Fig. 4) to get a high open-loop gain and excellent bandwidth with less power consumption, at the cost of a reduced signal swing range. In this implementation, the telescopic amplifier also exploits a wideswing gain-boosting technique in order to alleviate the problem of the reduced signal swing range. The gain-boosting technique improves the cascoding effect of a single MOS transistor by using local negative feedback.

Assume , for simplicity , that the two additional gain-boosting amplifiers have the same DC gain  $A_{add}$  , and the upper part of the circuit has the same output impedance as the lower part. Then the output impedance of the circuit is increased by the gain of the additional gain-stage  $A_{add}$ :

$$R_{\text{out}} = \frac{1}{2} \left( \left( g_{\text{m3}} r_{\text{o3}} \left( A_{\text{add}} + 1 \right) + 1 \right) r_{\text{o1}} + r_{\text{o3}} \right) \quad (2)$$

where  $g_{m3}$  is the transconductance of transistor

Fig. 4 Low-power high-bandwidth gain-boosting opamp

M3,  $r_{01}$  and  $r_{03}$  are the output resistance of transistors M1 and M3, respectively. Hence, the total DC-gain becomes

$$A_{o,tot} = \frac{1}{2} g_{m1} r_{o1} (g_{m3} r_{o3} (A_{add} + 1) + 1)$$

(3)

where  $g_{m1}$  is the transconductance of the transistor M1.

From Eq. (2) ,it can be seen that the gain-enhancement technique increases the output impedance by a factor approximately equal to  $A_{add} + 1$ . But the gain of the additional stage,  $A_{add}$  decreases for frequencies above the - 3dB bandwidth of the gain-boosting amplifier with a slope of - 20dB/ decade. For frequencies above unity-gain bandwidth of the gain-boosting amplifier,  $A_{add}$  is less than one, and the normal output impedance of a cascade stage without gain-enhancement remains. This could introduce a doublet in the plot of the total output impedance.

Non-complete doublet cancellation can seriously degrade the settling behaviour of an opamp. In order to overcome this drawback, the unity-gain frequency of the added gain boosting circuit should be higher than the - 3dB bandwidth of the circuit, which is the closed-loop bandwidth of an SC circuit which uses the main amplifier, and must be lower than the second-pole frequency of the main amplifier for reasons concerning stability. This way, the circuit could have a single-pole settling behavior. The gain-bandwidth product (GBW) could be expressed as

$$GBW = \frac{g_m}{C_{\text{load}}}$$

(4)

where  $g_m$  is the input transconductance and  $C_{load}$  is the load capacitor connected at the output of the amplifier. The amplifier also uses a switched-capacitor common-mode feedback circuit<sup>[6]</sup>, which is not shown in Fig. 4.

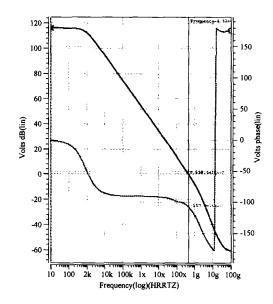

Figure 5 shows the simulated gain and phase of the gain-boosting opamp used in SHA. The main simulated characteristics of the opamp are summarized in Table 1.

Fig. 5 Simulated gain and phase of the gain boosting opamp

Table 1 Main characteristics of the opamp

| Characteristics     | Value  |

|---------------------|--------|

| DC gain             | 118dB  |

| Unity-gain freqency | 432MHz |

| Load capacitor      | 5p F   |

| Phase margin        | 73 °   |

| Power consume       | 18mW   |

| Output swing        | 2. 1V  |

| Supply voltage      | 3. 0V  |

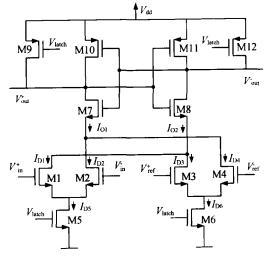

#### 3. 2 Dynamic comparator

As previously discussed the 1. 5bits/ stage architecture relaxes the requirements for comparator offsets. This allows the use of dynamic latch-type comparators without any preamplifier to cancel the offset voltage. In order to reduce power consumption ,a low offset dynamic comparator ,as shown in Fig. 6 ,is adopted in the ADC<sup>[7]</sup>.

Fig. 6 Dynamic comparator

The operation of the comparator can be briefly described as follows. When the latch signal  $V_{\text{latch}}$  is at 0V the comparator is inactive, transistors M5 and M6 are switched off and there is no current path between the supply voltages. The transistors M9 and M12 reset the outputs to  $V_{dd}$ . The transistors M7 and M8 of the latch conduct and pull the drains of the transistors M1 ~ M4 to  $V_{dd}$ , while the drain voltage of M5 and M6 are dependent on the comparator input voltages. When  $V_{\text{latch}}$  is raised to  $V_{dd}$ , the comparator is active, the outputs are disconnected from the supply  $V_{dd}$ , M5 and M6 turn on ,and M1 ~ M4 compare  $V_{\text{in}}^+$  –  $V_{\text{in}}^-$  with  $V_{\text{ref}}^+$  –  $V_{\text{ref}}^-$

The threshold voltage of the comparator is determined by the current division in the differential pairs and between the cross-coupled branches. The transistors M1 ~ M4 follow the large signal current equations  $(W_1 = W_2, W_3 = W_4)$ :

$$I_{\rm D1} - I_{\rm D2} = {}_{1}V_{\rm in} = \frac{2I_{\rm D5}}{N} - V_{\rm in}^{2}$$

(5)

$$I_{D4} - I_{D3} = {}_{3}V_{ref} = \frac{2I_{D6}}{\sqrt{3}} - V_{ref}^{2}$$

(6)

where

$$_{i} = \frac{1}{2} \mu C_{\text{ox}} \frac{W_{i}}{L}$$

,  $V_{\text{in}} = V_{\text{in}}^{+} - V_{\text{in}}$  and  $V_{\text{ref}} = V_{\text{ref}}^{+}$

-  $V_{\text{ref}}^{-}$ .

The comparator changes its stage when the currents  $I_{O1} = I_{D1} + I_{D3}$  and  $I_{O2} = I_{D2} + I_{D4}$  of both the output branches are equal. Assuming the relation of the source-coupled pair bias currents to be  $I_{D5} = dI_{D6}$ , and by marking the threshold point with a parameter *e* such that  $V_{in} = eV_{ref}$ , the resulting condition is thus

$$2 de^{2} I_{D6} \frac{W_{1}}{L} - \mu C_{ox} e^{4} V_{ref}^{2} \left( \frac{W_{1}}{L} \right)^{2} = 2 I_{D6} \frac{W_{3}}{L} - \mu C_{ox} V_{ref}^{2} \left( \frac{W_{3}}{L} \right)^{2}$$

(7)

The parameters d and e are chosen according to the desired trip point of the comparator. The total offset voltage of the comparator consists of the sum of the offsets of both source-coupled pairs. The offset of one differential pair has a well-known dependency on the mismatch of the threshold voltage  $V_{\rm T}$ , load resistance  $R_{\rm L}$  and transistor dimensions and their corresponding average values  $V_{\rm T}$ ,  $R_{\rm L}$ , and .

$$V_{\rm OS} = V_{\rm T} + \frac{V_{\rm gs} - V_{\rm T}}{2} \times \left(\frac{R_{\rm L}}{R_{\rm L}} + -\right) \qquad (8)$$

The offset voltage in this case is dominated by the mismatch of the transistor dimensions , while  $V_{gs} - V_T$  is set by the tail currents  $I_{D5}$  and  $I_{D6}$ . Simulation results show that the offset of this comparator is within 5mV, with a supply voltage range from 2. 6 ~ 3. 6V, a process range from slow to fast, and temperatures from low to high (-40 ~ 125), which is much lower than the traditional dynamic comparators in Ref. [9].

### 3. 3 Other components

The ADC also includes an on-chip precision bandgap reference voltage generator and buffer amplifiers to generate positive and negative reference voltage and the common-level voltage for opamps. The clock generation of the ADC is implemented with five local clock generators driven by a single master clock to coincide between stages in order to avoid any loss of clock period due to skews related to the layout.

## 4 Experimental results

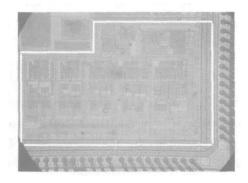

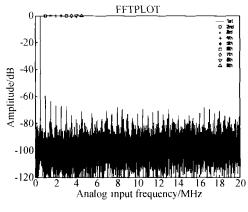

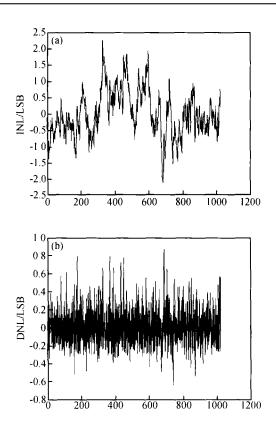

The ADC has been fabricated in a 0.  $25\mu$ m single-poly five-metal DGO CMOS process with an MiM capacitor. The die photograph is shown in Fig. 7. The upper side shows the bandgap and the reference buffer opamps, while the center side shows the SHA and the four opamp sharing blocks, and the bottom shows the digital error correction logic block. The total active area is about 1.  $24 \text{ mm}^2$ , with a core area, excluding the bandgap and buffer amplifiers, of about  $1 \text{ mm}^2$ . The measured output fast Fourier transform (FFT) spectrum with a 0. 5M Hz input frequency at 40MS/s is shown in Fig. 8. The measured nonlinearity of the ADC is shown in Fig. 9. The summary of the ADC is overall performance is given in Table 2.

Fig. 7 Die photograph

Fig. 8 Measured FFT spectrum

Fig. 9 Measured nonlinearity 40 Ms/s,  $f_{\text{in}} = 500 \text{ kHz}$

| Table 2Performance summary |                                                                       |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------|--|--|--|--|

| Resolution                 | 10bit                                                                 |  |  |  |  |

| Conversion rate            | 40MS/ s                                                               |  |  |  |  |

| Process                    | 0. 25µm single-poly five-metal DGO<br>CMOS process with MiM capacitor |  |  |  |  |

| Power supply               | 3.0V                                                                  |  |  |  |  |

| Total power                | 59mW @3.0V                                                            |  |  |  |  |

| SNR *                      | 51dB                                                                  |  |  |  |  |

| SFDR *                     | 59dB                                                                  |  |  |  |  |

| THD *                      | 57dB                                                                  |  |  |  |  |

| ENOB *                     | 8.1bit                                                                |  |  |  |  |

| Peak INL *                 | 2. 2L SB                                                              |  |  |  |  |

| Peak DNL *                 | 0.85LSB                                                               |  |  |  |  |

\* Measured at  $f_{in} = 0.5 \text{ MHz}$ ,  $f_{clk} = 40 \text{ MHz}$

## 5 Conclusion

A 10bit 40MS/s ADC has been described. By sharing an amplifier between two successive pipeline stages, significant power reduction has been achieved. The converter also employs high bandwidth low-power gain-boosting telescopic amplifiers and low power low offset dynamic comparators in order to save power and provide high performance. The ADC, which occupies 1. 24mm<sup>2</sup> and consumes only 59mW (including a bandgap and a reference circuit) at 40MS/s, has been implemented in a 0. 25µm DGO CMOS process technology.

When quantifying the power efficiency of the A/D converter implementations, the resolution and sample rate should also be considered. The most widely accepted measure of the effectiveness of design is the energy per conversion step<sup>[8]</sup>, defined as

$$E_{\rm conv} = \frac{P_{\rm D}}{2^N f_{\rm s}} \tag{9}$$

where  $P_{\rm b}$  is the power dissipation, N is the resolution and  $f_{\rm s}$  is the sample rate. Using the above equation power efficiency comparison with those reported in Refs. [1,3 ~ 5,9 ~ 12] is given in Table 3.

| T 11 0  | D      | CC: .          | •          |

|---------|--------|----------------|------------|

| Table 3 | Power  | etticiency     | comparison |

| rable 5 | 10 wei | criticitetic y | companson  |

|           | Resolution<br>/ bit | Sample rate<br>/ (Msample ·s <sup>-1</sup> ) | Power<br>dissipation<br>/ mW | Energy per<br>conversion step<br>/ pJ |

|-----------|---------------------|----------------------------------------------|------------------------------|---------------------------------------|

| This work | 10                  | 40                                           | 59                           | 1.4                                   |

| Ref. [1]  | 10                  | 40                                           | 65                           | 1.6                                   |

| Ref. [3]  | 13                  | 5                                            | 166                          | 4.1                                   |

| Ref. [4]  | 8                   | 52                                           | 250                          | 18.7                                  |

| Ref. [5]  | 10                  | 20                                           | 240                          | 11.7                                  |

| Ref. [9]  | 10                  | 20                                           | 65                           | 3.2                                   |

| Ref. [10] | 8                   | 200                                          | 177                          | 3.4                                   |

| Ref. [11] | 8                   | 125                                          | 71                           | 2.2                                   |

| Ref. [12] | 12                  | 20                                           | 254                          | 3.1                                   |

As can be seen from the table, the power efficiency of this work is much higher than those of Refs.  $[9 \sim 11]$  which are published state-of the art performances in domestic journals. Although the power efficiency of Ref. [1] is comparable with this work, it was implemented in a BiCMOS process, which is more suitable for high performance mixedsignal circuits than a CMOS process.

### References

- [1] Hoogzaad G, Roovers R. A 65mW 10b 40Msample/s BiC-MOS nyquist ADC in 0. 8mm<sup>2</sup>. IEEE J Solid-State Circuits, 1999,34(12):1796

- [2] Kwok P T F, Luong H C. Power optimization for pipeline analog-to-digital converters. IEEE Trans Circuits Syst ,1999, 46(5):549

- [3] Cline D W, Gray P R. A power optimized 13-b 5 Msamples/s pipelined analog-to-digital converter in 1. 2µm CMOS. IEEE J Solid-State Circuits ,1996 ,31 (3) :294

- [4] Nagaraj K, Fetterman H, Anidjar K, et al. A 250 mW, 8-b, 52-Msamples/s parallel-pipelined A/D converter with reduced number of amplifiers. IEEE J Solid State Circuits, 1997, 32

(3):312

- [5] Lewis S H. A 10-b 20Msample/s analog-to-digital converter. IEEE J Solid-State Circuits ,1992 ,27 (3) :351

- [6] Senderowicz D, Dreyer S F, Huggins J H, et al. A family of differential NMOS analog circuits for a PCM codec filter chip. IEEE J Solid-State Circuits, 1982, 17(6):1014

- [7] Sumanen L, Waltari M, Halonen K. A mismatch insensitive CMOS dynamic comparator for pipeline A/D converters. Proceedings of the IEEE International Conference on Circuits and Systems, 2000, 1:32

- [8] Sumanen L. Pipeline analog-to-digital converters for wideband wireless communications. Doctoral Thesis, Helsinki University of Technology, Espoo, 2002:23

- [9] Zhu Zhen, Ma Dequn, Ye Jinghua, et al. A full-differential CMOS pipelined A/D convertor. Chinese Journal of Semiconductors, 2004, 25(9):1175 (in Chinese) [朱臻,马德群,叶菁 华,等. 低功耗全差分流水线操作 CMOS A/D 转换器. 半导 体学报,2004,25(9):1175]

- [10] Chen Cheng, Wang Zhaogang, Ren Junyan, et al. 200Ms/s

177mW 8bit folding and interpolating CMOS A/D converter. Chinese Journal of Semiconductors ,2004 ,25 (11) :1391

- Wang Zhaogang ,Chen Cheng ,Ren Junyan ,et al. A 71mW 8b 125Msample/s A/D converter. Chinese Journal of Semiconductors ,2004 ,25(1) :6

- [12] Wang Xiaoyue, Hurst PJ, Lewis S H. A 12-bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration. IEEEJ Solid-State Circuits, 2004, 39(11): 1799

# 一个 59mW 10 位 40MHz 流水线 A/D 转换器\*

李 建' 严杰锋' 陈 俊' 张剑云' 郭亚炜' 沈 泊<sup>1,†</sup> 汤庭鳌'

(1复旦大学专用集成电路与系统国家重点实验室,上海 200433)(2上海微科集成电路有限公司,上海 200433)

摘要:设计了一个工作在 3.0V 的 10 位 40M Hz 流水线 A/D 转换器,采用了时分复用运算放大器,低功耗的增益 自举 telescopic 运放,低功耗动态比较器,器件尺寸逐级减小优化功耗.在 40M Hz 的采样时钟,0.5M Hz 的输入信 号的情况下测试,可获得 8.1 位有效精度,最大积分非线性为 2.2L SB,最大微分非线性为 0.85L SB,电路用 0.25µm CMOS 工艺实现,面积为 1.24mm<sup>2</sup>,功耗仅为 59mW,其中同时包括为 A/D 转换器提供基准电压和电流的 一个带隙基准源和缓冲电路.

关键词:模数转换器;低功耗;共享运算放大器技术

EEACC: 1265 H; 1280; 2570D

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2005)07-1301-08

<sup>\*</sup>上海市集成电路设计创新资助项目(批准号:047062008)

李 建 男,1980年出生,博士研究生,主要从事模数转换器的设计研究.

汤庭鳌 男,1939年出生,教授,博士生导师,主要从事集成电路工艺及设计研究.

沈 泊 男,1975年出生,博士,主要从事通信芯片设计研究.

<sup>+</sup> 本文通信作者, Email: boshen @fudan.edu.cn