# 数字射频存储器用 GaAs 超高速 3bit 相位 ADC 的设计与实现

#### 张有涛1,2 夏冠群1 李拂晓2 高建峰2 杨乃彬2

(1 中国科学院上海微系统与信息技术研究所,上海 200050) (2 南京电子器件研究所,南京 210016)

摘要:详细讨论、分析了用于 3bit 相位体制数字射频存储器 (DRFM) 系统的 3bit 相位体制 ADC 的设计、实现及测试. 利用南京电子器件研究所标准 GaAs 76mm 全离子注入工艺,采用全耗尽非自对准 MESFET 器件加工实现了 3bit 超高速相位体制 ADC.测试结果表明,该电路可在 2 GHz 时钟速率下完成采样、量化,达到 1. 2 Gbps 的输出码流速率,其瞬时带宽可达 150 MHz,具备 ±0. 22 LSB 的相位精度.

关键词:相位数字化;模数转换器;MESFET;比较器;数字射频存储器

**EEACC:** 2570A; 1265H; 7310Z

中图分类号: TN431. 1 文献标识码: A 文章编号: 0253-4177(2005)07-1424-04

#### 1 引言

数字射频存储器 (DRFM) 具有对射频和微波信号的存储及再现能力,已发展成为现代电子战系统和仪器测试系统的重要组成部分. 作为 DRFM 的核心部分,超高速 ADC,DAC 的性能直接决定了它处理模拟信号的能力. 但是,由于半导体工艺及器件性能的限制,高采样率、高分辨率的 ADC 及 DAC 难以实现. 由于相位数字化比传统的幅度数字化有多种优点,且采用相位量化可降低对上述电路的要求,所以含相位体制 ADC 及 DAC 的 DRFM 系统得到广泛应用[1~4]. 本文利用 GaAs MESFET 全离子注入非自对准常规工艺设计了用于 3bit 相位体制DRFM 系统的单片超高速相位体制 ADC.测试结果表明,电路可在 2 GHz 时钟速率下完成采样、量化,达到 1. 2 Gbps 的输出码流速率,其瞬时带宽可达150MHz,具备 ±0. 22LSB 的相位精度.

## 2 电路设计

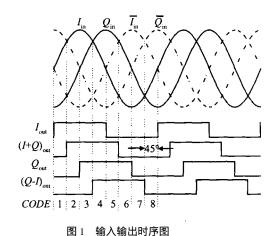

3bit 相位体制 ADC 的量化对象是输入信号的相位量,基本功能是将输入的两路正交模拟信号转换为四路含相位信息的数字信号.输出信号是占空

比为 1 1、频率与输入正交信号同频率的方波信号,但每相邻两路之间的相位差为 45 <sup>431</sup>. 3bit 相位体制 ADC 的输入输出时序关系及真值表分别如图 1、表 1 所示. 所以,3bit 相位体制 ADC 的输出信号每周期含 8 个相位态,电路的转换速率为输入模拟信号频率的 8 倍.

表 1 输出真值表

Table 1 Output true table

| CODE                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|----------------------|---|---|---|---|---|---|---|---|

| $I_{ m out}$         | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| $(I+Q)_{\text{out}}$ | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| Q <sub>out</sub>     | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| (Q - I) out          | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

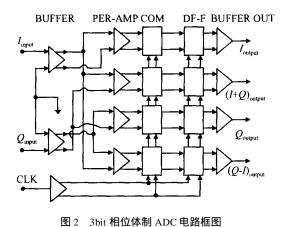

根据 3bit 相位体制 ADC 的工作原理,设计电路框图如图 2 所示.

3bit 相位体制 ADC 主要由五部分电路组成: (1)输入缓冲级. 本级电路将输入的单端模拟正交信号变换为 ADC 内部所需的互补信号,并具有一定的放大作用. 此外,该级电路还包括将外部的单端时钟信号变换为内部其他各级电路所需的互补时钟信号. (2)预放大级. 本级电路根据 3bit 相位量化的原

张有涛 男,1979年出生,博士研究生,主要研究方向为 CaAs 超高速集成电路.

夏冠群 男,1941年出生,研究员,主要研究领域为化合物半导体器件与电路.

李拂晓 男、1963年出生,研究员、主要研究领域为化合物半导体器件与 MMIC.

Fig. 1 Timing diagram

Fig. 2 3bit phase ADC block diagram

理对模拟正交信号及其互补信号按照一定规则两两组合,进行差分放大. (3) 比较级. 本级电路在时钟作用下,利用正反馈原理对比较器输入端的模拟信号进行取样、量化. (4) 触发锁存级. 本级电路在时钟的精确控制下,对前级比较级输出的量化数字值进行触发锁存. (5) 输出缓冲级. 目的是为了在高速数字传输时能足以驱动 ADC 后级的 50 负载. 电路设计时,已将输入、输出端口设计为片内 50 匹配,便干高速测试及应用.

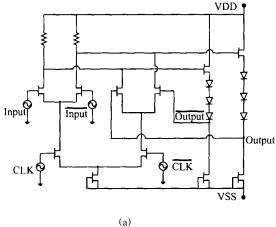

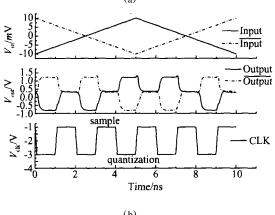

上述各级电路中,最为关键的部分是比较级电路.通过它将模拟信号采样、量化为数字信号,本级输出数字信号的质量将影响后级触发锁存级能否可靠工作.所以,它的性能直接决定了整个 ADC 电路的工作速度.为了获得高增益及良好的输入动态范围,采用栓锁再生比较器,利用其正反馈的工作原理达到高的采样、量化速度,且对小的输入信号仍然能够正确工作,为后级的触发锁存级提供足够的量化数字电平[5].栓锁再生比较器的电原理图如图 3(a)

所示. 图 3(b) 为其在  $20mV_{pp}$  输入信号、500MHz 时钟作用下的仿真工作特性.

图 3 (a) 栓锁再生比较器;(b) 比较器仿真结果

$\label{eq:Fig.3} Fig. 3 \quad \text{(a)} \ \ Regeneration \ comparator ; \ \text{(b)} \ \ Simulation \\ results \ of \ comparator \\$

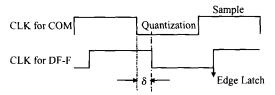

由图 3 可知,该比较器在时钟的高电平作用下 对外部输入信号进行取样,直至时钟的高电平结束. 这一过程中,比较器负载电阻端的电平及比较器的 输出端电平均跟随外部输入信号而变. 到达时钟的 下降沿时,比较器利用正反馈作用立刻将时钟高电 平最后时刻取样的外部信号进行量化,使比较器的 输出端强置于稳态的高、低电平. 因此,比较器的负 载电阻、输入取样对管的栅宽及正反馈量化对管的 栅宽都需要仔细设计,以达到高增益、高输出量化摆 幅. 比较器的后级采用下降沿 D 型触发器,利用与 比较器相同的时钟信号进行触发锁存. 为了对比较 器的量化输出稳态值进行可靠触发锁存,需要精细 设计整个 ADC 电路的时钟分布. 最终版图布局时 恰当安排各级版图位置,使到达触发锁存级的时钟 信号稍稍滞后于比较器级(如 ),即可用同一时钟 可靠同步整个 ADC 电路, 最终电路的具体时序安 排如图 4 所示.

图 4 ADC 各级电路时钟时序分布

Fig. 4 Clock distribution in stages of ADC

由于相位体制 ADC 的量化对象是信号的相位量,因此芯片版图设计时将片内互补时钟单元置于整个电路版图的中心,保证电路内部同一级 4 个通道的时钟信号边沿相差不大.此外,还要尽量保证各通道内部信号所走路径长度一致.

由于本电路最终将采用全离子注入非自对准常规工艺,而 ADC 又对器件的离散非常敏感,所以结合实际工艺情况,利用蒙特卡罗分析,计算了 ADC 电路对器件阈值电压离散的敏感度,进而分析电路的成品率.通过不断改进各级电路中器件的栅宽比例使得最终 ADC 电路在现有工艺水平下能够达到80%以上的成品率,至此电路设计完毕.

#### 3 工艺实现

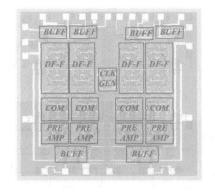

电路采用南京电子器件研究所标准 CaAs 76mm 全离子注入工艺实现,器件均为耗尽型器件,为非自对准常规工艺.工艺流程简介如下:N 有源区采用大面积 Si 离子注入形成,注入能量为 60keV,剂量为 4 3 ×10<sup>12</sup> cm<sup>-2</sup>;N<sup>+</sup>区采用 Si 离子选择双注入形成,注入能量分别为 120,60keV,剂量均为 3 ×10<sup>13</sup> cm<sup>-2</sup>;源漏欧姆接触金属采用 Au/ Ge/ Ni 金属系统,栅采用常规 Ti/ Pt/ Au 栅. 整个流程应用金属剥离工艺,电路用 Si<sub>3</sub> N<sub>4</sub> 介质实现两层金属布线隔离. 严格控制栅挖槽工艺,调整器件的阈值电压到目标电压-1. 3V. 最终得到的芯片实际照片如图 5 所示,芯片尺寸为 2mm ×2mm,各功能模块均以框图标示.

### 4 电路测试

设计测试专用的测试盒及高速 PCB 板,芯片直接装配到测试底座上,通过金丝键合至 PCB 上的传输线.由于电路本身含有驱动 50 负载的输出缓冲驱动电路,因此,测试过程中电路存在比较大的高速开关电流.为了保证在这种电流急速开关变化下的信号完整性,需要对所有的直流馈线交流旁路,旁路

图 5 3bit 相位体制 ADC 芯片照片 Fig. 5 Chip photo of GaAs 3bit phase ADC

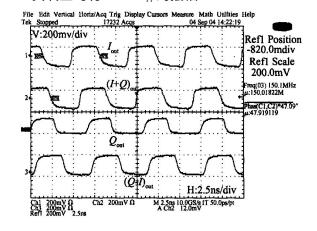

电容采用 1µf 和 100pf 的贴片电容,以此来稳定直流馈电的电压稳定.由于电路的量化对象是相位量,所以需要严格避免输入输出电缆给各通道所引入的额外相位误差.以每个通道输出信号经过各自高低电平的 50 %点为基准进行相位差统计.图 6 为高频150M Hz 输入模拟正交信号、2 GHz 时钟速率下的测试结果,ADC 的输出码流速率均为 1.2 Gbp s.由图可见,电路各通道的相位关系正确,输出幅度在50 负载上均有 180mVpp的摆幅.

图 6 150MHz 输入、2 GHz 时钟速率下的输出波形

Fig. 6 Output signal at 150MHz input signal and 2GHz clock

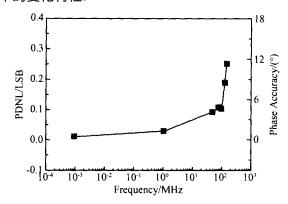

相位量化 ADC 最关键的参数是相位精度随工作频率的变化情况,它决定了 ADC 电路的瞬时工作带宽. 在某一频率 f 下,Pha(i) 代表实际第 i 个码元所对应的相位量,那么该频率下的相位精度 PA(f) 可表示为:

PA(f) = max(abs(Pha(i) - 45)) i = 1, 2, ..., 8

同传统的幅度 ADC,也可以用线性度随工作频率的变化描述电路的频域性能. 定义 PDNL(f)代

表该频率下的微分线性度,则:

$$PDNL(f) = PA(f)/45$$

图 7 是该电路的微分非线性误差及相位精度随 频率的变化特性.

图 7 PDNL 及相位精度的动态性能

Fig. 7 Dynamic performances of PDNL and phase accuracy

由图 7 测试结果可知,如果定义 10 相位误差(对 应 ±0. 22LSB) 为界,那么该电路具有接近 150MHz 的带宽,ADC的输出码流速率可达 1. 2 Gbps. 以上测 试结果均在 2GHz 时钟速率下测得.

#### 结论 5

本文详细讨论、分析了用于3bit相位体制

DRFM 系统的 3bit 相位体制 ADC 的设计过程. 利 用南京电子器件研究所标准 GaAs 76mm 全离子 注入工艺,采用全耗尽非自对准 MESFET 器件加 工实现了 3bit 超高速相位体制 ADC. 测试结果表 明,电路可在2GHz时钟速率下完成采样、量化,达 到 1. 2 Gbp s 的输出码流速率,其瞬时带宽可达 150M Hz, 具备 ±0. 22L SB 的相位精度. 经进一步改 进后可应用于 3bit 相位体制 DRFM 系统中.

#### 参考文献

- [1] Wordwworth GB, Clark DG. Gigahertz bandwidth multibit phase sampling and reconstruction of microwave signals. IEEE MTT-S Digest ,1986:371

- [2] William A W, Albert H T, Hisatshi S, et al. Design and application of a GaAs digital RF memory chip. IEEE J Solid-State Circuits, 1990, 25(4):961

- [3] Tho T V James M H. A GaAs phase digitizing and summing system for microwave signal storage. IEEE J Solid-State Circuits, 1989, 24(1):104

- [4] Pring P C J ,James G E , Hayes D ,et al. The phase performance of digital radio frequency memories (DRFMs). Proc 2nd Int Conf on Advanced A-D and D-A Conversion Techniques and Their Applications, 1994:18

- [5] Feng S, Seitzer D. Input voltage sensitivity of GaAs/ GaAlAs HEMT latched comparator. IEE Electronic Letters, 1992, 28 (3):233

### Design and Implementation of a High-Speed 3bit GaAs Phase ADC for DRFM

Zhang Youtao<sup>1,2</sup>, Xia Guanqun<sup>1</sup>, Li Fuxiao<sup>2</sup>, Gao Jianfeng<sup>2</sup> and Yang Naibin<sup>2</sup>

(1 Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China) (2 Nanjing Electronic Devices Institute, Nanjing 210016, China)

Abstract: The design and test process of a 3bit phase GaAs ADC for a 3bit phase digital radio frequency memory (DRFM) are described in detail . Using the Nanjing Electronic Devices Institute GaAs 76mm standard full ion-implanted process and 0. 5µm non-self-aligned D-mode MESFETs, a 3bit GaAs phase ADC is implemented. Test results indicate that the ADC can operate at a 2 GHz sampling rate with a 1. 2 Gbps output code rate. Its instantaneous bandwidth is nearly 150MHz with a phase accuracy of ±0. 22LSB.

Key words: phase digitizing; ADC; MESFET; comparator; DRFM

EEACC: 2570A; 1265H; 7310Z

Article ID: 0253-4177 (2005) 07-1424-04

Zhang Youtao male, was born in 1979, PhD candidate. His research interest is in GaAs VHSIC.

Xia Guanqun male, was born in 1941, professor. His research interests include GaAs devices and circuits.

Li Fuxiao male, was born in 1963, professor. His research interests include compound semiconductor devices and MMIC.