# Yield Modeling of Rectangular Defect Outline \*

Wang Junping and Hao Yue

(Key Laboratory of Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, Microelectronics Institute, Xidian University, Xi'an 710071, China)

**Abstract :** In integrated circuits ,the defects associated with photolithography are assumed to be in the shape of circular discs in order to perform the estimation of yield and fault analysis. However ,real defects exhibit a great variety of shapes. In this paper ,a novel yield model is presented and the critical area model of short circuit is correspondingly provided. In comparison with the circular model corrently available ,the new model takes the similarity shape to an original defect ,the two-dimensional distributional characteristic of defects ,the feature of a layout routing and the character of yield estimation into account. As for the aspect of prediction of yield ,the experimental results show that the new model may predict the yield caused by real defects more accurately than the circular model does. It is significant that the yield is accurately estimated and improved using the proposed model.

Key words:real defect;rectangular defect model;critical area;yield modelingEEACC:1130B;0240G;2220CCLC number:TN43Document code:AArticle ID:0253-4177 (2005) 08-1514-05

### 1 Introduction

Yield estimate can be used in production control, material management, timely product delivery and operations planning tools. It can be used to highlight designs that have much lower than expected yield, to determine the cost of new devices and their resource implications. It is also the focal point of the industry that evolves from production of standard products, such as the memories of the production of ASIC and SOC products. By the yield prediction, the measures, including changing layout shapes, designing rules and conditions for processes, are adopted to obtain the maximum yields for mature processes<sup>[1,2]</sup>. tant role in IC yields, and the design sensitivity to these physical elements has continued to increase in today 's nanometer technologies<sup>[3]</sup>. Among typical CMOS processes, it is one of the greatest loss factors of the yield that the defect causes the electrical faults. The modeling of real defect outlines that exhibit a great variety of defect shapes is usually modeled as circular<sup>[4~10]</sup>, which causes errors of critical area estimation<sup>[11~15]</sup>. This paper presents a rectangle model of describing real defects and gives emphasis to yield model studying based on the rectangular outlines of real defects. Some experiments are performed to verify the veracity of the new model.

#### 2 Rectangle model of a real defect

Physical defects have always played an impor-

For yield model studying ,it is necessary to be-

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2003AA1Z163)

Wang Junping female, was born in 1964, associate professor, PhD candidate. She is engaged in research on design for VLSI manufacturability and yield modeling.

Hao Yue male, was born in 1958, professor and adviser of PhD candidates. He is engaged in research on microelectronics and semiconductor devices.

Received 28 January 2005 , revised manuscript received 5 April 2005

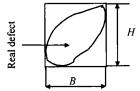

gin by considering the outline model of real defects. The results in Ref. [13] show that the rectangular model of the real defect has a more accurate estimation on critical areas associated a special layout than that of the circular defect model. The definition of a rectangular model of a defect is given as:for a real defect, the maximum possible extension of the real defect between two parallel straight lines, which corresponds to a horizontal routing direction of the special layout and touches the defect, is called the length (represented by the symbol H) of the real defect. The maximum possible extension of the real defect between two parallel straight lines, which corresponds to a vertical routing direction of the special layout and touches the defect, is called the width (represented by the symbol B) of the real defect, as can be seen in Fig. 1. Then we may define the rectangular model of real defect as a rectangle with H and B.

Fig. 1 Rectangular model of real defect

#### 3 New yield model

In general, based on the circular defect outlines, the Poisson yield model and the negative binomial model are often used to predict the yield loss from defects.

Poisson model

$$Y_{\rm F} = \prod_{i=1}^{M} e^{-A_i^{(c)}} D_i$$

(1)

Negative binomial model

$$Y_{\rm F} = \prod_{i=1}^{M} \left(1 + \frac{D_i A_i^{\rm (c)}}{i}\right)^{-i}$$

(2)

where  $Y_F$  denotes the yield ,which is the product of all layer yields ,and  $D_i$  is the defect density for layer *i*. The Poisson yield has been observed to give pessimistic yield predictions for large devices. In the better negative binomial model, *i* is the clustering parameter. Both in Poisson yield and in negative binomial model,  $A_i^{(c)}$ , the critical area related to a layout for layer *i* and  $A_i^{(c)}$ , can be written as

$$A_{i}^{(c)} = \prod_{R_{\min}}^{R_{\max}} A(R) h(R) dR$$

(3)

where A(R) is the critical area with diameter R, h(R) is the distribution of defect sizes,  $H_{\min}$  is the minimal diameter ,and  $R_{\max}$  is the maximal diameter based on the circular model.

According to the above rectangular defect outline model ,the critical area Eq. (3) ,which is caused by a rectangle defect and a layout associated with the *i* process ,now can be updated by

$$A_{i}^{(c)} = \prod_{H_{\min} B_{\min}}^{H_{\max} B_{\max}} A(H,B) h(H) b(B) dH dB (4)$$

where  $H_{\min}$  is the minimal length of the rectangle defect,  $H_{\max}$  is the maximal length,  $B_{\min}$  is the minimal width of the rectangle defect, and  $B_{\max}$  the maximal width, h(H) is the distributed function in length, that is,  $\frac{H_{\max}}{H_{\min}}h(H) = 1$ , and b(B) is the distributed function in width, that is,  $\frac{B_{\max}}{B_{\min}}b(B) = 1$ . Related to a defect with length H and width B, A(H,B) is the critical area , which is determined by the feature of layout routing and the model of a defect.

For mature processes, the distributed functions h(H) and b(B) are fixed and cannot be changed. Therefore, the key to Eq. (4) is to find A(H,B), which is determined commonly by the feature of layout routing and the defect model. It is well-known that IC interconnect was eventually going to be the dominate contributor to signal performance and that the largest contributor to yield loss is metal to metal shorted lines which can occur when a particle defect falls between two lines. The short critical area that is representative of a group as a whole is as follows.

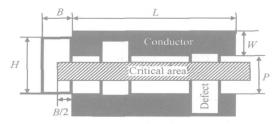

Now we assume that two metals are deposited on an insulator and have a length L which is much greater than its width  $W(L \gg W)$ . These metals have to allow an electric current to flow from one to the other. The failures in this case are short circuits caused by extra defects with a length H and a width B. The model of the critical area (see Fig. 2) is expressed as

$$A(H,B) = \begin{cases} 0, & 0 \quad H \quad P \\ (H - P)L + (H - P)B, \\ P < H \quad W + 2P \\ (P + W)L, \quad H > W + 2P \end{cases}$$

(5)

where L, W, and P are the length of metal lines, the width of metal lines, and the spacing between two metals, respectively. Based on the rectangular defect outlines, the new model of yield is composed of Eqs. (1), (4), and (5) or Eqs. (2), (4), and (5).

Fig. 2 Short critical area caused by rectangle defect outline

#### 4 Validity of the new model

In order to compare the new model developed in this paper with models currently available, real extra defects were collected using a test chip. The outlines of these defects are obtained by using the segmentation method of color image processing, which was presented in the author 's previous paper<sup>[13]</sup>. Based on these outlines, both the parameters H, B of the rectangular outline and the diameters of the circular outlines are respectively extracted. Using a routing unit similar to Fig. 2 (where the counts of metal lines are 32, that is, there are 32 metals on a routing unit , and  $W = 0.3 \mu m$  , P =0. 9 $\mu$ m,  $L = 56\mu$ m), the yields are obtained using the critical area models related to the rectangular outlines and circular outlines. On the same layout and real defects, the yield, as the comparative criterion, is obtained by the Monte-Carlo method. Comparison of the new yield value with the circular yield values is summarized in Table 1.

Table 1Yields caused by each defect model and realdefect

| Defect outline model         | Critical area<br>/ 10 <sup>-4</sup> cm <sup>2</sup> | Fault<br>probability | Yield  |

|------------------------------|-----------------------------------------------------|----------------------|--------|

| Minimal circle               | 1.6242                                              | 0.0151               | 0.9133 |

| Maximal circle               | 4.7363                                              | 0.0440               | 0.7677 |

| Real defect                  | 3.7457                                              | 0.0348               | 0.8114 |

| Mean circle                  | 3.3660                                              | 0.0313               | 0.8287 |

| Equivalent circle of ellipse | 1.9999                                              | 0.0186               | 0.8944 |

| Rectangle                    | 3.7625                                              | 0.0350               | 0.8106 |

Table 1 shows that the yields ,which are estimated by the model of maximal circle ,minimal circle ,real outline , mean circle ,equivalent circle , and rectangle outline , are 0. 9133 , 0. 7677 , 0. 8114 , 0. 8287 ,0. 894 ,and 0. 8106 ,respectively. From Table 1 ,it can be seen that a yield of 0. 8106 ,caused by the rectangular model , is nearest to the true yield of 0. 8114 caused by real defect outline.

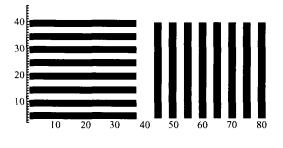

To verify the new model ,another experiments results are given. We assume a  $1/x^3$  defect size distribution and a random distribution of defect in length and width. By the features of the real layout (see Fig. 3) ,we obtain different sizes and different shapes defect with 9 ,whose maximum circular di-

Fig. 3 Metal array layout (line width 2.5µm, line length 36µm, line spacing 2.5µm)

ameters are ,2. 5,3,4,5, and 7. 9 $\mu$ m, respectively. Correspondingly, each probabilities distribution  $P_{D1}$ and  $P_{D5}$  are severally 0. 11,  $P_{D2}$  is 0. 22,  $P_{D3}$  is 0. 33, and  $P_{D4}$  is 0. 22. For the real defects, minimal circle diameter, mean circle diameter, equivalent circle diameter, rectangle outline and fault probability are calculated, as seen in Table 2. From Table 2, it can be proved that the fault probability 0. 2129 caused by the rectangular model is nearest to the true fault probability 0. 2089 caused by real defect outline. That is, the yield caused by the rectangular model is nearest to the true yield caused by real defect outline.

| Table 2  | Fault probability caused by each defect model |

|----------|-----------------------------------------------|

| and real | lefect                                        |

| Fault<br>probability | S <sub>m1</sub> (1) | S <sub>m2</sub> (2) | S <sub>m3</sub> (3) | S <sub>m4</sub> (2) | S <sub>m5</sub> (1) | Average<br>value with<br>weight |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------------------|

| Mean circle          | 0                   | 0                   | 0.0625              | 0.3125              | 1.0                 | 0.2014                          |

| Maximal circle       | 0                   | 0.0625              | 0.25                | 0.4375              | 1.0                 | 0.2986                          |

| Minimal circle       | 0                   | 0                   | 0                   | 0.1667              | 1.0                 | 0.1482                          |

| Equivalent circle    | 0                   | 0                   | 0                   | 0.2708              | 1.0                 | 0.1713                          |

| Rectangle            | 0                   | 0.0431              | 0                   | 0.4098              | 1.0                 | 0.2129                          |

| Real defect          | 0                   | 0.0418              | 0                   | 0.3982              | 1.0                 | 0.2089                          |

### 5 Conclusion

The rectangular model for predicting IC yield is presented and confirmed by our experiment results. The comparison presented for the routing layout shows that the new model can be used to estimate yield more accurately than the existing yield model. This approach can have a significant impact on the estimation and improvement of IC yields.

#### References

- [1] http://www.eetimes.com/news/latest/show Article.jhtml ? article IE = 18311057

- [2] Jing Ming 'e, Hao Yue. A geometry explanation of center of gravity algorithm of VLSI parametric yield. Chinese Journal of Semiconductors, 2004, 25(5):594(in Chinese)[荆明娥,郝 跃. VLSI成品率重心游移算法的一个几何解释. 半导体学报, 2004, 25(5):594]

- [3] Goel H, Dance D. Yield enhancement challenges for 90nm and beyond. Advanced Semiconductor Manufacturing Conference and Workshop ,2003:262

- [4] Wang Junping , Hao Yue. Segmentation of IC real defect color

images based on an LS space. Acta Electronica Sinica, 2005, 33(5):954(in Chinese)[王俊平,郝跃.基于LS空间的 IC 真 实缺陷图像的分割. 电子学报, 2005, 33(5):954]

- [5] Jiang Xiaohong, Hao Yue. Equivalent circular defect model of real defect outlines in the IC manufacturing process. IEEE Trans Semicond Manuf, 1998, 11(3):432

- [6] Papadopoulou E. Critical area computation for missing material defects in VLSI circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2001, 20 (5):583

- [7] De Vries D K, Simon P L C. Calibration of open interconnect yield models. 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 2003:26

- [8] Allan G A, Walton A J. Efficient extra material critical area algorithms. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 1999, 18(10):1480

- [9] Maly W. Computer aided design for VLSI circuit manufacturability. Proc IEEE, 1990:356

- [10] Allan G A. Targeted layout modifications for semiconductor yield/reliability enhancement. IEEE Trans Semicond Manuf, 2004,17(4):573

- [11] Ma Peijun, Hao Yue, Liu Hongxia. Analysis and simulation of effect of pinhole defects on integrated circuits functional yield. Chinese Journal of Semiconductors, 2001, 22(1):102(in Chinese)[马佩军,郝跃,刘红侠. 针孔缺陷对集成电路功能成 品率影响分析与仿真. 半导体学报, 2001, 22(1):102]

- [12] Zhao Tianxu, Hao Yue, Ma Peijun. An effectual IC 's yield estimation model. Chinese Journal of Semiconductors, 2002, 23

(2):198(in Chinese) [赵天绪, 郝跃, 马佩军. 一种有效的 IC 成品率估算模型. 半导体学报, 2002, 23(2):198]

- [13] Wang Junping , Hao Yue. Yield modeling based on circular defect size and a real defect rectangular degree. ICSICT Proceedings ,2004 :1104

- [14] Wang Junping, Hao Yue. Yield modeling of IC based on distribution of defect shapes. Chinese Journal of Semiconductors, 2005, 26(5):1054(in Chinese)[王俊平,郝跃.考虑缺陷形状 分布的 IC 成品率模型.半导体学报,2005,26(5):1054]

- [15] Wang Yang, Cai Yici, Shi Rui, et al. An algorithm for yield driven correction of layout. Chinese Journal of Semiconductors, 2004, 25(3):351(in Chinese)[王,蔡懿慈,石蕊,等.成 品率驱动下基于模型的掩模版优化算法.半导体学报,2004, 25(3):351]

## 矩形缺陷轮廓的成品率模型\*

#### 王俊平 郝 跃

(西安电子科技大学微电子学院 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

摘要:现有成品率及关键面积估计模型中,假定缺陷轮廓为圆,而实际缺陷轮廓为非规则形状.本文提出了矩形缺 陷轮廓的成品率模型,该模型与圆模型相比,考虑了缺陷的二维分布特性,接近真实缺陷形状及 IC 版图布线和成 品率估计的特点.比较了新模型与真实缺陷及其圆模型引起的成品率损失,表明新模型在成品率估计方面更加精确,这对成品率精确估计与提高有重要意义.

关键词:真实缺陷;矩形缺陷模型;关键面积;成品率模型

EEACC:1130B;0240G;2220C

中图分类号:TN43 文献标识码:A 文章编号:0253-4177(2005)08-1514-05

郝 跃 男,1958 年出生,教授,博士生导师,主要从事微电子学与半导体器件的研究. Email : yhao @xidian. edu. cn

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2003AA1Z1630)

王俊平 女,1964 年出生,副教授,博士研究生,主要从事集成电路可制造性设计与集成电路成品率模型. Email:jpwang @mail.xidian.edu. cn