# Design and Fabrication of a High-Voltage nMOS Device \*

Li Hua, Song Limei, Du Huan, and Han Zhengsheng

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract :** High-voltage nMOS devices are fabricated successfully and the key technology parameters of the process are optimized by TCAD software. Experiment results show that the device 's breakdown voltage is 114V, the threshold voltage and maximum driven ability are 1. 02V and 7. 5mA(W/L = 50), respectively. Experimental results and simulation ones are compared carefully and a way to improve the breakdown performance is proposed.

Key words: high-voltage nMOS devices; simulation; fabricationEEACC: 2560RCLC number: TN303Document code: AArticle ID: 0253-4177 (2005) 08-1489-06

### 1 Introduction

High-voltage semiconductor devices have been used in a wide range of applications, such as drivers, actuators, regulators and so on; the devices are also used in switching devices with extremely low voltage drops at on-state, low leakage current at off-state, and fast switching times<sup>[1,2]</sup>. In order to achieve higher reliability and lower manufacturing cost, there has been growing interest in developing high-voltage devices that can be integrated in lowvoltage CMOS circuits<sup>[3]</sup>. The method of integration provides an excellent way of achieving both high voltage and low voltage functions on the same chip; it reduces the cost of fabrication and reliability of circuit.

This paper presents a feasible method to fabricate high-voltage nMOS devices (HV-nMOS) based on 0. 8µm CMOS process. The device can be used in high-voltage integrated circuits such as driver ICs for FED<sup>[4]</sup>.

### **2** Device simulation

#### 2.1 Device structure

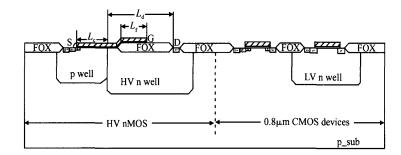

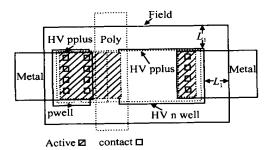

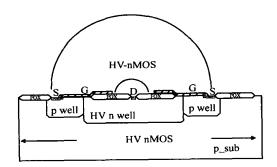

Figure 1 shows the schematic cross-section of an HV-nMOS structure using bulk silicon p-substrate. The high-voltage nMOS device is lateral double-diffusion MOSFET (LDMOS), which can be fabricated in the standard CMOS process by means of adding extra masks and process steps.

As we can see from Fig. 1,  $L_d$  is the length of the drift region of HV-nMOS, and its lengthening can lead to the increase of breakdown voltage of HV-nMOS<sup>[5]</sup>.  $L_f$  is the length of the field plate, which can improve the breakdown voltage of HVnMOS by reducing the surface electrical field<sup>[6]</sup>.  $L_c$ is the channel length of HV-nMOS, which determined by the lateral diffusion of the p well and HV n well.

<sup>\*</sup> Project supported by the State Key Development Program for Basic Research of China (No. 2003CB314705)

Li Hua male ,was born in 1981 ,master candidate. He is interested in research on semiconductor devices and VLSI technologies. Received 19 January 2005 ,revised manuscript received 14 April 2005 Chinese Institute of Electronics

Fig. 1 Schematic cross-section of high-voltage nMOS device

#### 2.2 Technology calibration

The HV n well is the drift region of HVnMOS. The phosphorus in an HV n well can affect a device 's breakdown voltage. The p well is the channel region of HV-nMOS, which can affect the threshold voltage and output current of the device. Thus, the technology parameters to form wells should be carefully designed by TCAD software<sup>[8]</sup>. In order to guarantee the validity of simulation results, the experiments to fabricate an n well and p well have been designed before the simulation. From Table 1 and Table 2, we can see that the simulation results using default coefficients cannot match the experiment results. In order to make the simulated results more creditable, it is necessary to calibrate the coefficients of TSUPREM- $4^{[8]}$ . DIX. 0 and DIP. 0 represent the impurity diffusion coefficient of phosphorus and born in Si and SEG. 0 represents the segregation coefficient of born between silicon and SiO<sub>2</sub><sup>[8]</sup>. Table 3 is the experimental and simulated results of an HV n well with calibrated coefficients.

| Table 1 | Results of | experiment 1 |

|---------|------------|--------------|

|---------|------------|--------------|

| n well                                          | $R_{\rm s}/({\rm k} \cdot {\rm r}^{-1})$ | $X_{\rm j}/\mu{ m m}$ | Coefficient in TSUPREM-4       |

|-------------------------------------------------|------------------------------------------|-----------------------|--------------------------------|

| Experimental results of experiment 1            | 2                                        | 5.3                   |                                |

| Simulated results using default coefficients    | 2.2                                      | 6.27                  | DIX. $0 = 2.31 \times 10^{10}$ |

| Simulated results using calibrated coefficients | 2                                        | 5.4                   | DIX. $0 = 1.3 \times 10^{10}$  |

| p well                                          | $R_{\rm s}/({\rm k} \cdot {\rm r}^{-1})$ | $X_{\rm j}/\mu{ m m}$ | Coefficient in TSUPREM-4                                       |  |  |

|-------------------------------------------------|------------------------------------------|-----------------------|----------------------------------------------------------------|--|--|

| Experimental results of experiment 2            | 3.8                                      | 4.81                  |                                                                |  |  |

| Simulated results using default coefficients    | 2.7                                      | 5.58                  | SEG. $0 = 1.13 \times 10^{3}$<br>DIP. $0 = 4.10 \times 10^{9}$ |  |  |

| Simulated results using calibrated coefficients | 3.7                                      | 4.83                  | SEG. $0 = 5 \times 10^2$<br>DIP. $0 = 3 \times 10^9$           |  |  |

| fuble 5 billiouted and measurement results of fiven wen | Table 3 | Simulated and | measurement | results of | HV | n well |

|---------------------------------------------------------|---------|---------------|-------------|------------|----|--------|

|---------------------------------------------------------|---------|---------------|-------------|------------|----|--------|

| Parameter   | $X_{j}/\mu m$ | $R_{\rm s}/(\cdot \cdot 1)$ | Thickness of SiO <sub>2</sub> after anealling/ nm |

|-------------|---------------|-----------------------------|---------------------------------------------------|

| Simulation  | 3.3           | 4910                        | 378                                               |

| Measurement | 3.34          | 4829                        | 362.8                                             |

#### 2.3 Device simulation

In this paper, the structural parameters of the

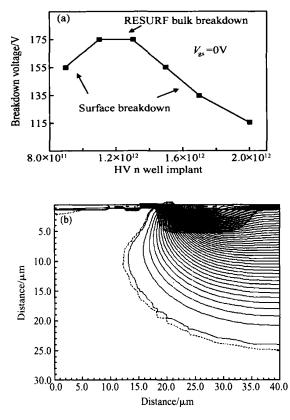

HV-nMOS are:  $L_d = 9.5 \mu m$ ,  $L_f = 7.5 \mu m$ ,  $L_c$  varies from 1. 5 $\mu m$  to 3 $\mu m$  with the increase of 0.5 $\mu m$ . MEDICI<sup>[8]</sup> is used to simulate the breakdown characteristic of HV-nMOS ( $L_c = 2\mu m$ ). At low phosphorus doses, simulation result indicates surface breakdown around the n<sup>+</sup> drain region. As the implant dose increases to 1. 3 ×10<sup>12</sup>, a maximum bulk RESURF breakdown voltage is achieved; further increasing the implant dose leads to loss of RE-SURF action and decrease of breakdown voltage<sup>[7]</sup>. The RESURF technique is based on the total depletion of the HV n well region leading to a spreading of equipotential lines, just as Fig. 2 shows.

Fig. 2 MEDICI simulation results (a) Breakdown voltage versus HV n well doping; (b) Equipotential contours of HV-nMOS ( $V_{gs} = 0V$ ,  $V_{ds} = 170V$ )

## **3 HV-nMOS fabrication**

The HV-nMOS is fabricated based on 0.8µm standard CMOS process in IMECAS (Institute of Microelectronics, Chinese Academy of Sciences). The following is the key process flows.

- (1) BS p-substrate;

- (2) Phosphorus implantation for HV n well;

(3) Boron implantation for p well;

(4) Annealing process to form HV n well and p well;

(5) Field implantation and LOCOS formation;

(6) Channel doping for HV-nMOS;

(7) Channel doping for low-voltage CMOS devices;

(8) Gate oxide formation;

(9) Gate formation;

(10) S/D formation;

(11) Contact and metallization.

The steps of  $(2 \sim 4, 6)$  are the extra steps to form HV-nMOS while the other steps are the standard CMOS process. In order to be compatible with standard CMOS process, the thickness of the gate oxide is 15nm and the formation of the two wells is assigned at the beginning of the whole process, thus the high-voltage process cannot affect the performance of low-voltage CMOS devices.

#### 4 Results and discussion

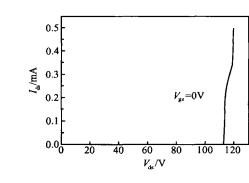

The experimental results show that the maximum driven ability and threshold voltage of HV-nMOS ( $W/L = 100\mu m/2\mu m$ ) are 7.5mA and 1.02V, respectively; the breakdown voltage of the device is 114V when  $V_{gs} = 0V$ . Table 4 is the comparison with related work<sup>[9]</sup>.

| <b>1</b>               |               |                 |     |                            |  |  |

|------------------------|---------------|-----------------|-----|----------------------------|--|--|

|                        | Breakdown     | Output          |     |                            |  |  |

| Device                 | voltage       | current         | W/L | $I_{ m ds}/L$              |  |  |

|                        | $(V_{gs}=0V)$ | $(V_{gs} = 5V)$ |     |                            |  |  |

| HV nMOS                | 114V          | 7.5mA           | 50  | 7.5 ×10 <sup>-5</sup> A/µm |  |  |

| HV nMOS <sup>[9]</sup> | 100V          | 7mA             | 90  | 5.2 ×10 <sup>-5</sup> A/µm |  |  |

Table 4 Electrical parameters of devices

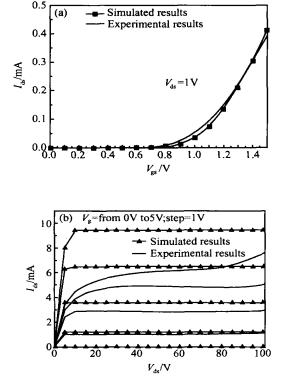

The comparison between simulated results and experimental results are shown in Fig. 3. The simulated threshold voltage and experimental threshold voltage are 0. 84V and 1. 02V (Fig. 3(a)). However, we can see that the deviation between simulated results and experimental results of output characteristics becomes obvious as  $V_{gs}$  increases, just as Fig. 3(b) shows.

In device simulation, we do not take the interface states between silicon and silicon dioxide into account. In fact, the Coulomb scattering mechanism of the interface states and fixed oxide charges is the dominant scattering mechanism as  $V_{gs}$  increases. The dependence of mobility on the gate field can be described by an empirical relationship of the following form :

$$\mu_s \ = \ \mu_0 \ ( \tfrac{0}{_{eff}} )$$

where  $\mu_0$  is the maximum extracted value of the mobility at a given doping concentration and is an empirical constant. An increase of  $V_{gs}$  can lead to an increase in <sub>eff</sub>, which causes carriers to be drawn closer to the interface, thus increasing surface scattering, and hence lower mobility<sup>[10]</sup>.

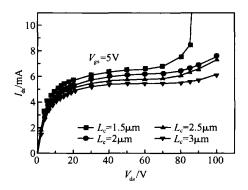

en ability. However, the short channel length may lead to the reduction of soft breakdown voltage because of punch-through: the breakdown voltage of HV-nMOS ( $L_c = 1.5\mu$ m) is just 85V when  $V_{gs} =$ 5V. On the other hand, the driven ability of the device is determined by two important factors: the length of drift region ( $L_d$ ) and channel ( $L_c$ )<sup>[5]</sup>. Thus, the increase of  $L_c$  cannot lead to the rapid decrease of driven ability. The experimental results show that the output current only decreases about 15 % when  $L_c$  increases from 1. 5µm to 2µm (Fig. 5); therefore, we can conclude that the channel length of HV-nMOS should be designed as 2µm in order to maintain the breakdown voltage of HVnMOS and get an acceptable output current.

Fig. 4 Breakdown voltage of HV-nMOS devices

Fig. 5 Output characteristics of different channel

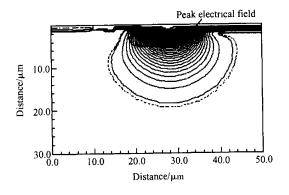

Figure 2 shows that the optimal breakdown voltage of HV-NMOS devices is 170V, but the experimental result is still 114V. The reason for the discord is the effect of field implantation. In order to avoid parasitic MOSFETs between adjacent devices, field implants should be done before LOCOS

Fig. 3 Simulated results versus experimental results (a)  $I_{ds}$ - $V_{gs}$  characteristics; (b) Output characteristics

The output characteristics of different devices are compared in Fig. 5; the channel lengths of four devices are 1. 5, 2, 2. 5, and  $3\mu$ m, respectively. From Fig. 5 we can see that the decrease of channel length can lead to the increase of the device 's drivprocess; according to layout design rules of 0. 8µm CMOS process, the distance of a field layer spaces well layer or active layer  $(L_1)$  is  $3\mu$ m, just as Fig. 6 shows. Figure 7 is the breakdown potential contours of HV-nMOS when  $V_{gs} = 0V$ ,  $V_{ds} = 140V$ . The simulated results of MEDICI show that the position of the peak electrical field is (34.75µm, 1. 456µm) and the weak point of breakdown is the p-n junction between the field implant region and the drift region of an HV-nMOS. In order to improve the breakdown performance of an HVnMOS, self-enclosed structure of the device can be adopted. Figure 8 shows the cross-section of it. We can see that the drain of HV-nMOS is surrounded by the regions of source and gate, so the breakdown between the field implant region and drift region can be avoided.

Fig. 6 Layout of HV-nMOS

Fig. 7 Equipotential contours of HV-nMOS  $V_{gs} = 0V$ ,  $V_{ds} = 140V$ ,  $L_1 = 3\mu m$

## 5 Conclusion

In this paper ,an HV-nMOS has been successfully integrated with standard 0.8µm CMOS

Fig. 8 Self-enclosed HV-nMOS

process. Process steps are given in detail after simulation and optimization by TSUPREM-4 and MEDICI. The HV-nMOS has been fabricated in IMECAS and the device exhibits excellent DC characteristics and acceptable breakdown performance. A way to improve the breakdown performance of the device is proposed. The process and the structure of an HV-nMOS are feasible for highvoltage applications.

#### References

- Hussein Ballan, Michel Declercq. High voltage devices and circuits in standard CMOS technologies. Kluwer Academy Publisher, 1999:1

- [2] Baliga B J. The future of power semiconductor device technology. Proceeding of the IEEE,2001,89(6):822

- [3] Liu Kuiwei, Han Zhengsheng, Qian He. Design and simulation of high-voltage CMOS devices compatible with standard CMOS technologies. Chinese Journal of Semiconductors, 2003,24(7):758(in Chinese)[刘奎伟,韩郑生,钱鹤,等. 兼容 标准 CMOS 工艺的高压器件设计与模拟. 半导体学报,2003, 24(7):758]

- [4] Kim J, Park M Y, Kang J Y, et al. Integration of 5-V CMOS and high voltage devices for display driver applications. ETRI Journal, 1998, 20(1):37

- [5] Moncoqut D, Farenc D, Rossel P, et al. LDMOS transistor for smart power circuits:modeling and design. IEEE, 1996

- [6] He Jin, Zhang Xing, Huang Ru, et al. 2-dimensional analysis of surface electrical field profile of planar junction with single-step field-plate termination structure. Chinese Journal of Semiconductors, 2001, 22(7):916(in Chinese)[何进,张兴,黄如,等.平面结场板结构表面场分布的二维解析.半导体学报,2001,22(7):916]

- [7] He Jin, Zhang Xing. Analytical model of surface field distribution and breakdown voltage for RESURF LDMOS transistor.

Chinese Journal of Semiconductors ,2001 ,22(9) :1102

- [8] TCAD manual. TSUPREM-4 Version 6.6. MEDICI Version4.1

- [9] Sun Weifeng, Wu Jianhui, Lu Shengli, et al. High-voltage power integrated circuit technology using bulk-silicon for plasma display panels data driver IC. Microelectronics Engi-

neering ,2004 ,71:112

[10] Arora N. MOSFET models for VLSI circuit simulation ----theory and practice. Zhang Xing ,Li Yingxue ,trans. Beijing : Science Press, 1999: 277 (in Chinese) [N. 艾罗拉, 著. 用于 VLSI 模拟的小尺寸 MOS 器件模型 ——理论与实践. 张兴, 李映雪,等译.北京:科学出版社,1999:277]

# 高压 nMOS 器件的设计与研制<sup>\*</sup>

李 桦 宋李梅 杜 寰 韩郑生

(中国科学院微电子研究所,北京 100029)

摘要:根据 TCAD 软件模拟的最优工艺条件成功研制了高压 nMOS 器件.测试结果表明器件的击穿电压为 114V, 阈值电压和最大驱动能力分别为 1. 02V 和 7. 5mA(W/L=50). 详细比较了器件的模拟结果和测试数据 ,并且提出 了一种改善其击穿性能的方法.

关键词: 高压 nMOS 器件; 模拟; 制造 **EEACC:** 2560R **中图分类号**: TN303 **文献标识码**: A 文章编号: 0253-4177(2005)08-1489-06

<sup>\*</sup>国家重点基础研究发展计划资助项目(批准号:2003CB314705)

李 桦 男,1981年出生,硕士研究生,研究兴趣为半导体器件和超大规模集成电路工艺. 2005-01-19 收到,2005-04-14 定稿