Vol. 26 No. 9 Sep., 2005

## LDMOS 的局部电热效应分析 \*

### 李梅芝 韦光萍 陈星弼

(电子科技大学微电子与固体电子学院,成都 610054)

摘要:分析了LDMOS(lateral DMOS)在一次雪崩击穿后的局部电热效应.提出并证明了等温分析和电热分析分别得到的LDMOS的触发点是不同的;分析了局部晶格温度在空间上的分布特点;并提出晶格温度弛豫时间会影响漏极电压弛豫时间.从而证明LDMOS工作于 ESD(electro-static discharge)保护的大电流区时,电热分析比等温分析的模拟结果与实验结果符合得更好.

关键词: 等温; 电热; 触发点; ESD; 晶格温度

**EEACC:** 2560R

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177 (2005) 09-1823-06

### 1 前言

LDMOS 在智能功率集成电路(smart power integrated circuit, SPIC) 输出级中的应用越来越广 泛,尤其在高性能汽车专用集成电路(application specific integrated circuits, ASICs) 中,用 40V-LD-MOS 做输出级的电路非常普遍[1~3]. 正常情况下, LDMOS 工作在线性区或饱和区:异常的 ESD 脉冲 来临时,LDMOS工作在一次雪崩击穿后的大电流 区,此时LDMOS 自身有一定的静电放电能力,故 LDMOS 是自保护器件. LDMOS 的 ESD 能力是汽 车电子可靠性的重要指标之一[4]. 栅极保护[5]、几何 图形[6]、器件结构[7] 等因素都会影响 LDMOS 的 ESD 能力. 文献[8,9]建立了 LDMOS 在 ESD 保护 时的模型,并对器件内部的物理机理作了详细分析. 由于LDMOS 在大电流区有电热效应,为减少设计 周期,节约成本,在预测和优化 LDMOS 自身的 ESD 能力时,对器件进行电热分析是必要的[4]. 文 献[10]分析了大电流区LDMOS器件单元之间的电 热特性,总结了器件电热分析方面的进展,但是,目 前还没有发现对比等温(晶格温度固定在300 K,晶 格温度固定,不随空间和时间变化,下同)分析和电热(晶格温度随空间和时间变化,下同)分析来对 LD-MOS 详细地进行电热效应分析的文献资料.

本文以栅接地的 40V-LDMOS 为例,用 2D-MEDICI<sup>[11]</sup>分别进行等温模拟和电热模拟,研究了LDMOS 的局部电热效应.提出并证明等温分析和电热分析分别得到的 LDMOS 的触发点是不同的;随后分析晶格温度在空间上的分布特点和晶格温度弛豫时间对漏极电压弛豫时间的影响,证明了 LD-MOS 工作于 ESD 保护的大电流区时,电热模拟的结果与实验结果符合得更好.

### 2 栅接地 40 V-LDMOS 的结构、模拟 结果及分析

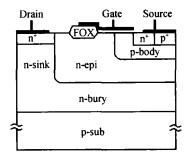

如图 1 所示,该器件是普通 SPIC 中的 LD-MOS,其漂移区由 n-epi 构成,表面漏极通过重掺杂的 n-sink 和埋层 n-bury 连通,沟道由双扩散形成,p-body 通过欧姆接触 p<sup>+</sup>和源 n<sup>+</sup>短接.该器件有一个寄生 npn 晶体管.当 p-body 和源极的 n<sup>+</sup>正偏时,该 npn 管触发导通,此时源极是发射极,p-body 是基区,漏极则是集电极.npn 管触发导通后,在负阻

<sup>\*</sup>国家自然科学基金资助项目(批准号:60476036)

李梅芝 女,1978年出生,博士研究生,目前研究方向为功率器件及功率 IC.

韦光萍 女,1979年出生,硕士研究生,目前研究方向为智能功率 IC.

陈星弼 男,1931 年出生,中国科学院院士,目前研究方向为功率器件及功率 IC.

区发生折回,进入 ESD 保护中的大电流区.

图 1 栅接地的 40V-LDMOS 结构示意图

Fig. 1 Cross-section indicating structrue of gategrounded 40V-LDMOS

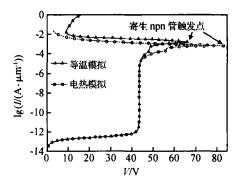

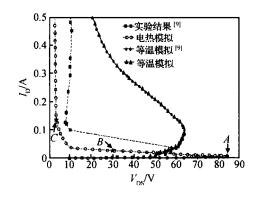

当栅源短接时,该器件相当于一个反向  $p^+$  nn<sup>+</sup> 二极管,其 FV 特性曲线与反向  $p^+$  nn<sup>+</sup> 二极管的 FV 特性曲线<sup>[4]</sup>相似,如图 2 所示. 由图可知等温模拟和电热模拟的 FV 特性曲线有基本相同的一次雪崩击穿,但是在一次雪崩击穿(电流大于  $10^{-5}$  A/ $\mu$ m)后,图中的两条 FV 特性曲线有两个很大的差别.

图 2 电热模拟和等温模拟的 FV 特性曲线

Fig. 2  $\ \ FV$  curves of non-isothermal and isothermal methods

- (1) 电热模拟的电流较小,是由晶格温度升高引起的. 晶格温度升高后,雪崩电离产生率下降,击穿产生电流逐渐减小,热产生电流逐渐增加,同时器件中有电流丝产生[2,4,10]. 另一方面,载流子的迁移率随晶格温度的增加而指数减小,使电阻率增大[2,12]. 这些结果都造成了一次雪崩击穿后,电热模拟的电流比等温模拟的电流小.

- (2)图 2 中两条 *FV* 特性曲线有不同的触发点,原因如下:

寄生 npn 管触发的条件是 p-body 和源极的  $n^+$  正偏且压降达到自建势  $V_{BPon}$ . 设触发时源极  $n^+$  下 方中性区的基区电阻为  $R_{B,t1}$  ,流经  $R_{B,t1}$  的雪崩触发

空穴电流为 Ini.i.,则 npn 管触发要满足下面条件[9]:

$$V_{\rm BEon} = R_{\rm B,tl} I_{\rm tl,ii} \tag{1}$$

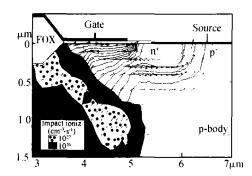

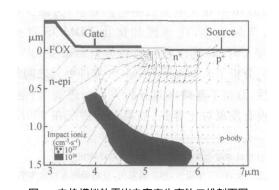

器件在触发点时,其等温模拟和电热模拟的电 离产生率不同.图3和图4分别是器件源区附近等 温模拟和电热模拟的二维剖面图,其中黑色填充区 域的电离产生率大于 10<sup>26</sup> cm<sup>-3</sup>·s<sup>-1</sup>;黑色圆点区域 的电离产生率大于 10<sup>27</sup> cm 3 · s 1; 实线代表电流 线;箭头表示空穴电流密度矢量.比较图3和图4, 可以得到两个显著的不同点:(1)图3中电离产生率 大于 10<sup>26</sup>cm<sup>-3</sup> · s<sup>-1</sup>的区域比图 4 中的区域大,且图 3 中有部分区域的电离产生率大于  $10^{27}$  cm  $^3$  ·s  $^1$ . 由此可知电热模拟的雪崩触发空穴电流小于等温模 拟的雪崩触发空穴电流.(2)图3和图4的电流线和 空穴电流矢量分布也有很大差别.图 3 中 n + 下方沿 平行表面方向流动的电流约占总电流的 1/4,这些 电流就是对寄生 npn 管触发有贡献的雪崩触发空 穴电流;而图 4 中,有贡献的雪崩触发空穴电流占总 电流的比例不到 1/10. 由图 2 可知,电热模拟的触 发电流比等温模拟的触发电流要小. 由上述分析可 推断电热模拟的雪崩触发空穴电流远小干等温模拟

图 3 等温模拟的雪崩电离产生率的二维剖面图

Fig. 3 Cross section indicating impact ionization rates of isothermal method

图 4 电热模拟的雪崩电离产生率的二维剖面图 Fig. 4 Cross section indicating impact ionization rates of non-isothermal method

的雪崩触发空穴电流.

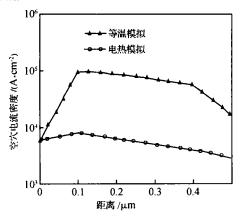

为证明上述结论的正确性,图 5 给出了雪崩触发空穴电流的电流密度曲线.由图可知电热模拟的雪崩触发空穴电流确实远小于等温模拟的雪崩触发空穴电流.

图 5 等温模拟和电热耦合模拟的雪崩触发空穴电流(横坐标 是 n<sup>+</sup>下方沿垂直表面方向的距离)

Fig. 5 Trigger hole current of avalanche breakdown of non-isothermal and isothermal methods

由于电热模拟的雪崩触发空穴电流远小于等温模拟的雪崩触发空穴电流,根据公式(1),电热模拟就很难达到寄生 npn 管触发的条件.要得到足够的雪崩触发空穴电流来触发该 npn 管导通,就需要比较大的漏源电压以产生更强的电场和更大的电离产生率.这就是等温模拟和电热模拟触发点不同的原因.

## 3 电热分析在 ESD 保护应用中的适 用性

# 3.1 等温模拟、电热模拟结果及与实验数据<sup>[9]</sup>的比较

文献 [8,9]提到等温模拟和 TLP(transmission line pulse) 实验结果在 ESD 保护的大电流区差异很大. 为使等温模拟结果更接近实验数据,文献 [8,9]引入器件宽度有效因子  $W_{\rm eff}=0.2W_{\rm actual}$ 来进行建模. 如采用电热分析的方法,就能避免用  $W_{\rm eff}=0.2W_{\rm actual}$ 进行建模. 为证实该想法,本文模拟了与文献 [9]相同结构、相同栅宽(栅宽  $W=136\mu$ m)的栅接地 40V-LDMOS.

图 6 给出了等温模拟、电热模拟结果的曲线和 文献[9]中的等温模拟、实验数据的曲线. 从该图可

以看出,该器件的等温曲线与文献[9]中模拟的等温曲线大致一样.尽管这两条等温模拟曲线都和实验结果<sup>[9]</sup>差别较大,但电热模拟曲线与实验结果<sup>[9]</sup>符合得更好.

图 6 本文中的等温模拟、电热模拟曲线和文献[9]中等温模拟、实验数据曲线

Fig. 6 FV curves of non-isothermal and isothermal methods in the paper and FV curves of isothermal and data results in Ref. [9]

#### 3.2 电热模拟结果与实验结果符合更好的原因

在电场和热场(即温度场)共同作用下,电子和空穴的电流输运方程[13]分别如公式(2)和(3)所示,熟知的热传导方程如公式(4)所示.

$$J_{n} = qn \mu_{n} \cdot E + qD_{n} \cdot \nabla n + qnD_{n}^{T} \cdot \nabla T$$

(2)

$$J_{p} = qn \mu_{p} \cdot E - qD_{p} \cdot \nabla p - qnD_{p}^{T} \cdot \nabla T (3)$$

$$\frac{\partial T}{\partial t} - D \cdot \nabla^2 (T) = \frac{-q(t)}{\cdot C_p}$$

(4)

其中 T 是晶格温度; t 是时间. 公式中各个量或参数的解释见文献[13].

公式 (2) 和 (3) 中第一项和第二项分别是电场和载流子浓度梯度引起的电流;第三项是晶格温度梯度引起的电流. 传统的半导体电流输运方程中没有第三项,第三项中的晶格温度梯度  $\nabla T$  就是热产生电流的来源. 公式 (4) 则表明了晶格温度与时间的关系(4,14).

本文假设衬底底面为热沉,其晶格温度恒定为300 K,衬底厚度为200µm. 用恒定的电流脉冲(上升时间为1ns)灌入漏极,以研究大电流脉冲突然来临时,LDMOS内部的局部电热效应. 在上述假设的前提下,从两方面分析电热模拟结果与实验结果更接近的原因. 一方面是晶格温度在空间上的分布特点;另一方面是漏极电压弛豫时间 temi (漏极电压达到稳态所需要的时间,下同)和晶格温度弛豫时间 temi

(晶格温度达到空间上的相对稳态分布所需要的时间,以局部最高晶格温度弛豫时间  $t_{temp,m}$  为例,下同)之间的关系.

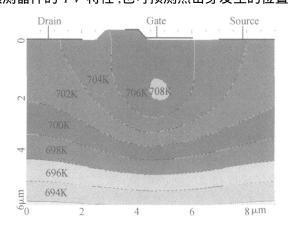

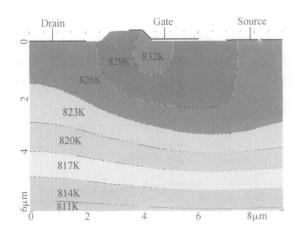

首先,分析晶格温度在空间上的分布特点.

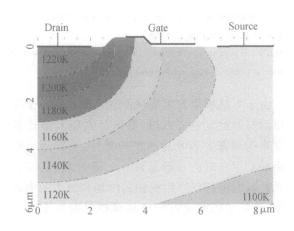

从半导体表面到衬底底面,晶格温度逐渐降低, 越来越接近 300 K. 图 7,8 和 9 是半导体表面器件区 域的晶格温度分布图,分别对应着 npn 管触发时, 负阻区和大电流区:局部最高晶格温度分别是708, 832 和 1220 K:局部最高晶格温度所在的位置分别 是栅极下方的器件内、栅极下方的表面和表面漏极. 由此可知,随漏极电流的增加,局部最高晶格温度的 位置不断变化,先从器件内部向表面移动,后沿着表 面移动到漏极.这预示器件表面的漏极和栅极位置 最易发生热击穿,且随着漏极电流的增加,晶格温度 梯度也在增大.图7和图8中局部最高晶格温度与 最低温度的温差分别是 14 和 21 K:而图 9 中温差高 达 100 K,约是图 8 中温差的 5 倍,表明在大电流区, 晶格温度梯度  $\nabla T$  急剧增加. 根据公式(2)和(3), ▽ T 引起的热产生电流已经不能忽略,逐渐代替击 穿产生电流而占据主导地位. 此时等温分析已经不 能准确预测器件的 FV 特性,电热分析既可更准确 预测器件的 FV 特性,也可预测热击穿发生的位置.

图 7 寄生 npn 管触发时的晶格温度分布图(图 6 中 A 点) Fig. 7 Space distribution of lattice temperature on triggering point of LDMOS 's intrinsic npn transistor

其次,分析漏极电压弛豫时间  $t_{train}$ 和晶格温度 弛豫时间  $t_{temp}$ 的关系.

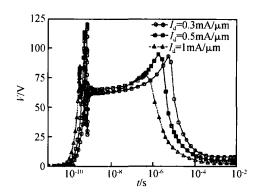

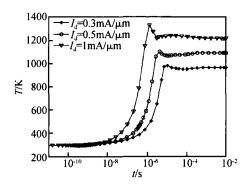

等温模拟结果表明,漏极电流的上升时间(1ns) 完毕后,漏极电压就进入稳态值,几乎没有弛豫时间;而电热模拟结果显示,同样的条件下,tdrain高达 µs 数量级,如图 10 所示,这与 temp 有关. 图 11 是局部最高晶格温度与时间的关系,在三种不同的漏极

图 8 负阻区源漏电压为 30V 时的晶格温度分布图(图 6 中 B 点)

Fig. 8 Space distribution of lattice temperature on negative resistance region when  $V_{\rm ds} = 30 \text{V}$

图 9 大电流区漏极电流为 1  $\times$  10  $^{-3}$  A/  $\mu$ m 的晶格温度分布图 (图 6 中 C 点)

Fig. 9 Space distribution of lattice temperature on high current region when  $I_{ds} = 1 \times 10^{-3} \text{ A}/\mu\text{m}$

电流下, $t_{temp.m}$ 都高达  $\mu$ s 数量级. 比较图 10 和图 11 可知,在相同的漏极电流下, $t_{drain}$  和  $t_{temp.m}$  是对应相等的. 例如,当漏极电流为  $10^{-3}$  A/ $\mu$ m 时, $t_{drain}$  和  $t_{temp.m}$ 都是  $1\mu$ s. 这说明  $t_{temp}$ 影响  $t_{drain}$ ,而  $t_{drain}$ 最终会改变器件的 tV 特性.

另外,如图 11 所示,局部最高晶格温度都经历一个上升过程达到峰值,然后下降到稳态值;漏极电流越大,局部最高晶格温度上升越快,其峰值和稳态值也越大;在稳态阶段前的弛豫时间阶段,局部最高晶格温度对于时间的微分 $\partial T/\partial t$  (图 11 中曲线每一点的切线)不等于 0 且是变化的. 在稳态阶段, $\partial T/\partial t$  近似等于 0. ESD 大电流脉冲持续时间的范围约为几百 ns 到十 ns [4]. 由图 11 可知,在该时间范围

图 10 在不同的恒定漏极电流下,漏极电压与时间的关系 Fig. 10 Drain voltage versus time under different drain currents

图 11 在不同的恒定漏极电流下,局部最高晶格温度与时间的关系

Fig. 11 Lattic temperature versus time under different drain currents

内, $\partial T/\partial t$  不等于 0 且是变化的,根据公式(4),半导体表面器件区域内的热传导在每一时刻并不相同,并最终影响器件的 FV 特性.

总之,在 ESD 保护的大电流区时,如果采用等温分析,漏极电压在很短时间内 (1ns) 就进入稳态;而电热分析考虑了  $t_{temp}$  对  $t_{drain}$  影响,漏极电压在很长时间内  $(50 1 \mu s)$  才进入稳态,再加上  $\forall T$  的存在,所以等温分析已经不能准确地预测器件的 FV 特性,而电热分析既能准确地预测器件的 FV 特性,不能预测热击穿发生的位置,其模拟结果也与实验结果符合得更好。

### 4 结论

(1)电热分析和等温分析所得的触发点不同的 主要原因是,在npn管的触发点,电热模拟的雪崩 触发空穴电流小于等温模拟的雪崩触发空穴电流.

(2) 通过研究晶格温度在空间上的分布特点以及 temp和 tdrain 的关系,证明当 LDMOS 工作于大电流区时,电热分析与实验结果符合得更好.

### 参考文献

- [1] Murari B, Bertotti F, Vignola G A. Smart power IC 's, technologies, and applications. 1st ed. Berlin: Springer-Verlag, 1995:56

- [2] Sze S M. Physics of semiconductor devices. 2nd edition. New York: Willy, 1981

- [3] Chen Xingbi. Power MOSFET and HVIC. Nanjing:UES Publishing,1990(in Chinese)[陈星弼. 功率 MOSFET 和高压集成电路. 南京:东南大学出版社,1990]

- [4] Amerasekera A, Duvvury C. ESD in silicon integrated circuits. 2nd edition. John Viley &Sons ,Ltd ,2002

- [5] Duvvury C, Carvajal F, Jones C, et al. Lateral DMOS design for ESD robustness. IEEE IEDM, 1997:375

- [6] Chung Y,Besse P,Zecri M,et al. Geometry effect on power and ESD capality of LDMOS power devices. ISPSD, Cambridge, UK, 2003, 14~17:265

- [7] Lee J H, Shih J R, Tang C S, et al. Novel ESD protection structure with embedded SCR LDMOS for smart power technology. 40th Annual Intenational Reliability Physics Symposium, Dallas, Texas, 2002:156

- [8] Mergens M, Wilkening W, Mettler S, et al. Analysis and compact modeling of lateral DMOS power devices under ESD stress conditions. Proc 21st EOS/ ESD Symp, Orlando, FL, 1999:1

- [ 9 ] Mergens M P J , Wilkening W , Mettler S ,et al. Analysis of lateral DMOS power devices under ESD stress conditions. IEEE Trans Electron Devices ,2000 ,47 (11) :2128

- [10] Denison M, Blaho M, Rodin P, et al. Moving current filaments in intergrated DMOS transistors under short-duration current stress. IEEE Trans Electron Devices, 2004, 51 (10):1695

- [11] TMA Medici. Technology Modeling Associates, Inc Version 2,1994

- [12] Dolny G M, Nostrand G E, Hill K E. The effect of temperature on lateral DMOS transistors in a power IC technology. IEEE Trans Electron Devices, 1992, 39(4):990

- [13] Stratton R. Semiconductor current-flow equations (diffusion and degeneracy). IEEE Trans Electron Devices, 1972, ED-19: 1288

- [14] Alwin V C, Navon D H, Turgeon L J. Time-dependent carrier flow in a transistor stucture under nonisothermal conductions. IEEE Trans Electron Devices, 1977, ED-24:1297

### Analysis of Local Electro-Thermal Effects of LDMOS Power Devices \*

Li Meizhi, Wei Guangping, and Chen Xingbi

(School of Microelectronics and Solid-State Electronics, University of Electronic Science and Technology of China, Chengdu 610054, China)

**Abstract :** Local electro-thermal effects of LDMOS after the first avalanche breakdown are analyzed. The different trigger points of LDMOS 's intrinsic npn transistor by isothermal and non-isothermal methods are compared and analyzed. The space distributing characteristics of lattice temperature are described, and the influence of  $t_{\text{temp}}$  (delay time of lattice temperature) on  $t_{\text{drain}}$  (delay time of drain voltage) is proposed. Thus, it is shown that the simulation results of the non-isothermal method are more consistent with the experimental data than those of the isothermal method, under ESD stress conditions.

Key words: isothermal; non-isothermal; trigger points; ESD; lattice temperature

**EEACC: 2560R**

Article ID: 0253-4177 (2005) 09-1823-06

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60476036)

Li Meizhi female, was born in 1978, PhD candidate. She is interested in research on power devices and smart power IC.

Wei Guangping female, was born in 1979, master candidate. She is interested in research on smart power IC.

Chen Xingbi male, was born in 1931, academician of Chinese Academy of Sciences. He is interested in research on the power devices and smart power ICs.