## Design of an OP-AMP Based on a LDO Regulator \*

Fan Hua and Feng Quanyuan

(Institute of Microelectronics, Southwest Jiaotong University, Chengdu 610031, China)

**Abstract :** An operational amplifier (OP-AMP) with a ground current of about 0. 6µA is presented. Moreover, this amplifier reaps the benefits of incorporating a foldback current limiting circuit, which enables the low-dropout voltage regulator without the need of a special current limiting subblock. Therefore, the object of ultra-low power is realized because of a great reduction in transistors and current limbs.

Key words: operational amplifier; ground current; LDO; foldback current limiterEEACC: 1220CLC number: TN722. 7Document code: AArticle ID: 0253-4177 (2005) 10-1905-05

## 1 Introduction

The explosive proliferation of battery-powered equipment in the past decade has accelerated the development of low-power-consumption low-dropout (LDO) voltage regulators. This has intensified the focus of designers on optimizing the performance of the amplifiers<sup>[1]</sup>. When the load-current is low ,which is the normal operating mode for many applications ,the ground current becomes an intrinsic factor in determining the lifetime of the batter $y^{[2,3]}$ .

In this paper ,the amplifier incorporating foldback current limiter , whose ground current is only 0.  $6\mu A$  to ensure the LDO regulator to operate at a ground current as low as 2.  $4\mu A$  throughout its load range has a very small number of current paths.

## 2 Circuit design

#### 2.1 Main structure of the LDO

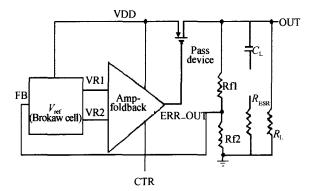

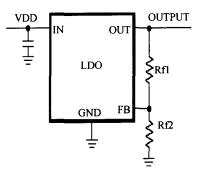

A low-dropout regulator is a circuit that provides a well specified and stable voltage. The input to output voltage difference of this circuit is low. The main structure of the LDO chip and its typical application circuit we designed is shown in Figs. 1 and 2 respectively. The regulator is basically composed of a pMOS pass transistor, an amplifier with a foldback current limiter, a set of resistive feedback networks Rf1 and Rf2, a load resistor  $R_L$ , a voltage reference  $V_{ref}$  based on Brokaw cell<sup>[4]</sup> whose function is to take a scaled-down version of the output and then provide differential signals VR1 and VR2 to the amplifier<sup>[5]</sup>, therefore the amplifier adjusts  $V_{OUT}$  via the pMOS pass transistor to a re-

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60371017)

Fan Hua female, was born in 1981. Her current interests are in intelligent signal process, low-power and low-voltage analog integrated circuits. Email :fanhua7531 @sina.com, fanhua7531 @163.com

Feng Quanyuan male, was born in 1963, professor, advisor of PhD candidates. His research interests include microwave & millimeter wave technology, integrated circuits design, electromagnetic compatibility and environmental electromagnetics, mobile antenna & smart antenna system, microwave devices & microwave materials.

Received 7 April 2005, revised manuscript received 11 June 2005

quired value.  $G_{L}$  is a filtering capacitor with equivalent series resistance  $R_{ESR}$ . The value of ESR determines the output performance during the load tran-

Fig. 1 Main structure of LDO

Fig. 2 Typical application circuit

sient. The smaller the ESR value, the better the perfor-mance, with less overshoots and undershoots during the load transient. The LDO features a p-channel MOSFET pass transistor. This provides advantages over similar designs using a pnp pass transistor - on advantage being longer battery life. The p-channel MOSFET requires no base drive, which reduces ground currents considerably.

#### 2.2 OP-AMP circuit design

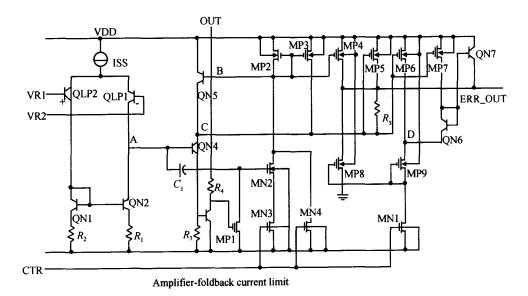

The amplifier we designed incorporates a foldback current limiter - this subblock is abbreviated to amp-foldback (Fig. 3).

As shown in Fig. 3, VR1 and VR2 are the noninverting and inverting inputs of the amplifier respectively. ERR – OUT is the output of the amplifier which controls the gate of pMOS pass device of the LDO. VDD is the power supply. OUT, which controls the gate of MN2, is the output pin of the LDO chip. CTR controls the gates of MN1, MN3, and MN4, offering biasing voltage to the amplifier. VR1 and VR2 are the inputs of the first stage with node A as the output, meanwhile, node A is the input of the second stage with ERR – OUT as the output of the second stage.

Fig. 3 Amp-foldback subblock schematic

The W/L ratios of MP6 and MP7 are designed equal, since their gate-source voltages are equal, their drain currents will be the same. That is  $I_{MP6} = I_{MP7}$ , Since  $V_{DS_{-}MP9} = V_{GS_{-}MP9}$ , MP9 will be in saturation and is given by

$$I_{\rm MP9} = I_{\rm MN1} = I_{\rm MP6} + I_{\rm MP7}$$

(1)

Thus, IMP6 is given by

$$I_{\rm MP6} = \frac{1}{2} I_{\rm MN1} = \frac{1}{4} \mu_0 C_{\rm ox} \frac{W_{\rm MN1}}{L_{\rm MN1}} (V_{\rm CTR} - V_{\rm ThN})^2$$

(2)

Equation (2) indicates that  $I_{MP6}$  is fixed, so  $V_{GS^*MP6}$  keeps constant, which gives rise to a very nearly constant node voltage  $V_{C}$ .

From the above analyses, operational principles of the amplifier can be concluded as follows: if the variation of differential inputs VR1, VR2 causes variation of node voltage  $V_A$  then a slight variation of  $V_C$  will lead to massive variation of  $V_{\text{ERR-OUT}}$ , which is the output of the amplifier.

QN5 has been added to balance current. This can be explained as follows: since  $V_{DS\_MP2} = V_{GS\_MP2}$ , MP2 will be in saturation causing  $V_{GS\_MP2}$  to be fixed, then voltage on node B  $V_B$  maintains constant. When the LDO regulator is in normality and  $V_{OUT}$  is large enough to turn MN2 on,  $I_{MP2}$  is given by

$$I_{\rm MP2} = I_{\rm MN3} + I_{\rm MN4}$$

(3)

Since the W/L ratios of MN3 and MN4 are designed equal, both are one fourth of that of MN1, moreover,  $V_{GS_MN1} = V_{GS_MN3} = V_{GS_MN4}$ , then

$$I_{\rm MN1} = 2(I_{\rm MN4} + I_{\rm MN3})$$

(4)

From Eqs. (2), (3), and (4), we get

$$I_{\rm MP6} = I_{\rm MP2} \tag{5}$$

Since the W/L ratio of MP6 is designed larger than that of MP2 ,it can be deduced that  $V_{\rm C} > V_{\rm B}$  ,transistor QN5 now being turned off. For node C applying KCL (the base current of QN5 is neglected)

$$I_{\text{E-QN4}} = I_{\text{C-QN4}} = I_{\text{QN5}} + I_{\text{MP3}} + I_{\text{R5}}$$

(6)

An increase in the voltage of non-inverting terminal VR1 will increase  $I_{E_QN4}$  owing to higher base-emitter voltage of QN4. From above analyses,  $I_{QN5} = 0$ , MP2 and MP3 are connected as a current mirror, thus  $I_{MP3}$  is fixed. For Eq. (6), an increase of  $I_{R5}$  is a must. Then  $V_{ERR_OUT}$  and  $V_D$  will increase (Since  $V_{\text{ERR-OUT}} + V_{\text{BE-QN7}} = V_{\text{D}} + V_{\text{BE-QN6}}$ , it can be deduced that  $V_{\text{D}} = V_{\text{ERR-OUT}}$ ) turning off QN6,QN7 at some point,  $I_{\text{MP6}}$  will be twice and  $V_{\text{C}}$  will decrease instantaneously, and this drop in  $V_{\text{C}}$  continues as long as  $I_{\text{EQN4}} > I_{\text{MP3}} + I_{\text{R5}}$ . As a result,QN5 will be turned on thus Equation (6) is satisfied, which is to say the current equilibrium point is established.

MN2 and R5 are the kernels of the foldback current limiter. The maximum value of the output current is limited by R5, and MN2 restricts the short-circuit current to a range that is 50mA when the OUT terminal of the LDO chip is connected to ground.

When the output current is large enough and results in  $V_{\text{ERR-OUT}} < V_{\text{C}}$ , then

$$I_{\rm R5} = I_{\rm MP3} - I_{\rm QN4} - I_{\rm MP3} - I_{\rm QN4\_min}$$

(7)

$$I_{\rm R5\_max} = I_{\rm MP3} - I_{\rm QN4\_min}$$

(8)

$V_{\text{ERR}_{\text{OUT}}} = V_{\text{C}} - I_{\text{R}_{5}} R_{5} \qquad V_{\text{C}} - (I_{\text{MP3}} - I_{\text{QN4}_{\text{min}}}) R_{5}$ (9)

$$V_{\text{ERR_OUT_min}} = V_{\text{C}} - (I_{\text{MP3}} - I_{\text{QN4_min}}) R_5$$

(10)

When the LDO is under normal operating conditions, VOUT is large enough to turn MN2 on, MP2 and MP3 are connected as a current mirror and the widthto-length ratios of them are designed 1 2, thus  $I_{MP3} =$  $2I_{MP2} = 2(I_{MN3} + I_{MN4})$ . When Equation (10) is satisfied, gate voltage of pMOS pass element of the LDO  $(V_{\text{ERR-OUT}})$  reaches its minimum value, leading to the maximum output current. At this time, if  $R_{LOAD}$  further continues to decrease ,VOUT will continually drop ,turning MN2 off at some point, thus IMP3 is reduced by half, which is to say,  $I_{MP3} = 2 I_{MN4}$ . From Eq. (10), VERR\_OUT\_min increases , leading to a decrease in maximum output current. Finally ,the maximum value of the output current is limited to a range that is 50mA when the OUT terminal of the LDO chip is connected to ground.

#### **3** Simulated results

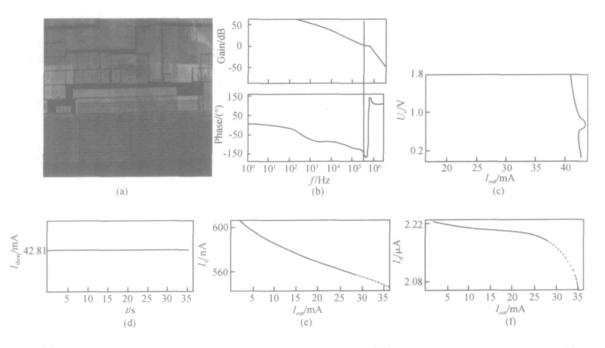

Figure 4(a) is the layout of the LDO including proposed operational amplifier. The AMP-Foldback circuit in Fig. 3 is simulated at  $V_{DD} = V_{OUT} + 1$ . Meanwhile the LDO regulator with this kind of amplifier is tested. The gain result is shown in Fig. 4(b) ,which is only 60dB but already meets the required transient response ,stability ,and load regulation characteristics of the LDO wholechip. The phase margin of the amplifier is about 45. Figure 4 (c) shows the simulation result of the foldback current limiter. The steady output of the LDO under normal operating conditions is 1. 8V ,when the load current decreases to the point where MN2 will be turned off, restricting the short-circuit current to 43mA. When OUT is shorted to ground, the short-circuit current is 42. 81mA (Fig. 4 (d)). As shown in Figs. 4 (e) and (f), at a 20mA load current, the ground currents consumed by the amplifier and by the LDO regulator are 0. 57 and 2.  $21\mu A$ respectively. Obviously, high current efficiency is achieved especially at a low output current.

Fig. 4 (a) Layout of the LDO including proposed operational amplifier; (b) Gain and phase of the amplifier; (c) Simulation result of the foldback current limit; (d) Simulation result of the short-circuit current; (e) Ground current of the amplifier subblock versus load current; (f) Ground current of the LDO wholechip versus load current

## 4 Conclusion

In this paper, we combine an amplifier and a foldback current limiter into a single circuit with a minimum number of current limbs making it a candidate for an ultra-low power LDO.

#### References

[1] Yin T, Zhu Z M, Yang Y T, et al. Analysis of bulk-driven MOSFET and design of ultra-low voltage operational amplifier. Chinese Journal of Semiconductors, 2005, 26(1):158(in Chinese)[尹韬,朱樟明,杨银堂,等. 衬底驱动 MOSFET 特 性分析及超低压运算放大器设计.半导体学报,2005,26(1): 1581

- [2] Lau S K,Leung K N, Mok P K T. Analysis of low-dropout regulator topologies for low-voltage regulation. IEEE International Conference on Electron Devices and Solid-State Circuits, 2003:379

- [3] Rincor-Mora A, Allen P E. A low-voltage, low quiescent current, low drop-out regulator. IEEE J Solid-State Circuits, 1998, SC-33(1):36

- [4] Hastings R A. Brokaw transconductance operational transconductance amplifier-based micropower low drop out voltage regulator having counterphase compensation. US Patent Application, No. 09/470910, filed December 23, 1999

- [5] Brokaw A P. Stable low dropout voltage regulator controller. US Patent Application. No. 647241, filed May 9,1996

# 一种基于 LDO 线性稳压器的放大器设计\*

#### 樊 华 冯全源

(西南交通大学微电子研究所,成都 610031)

摘要:设计了一种地电流约为 0. 6µA 的基于低压差线形稳压器的放大器电路.此放大器的突出优点是与 foldback 限流保护电路融合在一起,使得芯片不需要专门的限流模块,大大减少了电流支路,实现超低功耗.

关键词:运算放大器;地电流;LDO; foldback 过流保护

EEACC: 1220

中图分类号:TN722.7 文献标识码:A 文章编号:0253-4177(2005)10-1905-05

<sup>\*</sup>国家自然科学基金资助项目(批准号:60371017)

樊 华 女,1981年出生,硕士研究生,主要研究方向为模拟集成电路的设计与研究. Email:fanhua7531 @sina.com,fanhua7531 @l63.com

冯全源 男,1963年出生,教授,博士生导师,主要研究兴趣有:集成电路设计,半导体材料及器件,电磁兼容与环境电磁学,微波及毫米波技术,移动天线与智能天线系统,微波器件及材料等.