# A DBRTD with a High PVCR and a Peak Current Density at Room Temperature \*

Yili Chengrong, Xie Changqing, Wang Congshun, Liu Ming, and Ye Tianchun

(Micro Processing and Nano Technology Laboratory, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract :** AlAs/ GaAs/ In<sub>0.1</sub> Ga<sub>0.9</sub> As/ GaAs/ AlAs double-barrier resonant tunneling diodes (DBRTDs) grown on a semi-insulated GaAs substrate with molecular beam epitaxy is demonstrated. By sandwiching the In<sub>0.1</sub> Ga<sub>0.9</sub> As layer between GaAs layers, potential wells beside the two sides of barrier are deepened, resulting in an increase of the peak-to-valley current ratio (PVCR) and a peak current density. A special shape of collector is designed in order to reduce contact resistance and non-uniformity of the current; as a result the total current density in the device is increased. The use of thin barriers is also helpful for the improvement of the PVCR and the peak current density in DBRTDs. The devices exhibit a maximum PVCR of 13. 98 and a peak current density of 89kA/ cm<sup>2</sup> at room temperature.

Key words: resonant tunneling diode; peak-to-valley current ratio; peak current density

EEACC: 2530C; 2560Z

CLC number: TN312. 2

Document code: A

Article ID: 0253-4177 (2005) 10-1871-04

### 1 Introduction

Double barrier resonant tunneling diodes (DBRTDs) have received great attentions for their potential applications in frequency multiplication, microwave oscillation, analog-to-digital conversion, and static random access memory<sup>[1~4]</sup> because of their negative differential resistance (NDR) performance. To incorporate the DBRTD in the practical circuit, a high peak-to-valley current ratio (PVCR) larger than 5 and a high peak current density near to  $10^5 \text{ A/ cm}^2$  are required.

Since Tsu and Esaki<sup>[5]</sup>, and Chang *et al.*<sup>[6]</sup> first proposed and demonstrated NDR through DBRTDs, many efforts have been made to improve the performances of DBRTDs. Soderstrom *et al.*<sup>[7]</sup> fabricated InAs/AlSb DBRTD on a semi-insulated (SI) GaAs substrate with a PVCR of 11 and a peak current density of 4. 3kA/cm<sup>2</sup> at room temperature. A pseudomorphic  $In_{0.53}$  Ga<sub>0.47</sub> As/AlAs/InAs DBRTD on SI InP substrate with a PVCR of 50 and a peak current density of 5. 8kA/cm<sup>2</sup> at room temperature has also been reported<sup>[8]</sup>.

The option and preparation of different materials and structures are crucial to the performance of DBRTDs. Low electron effective mass in material and high conduction-band offset ( $E_C$ ) between barrier and well can improve the PVCR in DBRTDs resulting from reduction of the valley current. Due to lower electron effective mass ,properties of InP-substrate RTDs are generally better than those of GaAs-substrate ones ,and some novel materials of barrier and well have also been adopted<sup>[9]</sup> so as to obtain the same aims. However ,consequent difficulty in MBE growth of new materials ,and high fragility of InP resulting in rigorous process ,baffle them into real application.

In this paper in order to deepen the wells beside the two sides of the barrier, sub-well lays are

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60236010)

Yili Chengrongmale, was born in 1974, PhD candidate. His research interest is in RTD and its integration. Email :ylcr2002 @yahoo.com.cnReceived 16 April 2005, revised manuscript received 27 May 2005c 2005 Chinese Institute of Electronics

used through the introduction of an In<sub>0.1</sub> Ga<sub>0.9</sub> As layer between GaAs layers. Due to the reduction of the non-tunneling current, a high PVCR is obtained. Thin barriers and a special shape of collector are used for enlargement of the peak current density and the total current density, respectively. Device performance with a maximum PVCR of 13. 98 and a peak current density of 89kA/cm<sup>2</sup> are demonstrated at room temperature successfully.

## 2 Material structure and device fabrication

The AlAs/ GaAs/  $In_{0.1}$  Ga<sub>0.9</sub> As/ GaAs/ AlAs DBR TDs are grown on SI GaAs (100) substrate by using J EN- molecular beam epitaxy (MBE) equipment. The growth sequence begins with four step-graded n<sup>+</sup>- GaAs buffer layers ,followed by an undoped GaAs spacer layer, an undoped In<sub>0.1</sub>-Ga<sub>0.9</sub> As strained layer ,and an undoped GaAs spacer layer. The well-barrier structure consists of an In<sub>0.1</sub> Ga<sub>0.9</sub> As sub-well layer ,two GaAs well layers , and two AlAs barrier layers. Then there are symmetrical structures that are composed of a same spacer layer , a strained layer , a spacer layer , and buffer layers in turn. Table 1 shows the structure and doping profiles of the DBR TD.

| Table 1 | Schematic | MB E | structure | of | the | DBRTD |

|---------|-----------|------|-----------|----|-----|-------|

|---------|-----------|------|-----------|----|-----|-------|

| 500nm  | GaAs                 | 3 ×10 <sup>18</sup> cm <sup>-3</sup> |

|--------|----------------------|--------------------------------------|

| 5nm    | GaAs                 | 1 ×10 <sup>18</sup> cm <sup>-3</sup> |

| 5nm    | GaAs                 | 5 ×10 <sup>17</sup> cm <sup>-3</sup> |

| 5nm    | GaAs                 | $1 \times 10^{17} \text{cm}^{-3}$    |

| 5nm    | GaAs                 |                                      |

| 5nm    | Ino. 1 Gao. 9 A s    |                                      |

| 0.5nm  | GaAs                 |                                      |

| 4nm    | $In_{0,1}Ga_{0,9}As$ |                                      |

| 0.5nm  | GaAs                 |                                      |

| 1. 7nm | AlAs                 |                                      |

| 0. 5nm | GaAs                 |                                      |

| 1. 7nm | AlAs                 |                                      |

| 0. 5nm | GaAs                 |                                      |

| 5nm    | Ino. 1 Gao. 9 A s    |                                      |

| 5nm    | GaAs                 |                                      |

| 5nm    | GaAs                 | 1 ×10 <sup>17</sup> cm <sup>-3</sup> |

| 5nm    | GaAs                 | $5 \times 10^{17} \text{cm}^{-3}$    |

| 5nm    | GaAs                 | 1 ×10 <sup>18</sup> cm <sup>-3</sup> |

| 1000nm | GaAs                 | 3 ×10 <sup>18</sup> cm <sup>-3</sup> |

|        | (100) SF GaAs subst  | rate                                 |

Isolated mesa structures are formed by contact photolithography (Suss Microtec) and non-selective wet etching techniques (citric acid solution: hydrogen peroxide = 10 1). Resist is used for mask in etching. Au GeNiAgAu and TiAu metalization (DMDE450 film evaporation station) are made for the ohmic contacts and connect line, respectively, by metal lift-off. SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> are deposited through Nextral PECVD to form insulated layers and then are removed partly by wet etching (NH<sub>4</sub>F

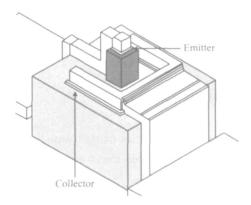

ice acetic acid = 1 1) and RIE dry etching respectively to open windows for connect lines. Figure 1 shows the schematic mesa structure of the DBRTD without the  $SiO_2/Si_3N_4$  layer in order to view easily.

Fig. 1 Schematic mesa structure of the DBRTD

## 3 Device measurements and discussion of results

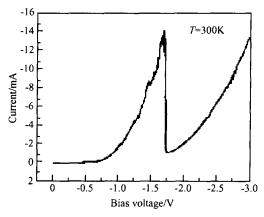

The current-voltage (*FV*) characteristics of the diodes are measured at room temperature by a semi-conductor parameter analyzer. Figure 2 shows the *FV* characteristic of the DBRTD with a 4 $\mu$ m × 4 $\mu$ m emitter at room temperature. The *FV* characteristic of the DBRTD is measured with a negative bias ,which refers to an electron injection from the bottom contact ,i. e. bottom buffer. For the negative bias the PVCR is 13. 98 and the peak current density is 89kA/cm<sup>2</sup>. The performances of the DBRTDs are much better than those of Wang *et al.*<sup>[10]</sup>, with roughly identical materials structure, as well as other reported DBRTDs with GaAs substrate so far.

Fig. 2 FV curve of RTD with a 4µm ×4µm emitter PVCR = 13. 98 with  $I_p$  = - 0. 014309A,  $V_p$  = - 1. 68V,  $I_v$  = - 0. 0010236A,  $V_v$  = - 1. 707V

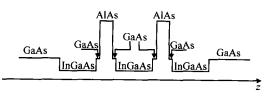

The great improvement of performance can be attributed to the use of In<sub>0.1</sub> Ga<sub>0.9</sub> As layers, better quality material ,and fabrication flows. As shown in Fig. 3, the conduction band energy level of  $In_{0,1}$ - $Ga_{0.9}$  As is lower than that of GaAs, so when  $In_{0.1}$ -Ga0.9 As layer is introduced between GaAs layers, the potential well of GaAs layer is deepened, resulting in an increase of relative height of AlAs barriers. It is helpful to enlarge both the PVCR and the peak current density, and at the same time non-tunneling current components are depressed efficiently. The roles of In<sub>0.1</sub> Ga<sub>0.9</sub> As layers can be similar to sub-well<sup>[11]</sup> when In<sub>0.1</sub> Ga<sub>0.9</sub> As layers lie in GaAs space layers and GaAs well respectively. The thicknesses of the AlAs barrier layers are as thin as 1. 7nm and are also helpful to increase the PVCR and the peak current density, since the thinner the barriers are, the higher the peak current densities are, and the PVCRs of devices are then enlarged<sup>[12]</sup>.

Fig. 3 Schematic conduction band diagram with z direction that parallels the current one in DBRTD

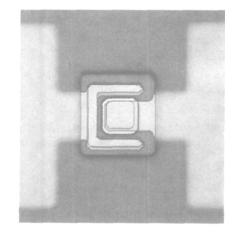

As shown in Fig. 4, the emitter of the RTD is surrounded by its collector. This unique layout is used for the reduction of contact resistance and non-uniformity in the emitter current, resulting in large current density in the DBRTDs.

Fig. 4 Top picture of RTD

### 4 Conclusion

Through introducing the In<sub>0.1</sub> Ga<sub>0.9</sub> As layer between the GaAs layers in AlAs/ GaAs/ In<sub>0.1</sub> Ga<sub>0.9</sub>-As/ GaAs/ AlAs DBRTDs with SI-GaAs substrate, the potential well of GaAs layer is deepened, and the height of barriers is functionally able to be enhanced, resulting in the realization of a high PVCR and a peak current density. Thin barriers and a special shape of collector are presented and used for increasing the peak current density and the total current density respectively. The characteristic of DBRTDs at room temperature in this work are much better than all other reported GaAs-substrate DBRTDs. From a practical point of view, this is very encouraging.

Acknowledgements The authors would like to thank Mr. Liu Xunchun and Mr. Sun Haifeng at Compound Semiconductor Laboratory for valuable process direction as well as Mr. Wang Baoqiang at Institute of Semiconductors (CAS, PRC) for highquality MBE growth.

#### References

- [1] Sen S, Capasso F, Cho A Y, et al. Multiple-state resonant tunneling bipolar transistor operation at room temperature and its application as a frequency multiplier. IEEE Electron Device Lett, 1988, 9:533

- [2] Brown E R, Sollner T C L G, Goodhue W D, et al. Millimeterband oscillators based on resonant tunneling in a double-barrier diode at room temperature. Appl Phys Lett, 1987, 50:835

- [3] Guo T H,Lin H C,Potter R C,et al. A novel A/D converter using resonant tunneling diodes. IEEE J Solid-State Circuits, 1991,26:145

- [4] Wei SJ, Lin H C. Multivalued SRAM cell using resonant tunneling diodes. IEEE J Solid-State Circuits, 1992, 27:212

- [5] Tsu R, Esaki L. Tunneling in a finite superlattice. Appl Phys Lett, 1973, 22(11):562

- [6] Chang L L, Esaki L, Tsu R. Resonant tunneling in semiconductor double barriers. Appl Phys Lett, 1974, 24(12):593

- [7] Soderstrom J R, Chow D H, McGill T C. InAs/AlSb doublebarrier structure with large peak-to-valley current ratio: a candidate for high-frequency microwave devices. IEEE Elec-

tron Device Lett ,1990 ,11(1) :27

- [8] Smet J H,Broekaert T P E,Fonstad C G. Peak-to-vally current ratios as high as 50 1 at room temperature in pseudomorphic In<sub>0.53</sub> Ga<sub>0.47</sub> As/AlAs/InAs resonant tunneling diodes.J Appl Phys,1992,71 (5):2475

- [9] Su Y K, Chang J R, Lu Y T, et al. Novel AlInAsSb/ InGaAs double-barrier resonant tunneling diode with high peak-tovally current ratio at room temperature. IEEE Electron Device Lett, 2000, 21 (4):146

- [10] Wang Zhenkun, Liang Huilai, Guo Weilian, et al. Design and fabrication of resonant tunneling diode. J Micronanoelectronic Technology, 2002, 7:13 (in Chinese) [王振坤,梁惠来,郭维 廉,等. 共振隧穿二极管的设计和研制. 微纳电子技术, 2002, 7:13]

- Broekaert T P E, Fonstad C G. Extremely high current density, low peak voltage, pseudomorphic In<sub>0.53</sub> Ga<sub>0.47</sub> As/ AlAs/ InAs resonant tunneling diodes. IEEE International Electron Devices Meeting, 1989

- [12] Tsuchiya M, Sakaki H, Yoshino J. Room temperature observation of differential negative resistance in an AlAs/ GaAs/ AlAs resonant tunneling diode. Jpn J Appl Phys, 1985, 24 (6) :L466

# 室温下高峰谷电流比、高峰电流密度的 双势垒共振隧穿二极管<sup>\*</sup>

#### 易里成荣 谢常青 王从舜 刘 明 叶甜春

(中国科学院微电子研究所 微加工与纳米技术实验室,北京 100029)

摘要: 在半绝缘 GaAs 衬底上制作了 AlAs/ GaAs/ Ino.1 Gao.9 As/ GaAs/ AlAs 双势垒共振隧穿二极管. 在 GaAs 层中 加入 Ino.1 Gao.9 As 层用以降低势垒两边的势阱深度,从而提高了器件的峰谷电流比和峰电流密度.为了减小器件的 接触电阻和电流的非均匀性,使用了独特形状的集电极,总的电流密度也因此提高.薄栅也有助于提高器件的 PVCR 和峰电流密度.在室温下测得其峰谷电流比高达 13.98,峰电流密度大于 89kA/ cm<sup>2</sup>.

关键词:共振隧穿二极管;峰谷电流比;峰电流密度

EEACC: 2530C; 2560Z

中图分类号: TN312.2

文献标识码: A

文章编号: 0253-4177(2005)10-1871-04

\*国家自然科学基金资助项目(批准号:60236010) 易里成荣 男,1974年出生,博士研究生,研究方向是 R TD 器件及其集成. 2005-04-16 收到,2005-05-27 定稿