# A Fractional- N CMOS DPLL with Self-Calibration

Liu Sujuan<sup>1</sup>, Yang Weiming<sup>1</sup>, Chen Jianxin<sup>1</sup>, Cai Liming<sup>2</sup>, and Xu Dongsheng<sup>2</sup>

(1 Optoelectronics Laboratory, Beijing University of Technology, Beijing 100022, China)

(2 China Integrated Circuit Design Center, Beijing 100015, China)

**Abstract :** A digital phase-locked loop (DPLL) based on a new digital phase-frequency detector is presented. The self-calibration technique is employed to acquire wide lock range ,low jitter ,and fast acquisition. The DPLL works from 60 to 600M Hz at a supply voltage of 1. 8V. It also features a fractional-N synthesizer with digital 2nd-order sigma-delta noise shaping ,which can achieve a short lock time ,a high frequency resolution ,and an improved phase-noise spectrum. The DPLL has been implemented in SMIC 0. 18µm 1. 8V 1P6M CMOS technology. The peak-to-peak jitter is less than 0. 8 % of the output clock period and the lock time is less than 150 times of the reference clock period after the pre-divider.

Key words: digital phase-locked loop; phase-frequency detector; self-calibration; voltage controlled oscillator; fractional-N

**EEACC:** 2570

CLC number : TN431 Document code : A

Article ID: 0253-4177 (2005) 11-2085-07

## 1 Introduction

Phase-locked loops (PLLs) are widely used for clock generation in digital and mixed analog/ digital chips designed for wireless communication and other applications. Low frequency and phase jitter are very important performance requirements for PLLs. The wide lock range is another key requirement in PLLs because of the constant device for more bandwidth in modern communication<sup>[11]</sup>. Considerable work has been put into reducing jitter. In 1996, Maneatis introduced a self-biased technique to achieve minimal jitter accumulation in PLL<sup>[21]</sup>. Optimizing the parameters of the phaselocked loop also improves the jitter performance to some extent<sup>[31]</sup>. However, when the lock range increases, the jitter of the output clock also increases<sup>[4,5]</sup>. So, this design focuses on presenting a method to meet wide lock range and low jitter requirements at the same time. The proposed digital PLL (DPLL) uses a digital phase-frequency detector (DPFD) and a self-calibration technique to get wide lock range, low jitter, and fast acquisition. It also features a fractional-N synthesizer with digital 2nd-order sigma-delta noise shaping to achieve a high frequency resolution and an improved phasenoise spectrum.

# 2 DPLL structure and operating principles

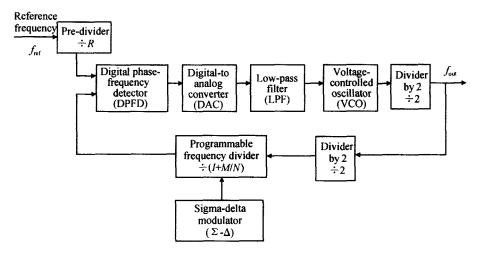

A DPLL functional block diagram is shown in Fig. 1. DPFD detects the phase and frequency

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2002AA1Z1290)

Liu Sujuan female ,was born in 1978 ,PhD candidate. Her research interests are CMOS analog and mixed integrated circuits design.

Yang Weiming male, was born in 1969, PhD candidate. His research interest is RF circuits design.

Chen Jianxin male, was born in 1946, professor, advisor of PhD candidates. His research fields involve high-speed microelectronics and integrated circuits design.

Received 27 November 2004 , revised manuscript received 25 July 2005

difference between the reference and the output clock from the programmable divider. In this design, the difference is a five-bit multi-level pulse from the digital up/ down counter. The multi-level pulse is fed to a digital-to-analog converter (DAC) to be converted into an analog signal. The low-pass filter smoothes the analog signal and the output is the control voltage of the voltage-controlled oscillator (VCO). The VCO changes its output frequency according to the control voltage and the output frequency is proportional to the average value of the multi-level pulse. The feedback loop is closed via the dividers, which forces the system to go to a steady state.

Fig. 1 DPLL functional block diagram

The frequency of the VCO is twice the output frequency. The first divider by two is utilized to achieve a 50 % duty cycle, which is critical in most applications. The second divider by two assures that the programmable divider operates on a lower frequency and reduces the multiplication factor range. The programmable divider is connected between the VCO and the DPFD to generate the various output frequencies. From Fig. 1, the DPLL produces an output clock at the frequency :

$$f_{\text{out}} = \frac{2}{R} \left( I + \frac{M}{N} \right) f_{\text{ref}} \tag{1}$$

where  $f_{ref}$  is the reference frequency ,its range is 10 ~ 100M Hz ,  $f_{out}$  is the output frequency ,its range is 60 ~ 600M Hz , R is the pre-division factor ,the integer from 1 to 16 , I is the integer part of the multiplication factor F(F = I + M/N) , I is in range from 5 to 16 ,if it is less than 5 ,the DPLL accepts 5 ,M/NN is the fraction part of the multiplication factor F. Here M and N are integer ,respectively in the ranges of 0 ~ 1023 and 1 ~ 1024.

### **3** Circuit description

#### 3.1 Digital phase-frequency detector

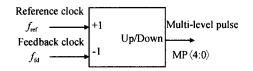

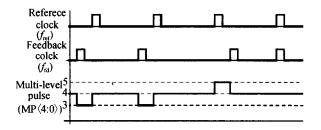

In this design, the DPFD is implemented as a 5bit asynchronous up/down counter (Fig. 2). During the lock-in process the frequency of the reference clock and feedback clock is different. The counter is incremented by 1 at the positive edge of the reference clock and decremented by 1 at the positive edge of the feedback clock. Thus, the DPFD generates a multi-level pulse MP 4 0 (as shown in Fig. 3). If the reference clock frequency is higher, MP 4 0 increases to raise the frequency of the VCO. If the feedback clock frequency is higher ,MP 4 0 decreases to lower the frequency of the VCO. When the reference clock and the feedback clock have equal frequency, the multi-level pulse MP 4 0 has a constant duty cycle and the VCO is exactly tuned to the required frequency.

Fig. 2 Digital frequency-phase detector

Fig. 3 Reference clock ,feedback clock ,and multi-level pulse MP 4 0

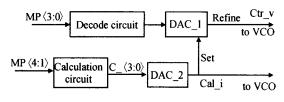

The self-calibration technique is employed to speed-up the lock-in process. The self-calibration is performed by two DACs (DAC  $\_$  1 and DAC  $\_$  2) and illustrated by Fig. 4. The higher bits of MP 4

0 ,MP 4 1 ,after being calculated and converted from digital to analog ,functions as the calibration current (Cal  $\_$  i). The lower bits MP 3 0 , after being decoded and converted from digital to analog ,functions as the control voltage (Ctr  $\_$  v). Control voltage (Ctr  $\_$  v) is fed to a low-pass filter and the output voltage controls the VCO frequency.

Fig. 4 Block diagram of self-calibration

The self-calibration process is described as follows. At first, the DPLL is reset and enabled respectively by the reset and enabling signals. And then, the DPLL calculates the calibration current (Cal\_i) according to the reference clock ( $f_{ref}$ ) and the multiplication factor (F).

After that, the calibration current (Cal - i)sets the control voltage (Ctr - v) to a special range and assures that the VCO will be close to the center of the frequency range. At the same time, the calibration current (Cal  $\_$  i) adjusts the VCO 's step size and makes it proportional to the reference clock. All these help the DPLL get the wider frequency range and the reduced lock time.

After calibration, the control voltage  $(Ctr_v)$  will have a small vibration due to the vibration of the MP 3 0. The feedback loop refines them according to the control voltage  $(Ctr_v)$  until the loop is locked with low jitter.

Through the three steps the DPLL acquires the wide frequency range, short frequency lock time, and low jitter.

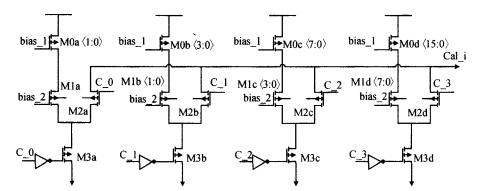

Figure 5 is the core structure of the DAC  $\_$  2, which is a 4 bits current scaling DAC using binaryweighted current sources with input codes  $C_{-}3$  $0 \cdot C_{-} = 3 \quad 0$  are the outputs of the MP 4 1 after being calculated; bias\_1 and bias\_2 are the bias voltage generated by the internal bias block. Current scaling is implemented by the  $2^1(2)$  to  $2^4$ (16) matched MOSFETs. The conversion time of DAC\_2 is very short and insensitive to parasitics because there are no floating nodes compared with the generic current scaling DAC. The output current, Cal\_i, is sent to DAC\_1 and VCO to set the control voltage and adjust the step size of the VCO. The DAC \_ 1 is a parallel-input monolithic multiplying DAC with very high-speed performance and its output is control voltage, Ctr \_ v. The conversion time of the DAC \_ 1 is less than 20ns.

The DPLL also has a phase adjusting block, which generates a control signal that minimizes the phase jitter and skews between reference and output clocks. The phase adjusting block starts after frequency lock is achieved. This work mode is the frequency/phase lock mode and can be selected by the user. The frequency/phase lock mode is used for synchronous applications and sampling A/D and D/A precision converters, where a phase error can be very important. The frequency/phase lock mode will be introduced in later work.

#### 3.2 Voltage-controlled oscillator

In this design, a ring-based voltage-controlled

Fig. 5 Core structure of DAC \_ 2

oscillator (VCO) is chosen because it has no external components and is well suitable for integration. Its intrinsic phase noise is relatively high and the dominant noise source is actually due to the power supply. Such noise typically appears as steps or impulses on the power supply of the oscillator ,and it affects both the frequency and phase of the VCO, causing cycle-to-cycle jitter<sup>[6]</sup>.

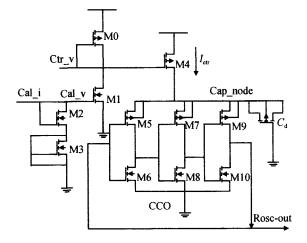

The VCO core structure is shown in Fig. 6. It is based on an inverter-type ring oscillator supplied by a current  $I_{ctr}$  coming from the voltage-to-current converter. The voltage-to-current converter is a simple MOS device M4 in the quadratic region, making the overall VCO transfer function approximately linear. A current controlled oscillator (CCO) is the basic element of the VCO, which allows high-frequency operation at low voltage operation.

Fig. 6 Core structure of VCO

Transistors M4 and M0 of the current mirror are perfectly matched. Ctr \_ v controls current  $I_{ctr}$ and current  $I_{ctr}$  controls the delay time  $t_d$  of the CCO. For the equivalent small-signal circuit,  $t_d$  $\frac{V_{dd}}{I_{ctr}}$  while  $I_{ctr}$   $V_{dd}$ , so the effects of the power supply noise can be partly counteracted.

A decoupling capacitance  $C_d$  composed of a set of pMOS transistors across the CCO helps to reduce the supply noise injected through parasitic capacitance. The sources and bulks of the transistor M5,M7, and M9 connected to the node cap – node not to  $V_{dd}$  assures that the CCO is not sensitive to the supply voltage. All these improve the power supply noise rejection ratio (PSNR) of the VCO.

Rosc \_ res is the reset signal of the ring oscillator. Cal \_ i sets the control voltage and adjusts the step size of the VCO after self-calibration. The Ctr \_ v refines the VCO until the VCO is exactly tuned to the required frequency. The Cal \_ v is the output of the Cal \_ i through the current-to-voltage converter.

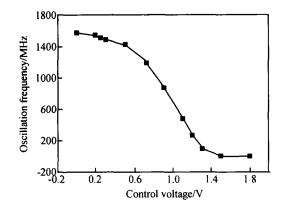

The VCO output frequency as a function of control voltage is shown in Fig. 7.

#### 3.3 Implementation of fractional-N synthesizer

The fractional-N synthesizer is implemented by the programmable divider selecting the division factor I or I + 1 through the divider modulus control. Equation (2) can be deduced from Eq. (1).

$$f_{\text{out}} = \frac{2}{R} \mathbf{x} \left[ \frac{M}{N} (I+1) + \frac{N-M}{N} I \right] f_{\text{ref}} \quad (2)$$

Fig. 7 VCO frequency versus the control voltage Ctr \_ v

During M work cycles ,the division factor is set to I + 1 ,while during the N - M work cycles ,the division factor is set to I. The fraction part is converted by a digital accumulator to a sequence of "1" and "0".

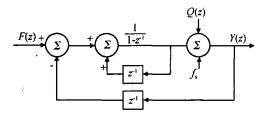

This technique can get a high frequency resolution with a reduced lock time. However, because of a switch of the division factor from I to I + 1, this technique generates undesired spurs. The output is at  $\frac{2}{R}(I + \frac{M}{N}) f_{ref}$  with the spurs at offset frequencies equal to multiples of  $\frac{M}{N} f_{ref}$ . So in this design, a sigma-delta modulator is used to eliminate the spurs. The basic structure of the first order sigma-delta modulator is shown in Fig. 8. Equation (3) can be deduced from Fig. 8.

Fig. 8 First-order sigma-delta modulator

$$Y(z) = F(z) + H_n(z) Q(z)$$

(3)

$H_n(z)$  and Q(z) respectively is the phase noise and quantization noise.

$$|H_n(f)| = \left|2\sin(\frac{f}{f_s})\right|, \quad 0 \quad f \quad \frac{f_s}{2}$$

(4)

At low frequencies,  $|H_n(f)|$  tends to go to zero,

and when the frequency is near  $\frac{f_s}{2}$ ,  $|H_n(f)|$  tends to go to the maximum value of 2. The sigma-delta modulator moves the phase noises to higher frequencies, where it would be filtered by the loop<sup>[7]</sup>.

To get better phase noise spectral ,a higher order sigma-delta modulator is used to shape progressively to a high degree. However the higher order sigma-delta modulator with several feedbacks is not always stable<sup>[8]</sup>. So ,in this design a second order sigma-delta modulator is employed.

### 4 **Results**

The DPLL has been simulated by SMIC SPICE model for 0. 18µm logic 1. 8V 1P6M process and the simulation tool is HSPICE. The chip is fabricated in SMIC 0. 18µm, 1. 8V, 1P6M, standard digital CMOS process. Table 1 summarizes the preliminary DPLL performance measurement results.

Table 1 DPLL performance measurement results

| Output frequency range          | 60 ~ 600M Hz                        |

|---------------------------------|-------------------------------------|

| Power consumption               | < 3. 5mW at supply voltage of 1. 8V |

| Lock time                       | $< 150 T_{\rm pre}  (< 15 \mu s)$   |

| Frequency jitter (peak to peak) | $< 0.8$ % of $T_{\rm out}$          |

| Phase noise                     | - 102. 6dBC/ Hz @10k Hz off set     |

| Minimum frequency resolution    | 10k Hz                              |

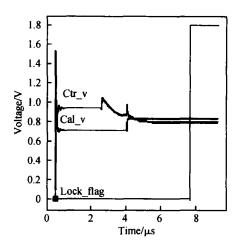

Figure 9 is the simulated results of Cal  $\_$  v, Ctr  $\_$  v, and lock flag when the DPLL locks at 400M Hz. The DPLL also has a lock control module. The lock control module contains a set of timers indented to generate all necessary control signals during the lock-in time. The lock flag being "1" indicates that the loop is locked. In Fig. 9, the lock flag becomes "1" at 7. 659µs and the loop is locked.

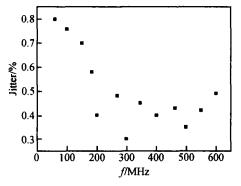

Figure 10 shows the measured frequency peakto-peak jitter versus the output frequency. Jitter is the percent of the absolute jitter/output clock period. It shows that jitter is less than 0.5% of the output clock period for operating frequencies greater than 200MHz. At lowest frequency (at 60MHz), jitter increased to the maximum 0.8%,

Fig. 9 Simulated Cal \_ v ,Ctr \_ v ,and lock flag

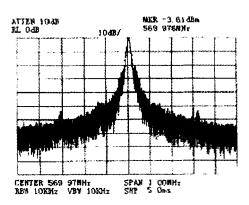

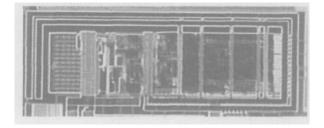

mainly because the loop bandwidth of the DPLL still needs to optimize. Figure 11 is the output spectrum of the proposed DPLL. Figure 12 is the microphotograph of the proposed DPLL core structure.

Fig. 10 Measured frequency peak-to-peak jitter versus DPLL output frequency

Fig. 11 Output spectrum of the DPLL

Here  $T_{out}$  is the output clock period and  $T_{pre}$  is the reference clock period after the pre-divider.

Fig. 12 Microphotograph of the proposed DPLL core structure

### 5 Conclusion

A digital phase-locked loop based on a new phase-frequency detector is fabricated in SMIC 0.  $18\mu$ m, 1. 8V, 1P6M, standard digital CMOS process. The self-calibration technique is employed to acquire a wide locking range, low jitter, and fast acquisition. The DPLL works from 60 to 600MHz with the VCO output frequency from 100 to 1500MHz at a supply voltage of 1. 8V. The peak-to-peak jitter is less than 0. 8% of the output clock period and the lock time is less than 150 times of the reference clock period after the pre-divider.

#### References

- [1] Chao Xu, Sargeant W, Laker K R, et al. An extended frequency range CMOS voltage controlled oscillator. IEEE Circuits and Systems, 2002, 2:425

- Maneatis J G. Low-jitter process-independent DLL and PLL based on self-biased techniques. IEEE Solid-State Circuits, 1996,31(11):1723

- [3] Mansuri M, Ken C K. Jitter optimization based on phase-locked loop design parameters. IEEE Solid-State Circuits, 2002, 37(11):1375

- [4] Razavi B. A study of phase noise in CMOS oscillators. IEEE Solid-State Circuits, 1996, 31 (3):331

- [5] Hajimiri A ,Limotyrakis S ,Lee T H.Jitter and phase noise in ring oscillators. IEEE Solid-State Circuits ,1999 ,34(6) :790

- [6] Pialis T, Phang K. Analysis of timing jitter in ring oscillators due to power supply noise. IEEE Circuits and Systems, 2003, 1:685

- [7] Bourdi T,Borjak A, Kale I. A delta-sigma frequency synthesizer with enhanced phase noise performance. IEEE Instrumentation and Measurement Technology ,2002 ,1 :247

- [8] Shu K, Sanchez-Sinencio E, Maloberti F. A comparative study of digital - modulators for fractional-N synthesis. IEEE Circuits and Systems, 2001, 3:1391

## 一种具有自校准功能的 CMOS 分数数字锁相环<sup>\*</sup>

刘素娟'杨维明'陈建新'蔡黎明'徐东升'

(1 北京工业大学光电子实验室,北京 100022)(2 中国华大集成电路设计中心,北京 100015)

摘要:提出了一种数字锁相环(DPLL),它的相频检测器采用全新的设计方法和自校准技术,具有工作频率范围 宽,抖动低,快速锁定的优点.锁相环在 1.8V 外加电源电压时,工作在 60~600MHz 的频率范围内.采用分数分频 技术,加速锁定过程并具有较小的输出频率间隔,利用 - 调制改善相位噪声性能.设计在 SMIC 0.18µm,1.8V, 1P6M 标准 CMOS 工艺上实现,峰-峰相位抖动小于输出信号周期的 0.8%,锁相环的锁定时间小于参考频率预分 频后信号周期的 150 倍.

关键词:数字锁相环;相频检测器;自校准;压控振荡器;分数分频 EEACC:2570 中图分类号:TN431 文献标识码:A 文章编号:0253-4177(2005)11-2085-07

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2002AA1Z1290)

刘素娟 女,1978年出生,博士研究生,研究方向为 CMOS 模拟/混合集成电路设计.

杨维明 男,1969年出生,博士研究生,研究方向为 RF 集成电路设计.

陈建新 男,1946年出生,教授,博士生导师,研究领域为超高速微电子学与集成电路设计.