# An Analytical Threshold Voltage Model for Fully Depleted SOI MOSFETs

Li Ruizhen and Han Zhengsheng

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract :** A new two-dimensional (2D) analytical model for the threshold-voltage of fully depleted SOI MOSFETs is derived. The 2D potential distribution functions in the active layer of the devices are obtained through solving the 2D Poisson 's equation. The minimum of the potential at the oxide-Si layer interface is used to monitor the threshold voltage of the SOI MOSFETs. This model is verified by its excellent agreement with MEDICI simulation using SOI MOSFETs with different gate lengths, gate oxide thicknesses, silicon film thicknesses, and channel doping concentrations.

Key words: fully depleted SOI MOSFETs; surface potential; threshold voltageEEACC: 2520M; 2560BCLC number: TN386Document code: AArticle ID: 0253-4177(2005)12-2303-06

## 1 Introduction

Recently there has been an increasing interest in fully depleted SOI MOSFETs<sup>[1]</sup> because of their inherent immunity to the kink effect<sup>[2]</sup>, nearly ideal sub-threshold voltage swing<sup>[3]</sup>, and immunity to the short channel effect<sup>[4]</sup>. Many related models have been reported. The 2D Poisson 's equations have been solved for both silicon film and buried oxide in Refs. [5,6], and thus the minimum potential has been obtained. The threshold voltage is defined as the gate voltage at which the minimum potential is capable of sustaining the fully depleted channel region. However, the Green function technique is used in solving the Poisson's equations, thereby involving infinite series and increasing the computation complexity. These models are not suitable for circuit simulation. Young 's model<sup>[7]</sup> proposed the parabolic function distribution of potential in the active layer for the first time. Some other models were reported<sup>[8~12]</sup> using this assumption. Too many fitting parameters and experimential equations were used in Ref. [8], with the result that the model is hard to understand and has lost physical meaning. In Ref. [9] the threshold voltage was defined as the gate voltage at which the minimum of the surface potential equals the Fermi potential of the channel region. This is not consistent with normal conditions and will lead to a lower threshold voltage. In Ref. [10] the 2D Poisson 's equation was solved in the active layer to obtain minimum potential distribution. The potential at the front interface between the gate and silicon films was defined as the gate voltage minus the built-in voltage of the Schottky barrier at the gate. This boundary condition is not accurate for SOI MOSFETs. The threshold voltage was defined as the gate voltage for which the minimum of the potential was zero. This is not accurate because at

Li Ruizhen male, was born in 1978, PhD candidate. His research interest includes IC processes, device models, and parameters extraction. Email : liruizhen @ime. ac. cn

Han Zhengsheng male, was born in 1962, advisor of PhD candidates. His primary research interest includes SOI/ CMOS VLSI technologies and designs.

threshold voltage the minimum of the potential may be far from zero.

In this paper ,an analytical model for fully depleted SOI MOSFETs is proposed. The parabolic function distribution of the potential in the active layer is adopted. The potential distribution at the front surface of the channel is derived. The results of this model closely agree with MEDICI simulation.

# 2 Theoretical model

#### 2.1 Potential distribution analysis

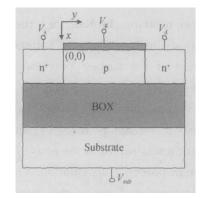

The schematic structure of a fully depleted SOI MOSFET is shown in Fig. 1. Before the onset of strong inversion, Poisson 's equation in the active layer can be written as

$$\frac{d^{2}(x, y)}{dx^{2}} + \frac{d^{2}(x, y)}{dy^{2}} = \frac{qN_{ch}}{s_{i}}$$

$$0 \quad x \quad T_{Si}, 0 \quad y \quad L \quad (1)$$

Fig. 1 Cross-section of an n-channel SOI MOSFET

where q is the electron charge and  $N_{\rm ch}$  is the doping concentration in the channel region. Because the silicon film thickness is small, the doping concentration in the channel region is assumed to be uniform. Here si is the permittivity of the silicon film,  $T_{\rm Si}$  is the thickness of the silicon film, and L is the channel length. When the drain voltage  $V_{\rm d}$  is small, the x-dependence of (x, y) can be approximated by a simple parabolic function:

$$f(x, y) = f(y) + k_1(y) x + k_2(y) x^2$$

(2)

where f is the potential distribution function at the interface between the gate oxide and silicon film, and  $k_1(y)$  and  $k_2(y)$  are functions of y independent of x. The functions  $k_1(y)$  and  $k_2(y)$  can be determined by the following boundary conditions:

$$(T_{\rm Si}, y) = b(y)$$

(3)

$$\frac{\mathbf{d}_{-}(x, y)}{\mathbf{d}x}\Big|_{x=0} = \frac{\mathbf{o}x}{\mathbf{s}i} \times \frac{\mathbf{f}(y) - V_{\text{gfeff}}}{T_{\text{fox}}}$$

(4)

$$\frac{\mathbf{d}(x,y)}{\mathbf{d}x}\Big|_{x=T_{Si}} = \frac{-\infty}{Si} \times \frac{V_{gheff} - b(y)}{T_{box}}$$

(5)

where  $_{b}(y)$  is the potential distribution function at the bottom interface between the silicon film and buried oxide layer,  $_{ox}$  is the permittivity of the buried oxide layer , and  $V_{gfeff}$  and  $V_{gbeff}$  are the effective voltages of the front gate and back gate respectively, which are given by

$$V_{\text{gfeff}} = V_{\text{g}} - V_{\text{FBf}}$$

(6)

$$V_{\text{gbeff}} = V_{\text{sub}} - V_{\text{FBb}}$$

(7)

where  $V_g$  is the gate voltage,  $V_{FBF}$  is the flat-band voltage between the gate and channel, and  $V_{FBb}$  is the flat-band voltage between the channel and substrate.  $V_{FBF}$  and  $V_{FBb}$  are given as

$$V_{\rm FBf} = \frac{kT}{q} \ln \left( \frac{N_{\rm g} N_{\rm ch}}{n_{\rm s}^2} \right) +$$

(8)

$$V_{\rm FBb} = \frac{kT}{q} \ln \left( \frac{N_{\rm sub}}{N_{\rm ch}} \right)$$

(9)

where k is the Boltzmann constant, T is the absolute temperature,  $n_i$  is the intrinsic carrier concentration,  $N_g$  is the doping concentration of the polysilicon gate,  $N_{sub}$  is the doping concentration of the substrate, and is a fitting parameter.

Equations  $(3 \sim 9)$  can be used to determine  $k_1(y)$  and  $k_2(y)$ .

$$k_{1}(y) = \frac{\sigma_{x}}{s_{i}} \times \frac{f(y) - V_{gfeff}}{T_{fox}}$$

(10)

$$k_{2}(y) = \frac{-(1 + C_{f}/C_{Si} + C_{f}/C_{b}) + (C_{f}/C_{Si} + C_{f}/C_{b})V_{gfeff} + V_{gbeff}}{T_{Si}^{2}(1 + 2C_{Si}/C_{b})}$$

(11)

Substituting Eq. (2) into (1) yields the differential equations:

$$\frac{d^{2} f(y)}{dy^{2}} - f f(y) = f$$

(12)

$$f = \frac{2(1 + C_{f}/C_{Si} + C_{f}/C_{b})}{T_{Si}^{2}(1 + 2C_{Si}/C_{b})}$$

(13)

$$_{\rm f} = \left( \begin{array}{c} \frac{qN_{\rm ch}}{{\rm Si}} - 2 \frac{\left( \frac{C_{\rm f}}{C_{\rm Si}} + \frac{C_{\rm f}}{C_{\rm b}} \right) V_{\rm gfeff} + V_{\rm gheff}}{T_{\rm Si}^2 \left( 1 + 2 C_{\rm Si} / C_{\rm b} \right)} \right) / (14)$$

where  $C_{\rm f} = _{\rm ox}/$

$$T_{\text{fox}} \text{ is the front gate oxide capaciby}$$

$$y) = -\frac{-f}{f} + \frac{\Phi_{\text{bi}} + V_{\text{ds}} + -f/-f}{2 \operatorname{sh}(-\sqrt{f}L)} \exp\left(-\sqrt{f}(L-y)\right) + \frac{2 \operatorname{sh}(-\sqrt{f}L)}{2 \operatorname{sh}(-\sqrt{f}L)} \exp\left(-\sqrt{f}(L-y)\right) + \frac{2 \operatorname{sh}(-\sqrt{f}L)}{2 \operatorname{sh}(-\sqrt{f}L)} \exp\left(-\sqrt{f}L\right)} \exp\left(-\sqrt{f}L\right)$$

$$(15)$$

#### 2.2 Threshold voltage

f ( '

The position of the minimum front surface potential can be obtained by solving the equation  $d_{f}(y)/dy = 0$ . It is given by

$$y_{0} = \frac{L}{2} + \frac{1}{2 \sqrt{f}} \times \ln\left(\frac{\phi_{bi} + f/f - (\phi_{bi} + V_{ds} + f/f) \exp(f - \sqrt{f}L)}{\phi_{bi} + V_{ds} + f/f - (\phi_{bi} + f/f) \exp(f - \sqrt{f}L)}\right)$$

(16)

Substituting Eq. (16) into (15) can give the value of the minimum front surface potential:

$$f_{min} = -\frac{-f}{f} + 2\{ f \Phi_{bi} + \frac{-f}{f} - (\Phi_{bi} + V_{ds} + \frac{-f}{f}) \times f \}$$

$$\exp\left(-\sqrt{f}L\right) \int \left[ \Psi_{6i} + V_{ds} + \frac{1}{f} - \left( \Psi_{6i} + \frac{1}{f} \right) \right] \times$$

$$\exp\left(-\sqrt{f}L\right) ] j^{1/2} \frac{\exp\left(-\sqrt{f}L/2\right)}{1 - \exp\left(-2\sqrt{f}L\right)} \quad (17)$$

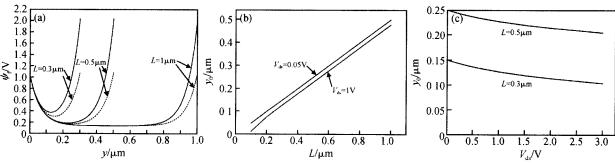

potential across the body-source junction, and bi =  $kT \ln(N_{\rm ch} N_{\rm ds}/n_{\rm i}^2)/q$ .  $N_{\rm ds}$  is the doping concentration of the source and drain. Then f(y) can be solved ) Figure 2(a) shows the potential distribution at the front surface between the gate oxide and silicon film. The dashed lines represent the potential distribution at a small drain voltage (0. 05V), and the solid lines represent the potential distribution at a large drain voltage (1V). When the drain voltage is

tance,  $C_{\rm Si} = {\rm si}/T_{\rm Si}$  is the silicon film capacitance,  $C_{\rm b}$

$= _{ox}/T_{box}$  is the buried oxide layer capacitance ,and is a fitting parameter. Equation (12) can be solved by using the following boundary conditions: f(0)=  $_{bi}$ ,  $_{f}(L) = V_{ds} + _{bi}$ , where  $_{bi}$  is the built-in

large, a small error will be introduced by the 2D effect, which affects the surface potential but not the threshold voltage model because it is based on a small drain voltage.

Compared to devices with long channel length, the devices with short channel length have a higher potential minimum. This reduces the channel barrier. So a short channel device has a smaller threshold voltage. As the drain voltage increases, the potential minimum and the channel barrier are reduced. This effect is called drain-induced barrier

Fig. 2 (a) Calculated front surface potential distribution The device parameters are:  $T_{\text{fox}} = 10$  nm,  $T_{\text{Si}} = 100$  nm,  $T_{\text{box}} = 10$ 320nm,  $N_{ch} = 1.2 \times 10^{17} \text{ cm}^{-3}$ . The substrate bias is 0V. The dashed lines show the data for  $V_{ds} = 0.05V$ , and the solid lines for  $V_{ds} = 1V$ ; (b) Calculated location of potential minimum as a function of channel length; (c) Calculated location of potential minimum as a function of drain voltage

lowering (DIBL). DIBL in short channel devices is more evident than in long channel devices as shown in Fig. 2(a).

For long channel devices  $\exp(-(f)^{1/2}L) \ll 1$ . When the drain voltage is small ,the second term of Eq. (16) is approximately zero ,and  $y_0 = L/2$ . That means the potential minimum occurs at the center of the channel for devices with large channel length (see Fig. 2 (a)). But this is not true for devices with short channel length because of the short channel effect (SCE). As the drain voltage increases and channel length decreases ,the second term of Eq. (16) cannot be omitted. The location of the potential minimum gets closer to the source (see Figs. 2(b) and (c)).

The threshold voltage can be defined quantitatively as the gate voltage where f,min becomes 2 b. Here b is the Fermi barrier and can be given as

$$\Phi_{\rm b} = \frac{kT}{q} \ln \left( \frac{N_{\rm ch}}{n_{\rm i}} \right) \tag{18}$$

For devices with a large channel length, the second term of Eq. (17) is approximately zero. The following equations are obtained by substituting  $f_{,min} = 2$  b into Eq. (17) :

$$\frac{-f}{f} = -2\Phi_{b}$$

(19)

Solving Eq. (19) can give the threshold voltage of devices with large channel length.

$$V_{\text{th0}} = \frac{qN_{\text{ch}} T_{\text{Si}}^2 \left(1 + 2C_{\text{Si}}/C_{\text{b}}\right) - 2 S_{\text{Si}} V_{\text{gbeff}} + 4\phi_{\text{b}} S_{\text{i}} \left(1 + C_{\text{f}}/C_{\text{Si}} + C_{\text{f}}/C_{\text{b}}\right)}{2 S_{\text{si}} \left(C_{\text{f}}/C_{\text{Si}} + C_{\text{f}}/C_{\text{b}}\right)} + V_{\text{FBf}}$$

(20)

For devices with small channel length the second term of Eq. (17) cannot be omitted. The following approximation is used :exp(-( $_{\rm f}$ )<sup>1/2</sup>L)  $\ll$ 1, 1 - exp(-( $_{\rm f}$ )<sup>1/2</sup>L) 1 and the following equations are obtained:

$$a = 1 - 4\exp\left(-\sqrt{f}L\right)$$

(21)

$$b = 2 f_{\text{f,min}} - 8 \exp(-\sqrt{f}L) \phi_{\text{bi}} - 4 \exp(-\sqrt{f}L) V_{\text{ds}}$$

(22)

$$c = 4 f_{f,min}^2 - 4 (\theta_{bi} + \theta_{bi} V_{ds}) \exp(-\sqrt{f}L)$$

(23)

$$d = \frac{-b + \sqrt{b^2 - 4ac}}{2a}$$

(24)

$$\frac{-f}{f} = d$$

(25)

The threshold voltage can be obtained by solving Eq. (25). Notice that Eq. (25) resembles Eq. (19), except for the right side. Substituting Eq. (21) into (24) and  $f_{min} = 2 \ b$ , b = -d/2 into Eq. (20), the threshold voltage of devices with small channel length can be obtained.

## **3** Model verification

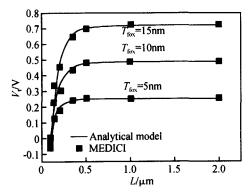

The threshold voltage versus gate length for different gate oxide thicknesses is plotted in Fig. 3. The threshold voltage decreases with the decrease of gate oxide thickness because the coupling between gate and channel is greater for devices with a thinner gate oxide. And the dependence of the threshold voltage on gate oxide thickness is reduced when the gate oxide is small. Therefore a thin gate oxide is more attractive in practice. But if the gate oxide is too thin, a leakage current may occur because of the tunneling effect. A material with a high permittivity can prevent leakage current while retaining a small equivalent oxide thickness (EO T).

Fig. 3 Threshold voltage versus gate length for different gate oxide thicknesses The device parameters are:  $T_{\rm Si} = 100$  nm,  $T_{\rm box} = 320$  nm,  $N_{\rm ch} = 1.2 \times 10^{17}$  cm<sup>-3</sup>,  $V_{\rm ds} = 0.05$  V.

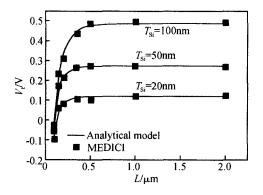

The threshold voltage versus gate length for different silicon film is plotted in Fig. 4. The

threshold voltage of devices with smaller silicon film thicknesses is lower than that of the devices with larger silicon film thicknesses. This is because there is less charge to be coupled by the gate for the devices with a small silicon film thickness. It also shows that the dependence of threshold voltage on silicon film thickness is small when the devices have a thinner silicon film. It seems that the silicon film should be thin enough. In practice, if the silicon film thickness is less than a critical thickness, tunneling will occur. Compared with the devices that have a thick silicon film, devices with a thin silicon film must have a higher channel doping concentration to fulfill a given threshold voltage requirement.

Fig. 4 Threshold voltage versus gate length for different silicon film thicknesses The devices parameters are:  $T_{\text{fox}} = 10$  nm ,  $T_{\text{box}} = 320$  nm ,  $N_{\text{ch}} = 1.2 \times 10^{17}$  cm<sup>-3</sup> ,  $V_{\text{ds}} = 0.05$  V.

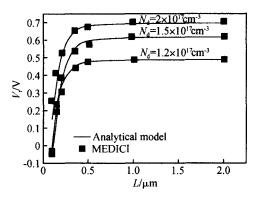

The threshold voltage versus gate length for different channel doping concentrations is plotted in Fig. 5. It can be seen that the devices with a higher channel doping concentration have a higher threshold voltage ,and the dependence of threshold voltage on channel doping concentration is large for these devices. So there must be a tradeoff during the course of device design.

## 4 Conclusion

In this paper an accurate threshold voltage model for SOI MOSFETs has been proposed. It in-

Fig. 5 Threshold voltage versus gate length for different channel doping concentrations The devices parameters are :  $T_{\text{fox}} = 10$  nm ,  $T_{\text{box}} = 320$  nm ,  $T_{\text{Si}} = 100$  nm ,  $V_{\text{ds}} = 0.05$  V.

volves only two fitting parameters. This model has been verified by comparison with simulation results for the devices with different gate oxide thicknesses, silicon film thicknesses, and channel doping concentrations. The simulated data agree closely with the predictions of the model. This model has a simple function form and has no complex mathematical computations such as infinite series. It is easily to be embedded into circuit design software and will play an important role in device and process design.

#### References

- Colinge J P. Silicononrinsulator technology :materials to VL-SI. Boston : Kluwer Academic Publishers ,1991

- [2] Cheng Yuhua, Wang Yangyuan. Analytical current model for thin film SOI m-channel MOSFET 's applicable to circuit simulation. Chinese Journal of Semiconductors, 1992, 13(9):547 (in Chinese)[程玉华,王阳元. 薄全耗尽 SOI 膜 n 沟道 MOS-FET 强反型电流模型. 半导体学报, 1992, 13(9):547]

- [3] Liu Xinyu, Sun Haifeng, Liu Hongmin, et al. Fully depleted CMOS/ SOI technology. Chinese Journal of Semiconductors, 2003,24(1):104(in Chinese)[刘新宇,孙海峰,刘洪民,等.全 耗尽 CMOS/ SOI 工艺.半导体学报,2003,24(1):104]

- [4] Zhang Xing, Wang Yangyuan. Design and fabrication of 0.15µm thin film fully depleted MOS/SOI device. Chinese Journal of Semiconductors,2000,21(2):156(in Chinese)[张 兴,王阳元.0.15µm 薄膜全耗尽 MOS/SOI 器件的设计和研 制.半导体学报,2000,21(2):156]

- [5] Hou C S, Wu C Y. A 2D analytic model for the thresholdvoltage of fully depleted short gate-length Si-SOI

MOSFET 's. IEEE Trans Electron Devices, 1995, 42 (12):

- [6] Chiang T K, Wang Y H, Houng M P. Modeling of threshold voltage and subthreshold swing of short-channel SOI MES-FET 's. Solid-State Electron, 1999, 43:123

- [7] Young K K. Short-channel effect in fully depleted SOI MOS-FET 's. IEEE Trans Electron Devices ,1989 ,36(2) :399

- [8] Cheng B J, Shao Z B, Tang T T, et al. Modeling of subthreshold characteristics of deep-submicrometer FD devices. Chinese Journal of Semiconductors, 2001, 22 (7):908

- [9] Fu J, Tian L L, Qian P X, et al. An analytic threshold-voltage model for fully-depleted SOI MOSFET. Chinese Journal of E-

lectronics ,1996 ,24(5) :48

- [10] Pandey P, Pal B B, Jit S. A new 2D model for the potential distribution and threshold voltage of fully depleted shortchannel Si-SOI MESFETs. IEEE Trans Electron Devices, 2004,51(2):246

- [11] Suzuki K, Pidin S. Short-channel single-gate SOI MOSFET model. IEEE Trans Electron Devices ,2003 ,50(5) :1297

- [12] Yeh P C, Fossum J G. Physical subthreshold MOSFET modeling applied to viable design of deep-submicrometer fully depleted SOI low-voltage CMOS technology. IEEE Trans Electron Devices ,1995 ,42 (9) :1605

# 全耗尽 SOI MOSFETs 阈值电压解析模型

#### 李瑞贞 韩郑生

(中国科学院微电子研究所,北京 100029)

摘要:提出了一种新的全耗尽 SOI MOSFETs 阈值电压二维解析模型.通过求解二维泊松方程得到器件有源层的 二维电势分布函数,氧化层-硅界面处的电势最小值用于监测 SOI MOSFETs 的阈值电压.通过对不同栅长、栅氧厚 度、硅膜厚度和沟道掺杂浓度的 SOI MOSFETs 的 MEDICI模拟结果的比较,验证了该模型,并取得了很好的一致 性.

关键词:全耗尽 SOI MOSFETs;表面势;阈值电压

EEACC: 2520M; 2560B

中图分类号: TN386

文献标识码: A

文章编号: 0253-4177(2005)12-2303-06

韩郑生 男,1962年出生,博士生导师,从事 SOI/ CMOS 集成电路技术和设计的研究.

2156

李瑞贞 男,1978年出生,博士研究生,从事集成电路工艺、器件模型及参数提取的研究. Email :lirulizhen @ime.ac.cn