Vol. 26 No. 12 Dec. .2005

# 低电场应力下闪速存储器的退化特性\*

#### 郑雪峰 郝 跃 刘红侠 马晓华

(西安电子科技大学微电子学院、宽禁带半导体材料与器件教育部重点实验室、西安 710071)

摘要:基于负栅源边擦除的闪速存储器存储单元,研究了形成应力诱生漏电流的三种导电机制,同时采用新的实验方法对引起瞬态和稳态电流的电压漂移量进行了测量.并利用电容耦合效应模型对闪速存储器存储单元的可靠性进行了研究,结果表明,在低电场应力下,其可靠性问题主要由载流子在氧化层里充放电引起.

关键词:闪速存储器:应力诱生漏电流:低电场应力:电容耦合效应

**PACC:** 7300; 7200J **EEACC:** 2810D

中图分类号: TN406 文献标识码: A 文章编号: 0253-4177(2005)12-2428-05

#### 1 引言

闪速存储器 (flash memory, 闪存) 是基于 EPROM, EEPROM发展起来的一种新型非挥发性 半导体存储器. 它具有价格便宜、工艺相对简单、可方便快速地进行多次擦写的特点,自问世以来,闪存在存储领域得到了广泛应用,在嵌入式系统中更是不可缺少的[1~3].

随着闪存使用的越来越多,其可靠性问题也就越来越重要.闪存的可靠性主要包括两个方面:一方面是器件的耐久性问题,指经过多次擦写后器件不会失效;另一方面是器件的保持性问题,是指存储在浮栅上的电荷保持有效而不泄漏的能力.随着闪存单元特征尺寸越来越小,在擦写电应力下,由于带带隧穿等效应会产生界面态和氧化层电荷/陷阱,因而导致越来越严重的可靠性问题[4].

负栅源擦除单元是在控制栅上加负偏置,在源极加正偏置,以达到擦除的目的.在这种采用 Fowler-Nordheim 擦除的结构中,源栅重叠区域由于表面电场导致带-带隧穿,从而产生空穴.这些空穴中的一部分获得足够的能量,成为热空穴.同样,写过程中也会产生热电子.这些热载流子具有较大的能量,在向氧化层注入时,会产生界面态和氧化层电荷

陷阱. 经过多次擦写后,热载流子注入引起的氧化层破坏将会非常严重. 这将产生氧化层应力诱生漏电流(stress induced leakage current, SILC)<sup>[5]</sup>,导致存储单元的特性退化.

本文研究了形成 SILC 的三种导电机制,并采用新的实验方法确定了引起 SILC 中稳态电流和瞬态电流的电压漂移量,进而利用电容耦合效应研究了低电场应力(读应力)下引起闪存特性退化的主要因素.

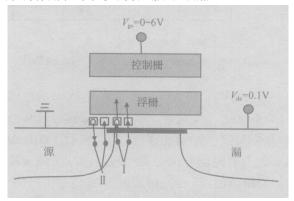

## 2 器件结构和参数

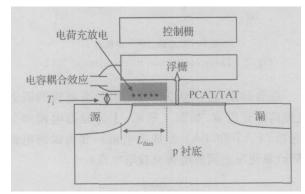

本研究采用的存储单元结构如图 1 所示,长 L = 3.  $2\mu$ m,宽 W =  $3\mu$ m. 隧道氧化层厚度  $T_{ox}$  = 10nm,介质氧化层采用氧氮氧 (ONO) 结构,厚度  $T_{ono}$  = 18. 5nm. 源和漏均采用金属双扩散 (MDD) 结构. 浮栅面积为 5.  $9\mu$ m × 8.  $0\mu$ m,控制栅面积为 5.  $5\mu$ m × 8.  $0\mu$ m,源和漏的 MDD 结构采用磷注入,注入剂量为 2. 5 ×  $10^{15}$  cm  $^{-2}$  ,能量为 35 keV; $n^+$  源和漏采用砷注入,剂量为 5 ×  $10^{15}$  cm  $^{-2}$  ,能量为 60 keV.

#### 3 SILC的三种导电机制及定量分析

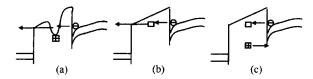

目前认为 SILC 有三种主要的导电机制[6,7]. 图

<sup>\*</sup>国家高技术研究发展计划(批准号:2004AA1Z1070)和国防预先研究计划(批准号:41308060305)资助项目 郑雪峰 男,1979年出生,博士研究生,主要从事超深亚微米器件可靠性研究.

郝 跃 男、1958年出生、教授、博士生导师、主要从事 MOS 器件可靠性和宽禁带半导体器件研究、

图 1 存储单元结构图

Fig. 1 Structure of flash memory cell

2(a) 示出了电子通过陷落的正电荷隧穿(PCAT), 图 2(b) 示出了电子通过中性电子陷阱隧穿(TAT), 图 2(c) 示出了载流子在氧化层陷阱里面充放电的 过程.

图 2 SILC 的三种导电机制

Fig. 2 Three conduction mechanisms of SILC

综合起来,可以认为 SILC 由稳态电流和瞬态电流两部分组成,如图 3 所示. 为稳态电流部分(包括 PCAT和 TAT 形成的电流), 为瞬态电流部分(氧化层里面的电荷充放电电流).

图 3 SILC 的稳态电流和瞬态电流

Fig. 3 Steady-state current and transient current of SILC

闪存可靠性的研究,必须定量分析 SILC 里面各部分电流的大小.

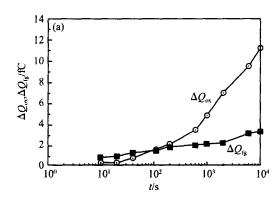

对于一个存储单元,在隧道氧化层上施加一定的电应力后测试单元的转移特性如图 4(a) 所示.可以得出应力前后闪存单元的阈值电压变化量  $V_{th}$ ,

它表示了图 2 中三种导电机制引起的总的阈值电压变化.

为了定量分析载流子充放电效应和 PCAT/TAT 各自的影响,必须对闪存单元应力前后的漏边GIDL 电流进行测量,如图 4(b)所示.在 GIDL 测试过程中,源极是悬浮的,因此应力引起的充放电效应可以忽略(因为在源边擦除过程中由于热空穴注入产生的氧化层陷阱电荷只存在于源极附近). GIDL实验的电压变化被记做 VGIDL,所以 VGIDL 仅仅是由于图 2 中 PCAT/TAT 效应引起的.那么 Vth与VGIDL 的差值,可以认为是由于源结附近载流子的充放电效应引起的.

图 4 V<sub>th</sub>和 V<sub>GIDL</sub>测试

Fig. 4 Measurement of  $V_{th}$  shift and  $V_{GIDL}$  shift

所以,通过测量应力前后  $V_{th}$ 和  $V_{GIDL}$ ,可以区分闪存存储单元氧化层里面载流子充放电效应和PCA T/ TA T 分别对 SILC 的贡献.

## 4 低电场应力(读应力)下退化特性

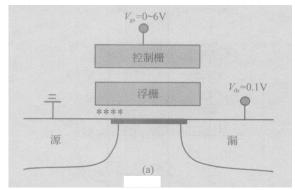

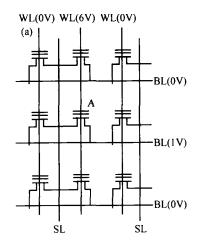

由于闪存单元经常处于读条件下,被读单元(图 5(a) 中单元 A) 的隧道氧化层承受了一定的电场应力,该电场相对于擦写情况被认为是低电场,下面讨论低电场下的退化特性.本文采用的是经过 5000 次

擦写操作后的样品. 所加的读应力为  $V_{\rm gs}=6{\rm V}$  ,  $V_{\rm ds}=1{\rm V}$  (隧道氧化层有效电场  $E_{\rm ox}=3{\rm MV/cm}$ ). 图 5 (b) 所示为读应力退化特性 ,图中曲线 a 表示一定的应力时间后闪存单元的  $V_{\rm th}$  ,曲线 b 表示 PCA T/ TA T 引起的闪存单元电压变化  $V_{\rm GIDL}$  ,曲线 c 表示从曲线 a 里面减去曲线 b 所得到的. 可以看出 ,总的  $V_{\rm th}$  随着应力时间的增加而增加 ,在经过  $10^4{\rm s}$  后达到  $0.33{\rm V}$ . PCA T/ TA T 引起的  $V_{\rm GIDL}$  (曲线 b) 很小,充放电引起的电压变化(曲线 c) 远远大于  $V_{\rm GIDL}$ . 因而可以得出,载流子的充放电是低场应力 (读应力)下引起失效的主要因素.

图 5 读单元及读应力下的电压漂移

Fig. 5 Read cell and voltage shift under reading stress

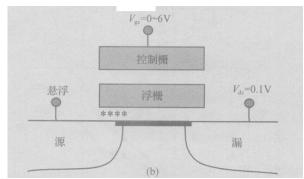

为了定量分析应力前后的电荷变化量,采用了电荷电容耦合效应模型<sup>[7]</sup>来分析低氧化层电场(读应力)下的失效现象,如图 6 所示,闪存中的载流子将通过电容耦合效应来引起阈值电压的变化.

根据电容耦合效应和电荷平衡方程,阈值电压的变化能被定量的推导出来,如下所示:

$$V_{\text{th,ox}} = \frac{C_{\text{ox}} + C_{\text{ono}}}{C_{\text{ox}} C_{\text{ono}}} Q_{\text{ox}}$$

(1)

$$V_{\text{th,fg}} = \frac{Q_{\text{fg}}}{C_{\text{ono}}}$$

(2)

式中  $V_{\text{th,ox}}$ 代表图 5 中的曲线 c(也即载流子的充电/放电);  $V_{\text{th,fg}}$ 代表曲线 b(也即 PCA T/ TA T);  $Q_{\text{ox}}$ 和  $Q_{\text{fg}}$ 分别代表氧化层和浮栅的电荷变化;  $C_{\text{ono}}$ 是控制栅和浮栅之间的电容;  $C_{\text{ox}}$ 代表损伤区的电容,表示为:

$$C_{\text{ox}} = C_{\text{ox}} \frac{L_{\text{dam}}}{L} \times \frac{T_{\text{ox}}}{T_{\text{ox}} - T_{\text{t}}}$$

(3)

式中  $C_{\rm x}$ 是闪存单元的隧道氧化层电容 ; $L_{\rm dam}$ 和  $T_{\rm t}$ 分别代表 Si/SiO<sub>2</sub> 界面上面损伤区域的长度和产生的隧道氧化层陷阱的深度. 其中 , $L_{\rm dam}$ 的值可以从栅二极管测试中得到 ,在这里采用  $L_{\rm dam}=0$ .  $2\mu$ m<sup>[8]</sup>. 考虑到  $T_{\rm t}$  的值会随器件的结构以及工作状态略有不同 ,参考一些文献 ,取其典型值  $T_{\rm t}=3$ nm<sup>[9]</sup>.

图 6 电容耦合效应示意图

Fig. 6 Illustration of capacitance coupling effect

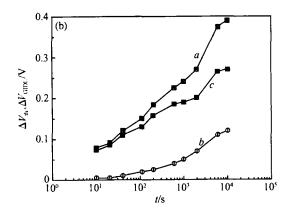

因为  $V_{\text{th,ox}}$ 和  $V_{\text{th,fg}}$ 能够从图 5 (b)的曲线中得到,那么电荷变化量  $Q_{\text{ox}}$ 和  $Q_{\text{fg}}$ 就可以从公式 (1) 和公式 (2) 中计算出来.图 7 (a)表示计算的  $Q_{\text{ox}}$ 和  $Q_{\text{fg}}$ 与时间的对应关系.显然, $Q_{\text{ox}}$ 是随着应力时间而增加的,而  $Q_{\text{fg}}$ 的增加量不是很大.这个现象可以解释为,在低的氧化层电场下,电子能够以很高的概率隧穿进入陷阱,但从陷阱隧穿出来的几率却很小.

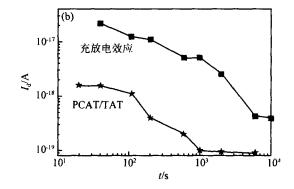

进而,通过 $\partial Q_{ox}/\partial t$  可以计算 SILC 中各部分电流的大小 $^{[10]}$ ,如图 7(b) 所示. 相比氧化层充放电效应 ,PCA T/TAT 引起的浮栅电荷量随时间的变化不大(图 7 中的  $Q_{fg}$ ) ,其形成的 SILC 电流就小得多. 因此 ,可以得出这样的结论 ,在低氧化层电场下 , 应力引起退化的主要机制是由载流子通过电容耦合

图 7 不同应力时间下的电量变化(a) 和泄漏电流(b) Fig. 7 Charge shift (a) and leakage current (b) under different stress times

效应在氧化层里充放电引起的.

#### 5 结论

本文研究了采用负栅源边擦除的存储单元出现的退化现象,在研究了形成应力诱生漏电流(SILC)的三种导电机制的基础上,采用新的实验方法定量测得了引起 SILC 中瞬态和稳态电流的电压漂移量.利用电容耦合效应模型对闪速存储器存储单元的可靠性进行了研究.结果表明,在低电场应力条件下,可靠性问题主要是由载流子在氧化层里充放电引起的.

#### 参考文献

- [1] Lu Yanxun ,Li Zhengxiao. Flash memory technology. Micro-processor ,1995 , 3:8 (in Chinese) [芦延勋,李正孝. Flash Memory 技术. 微处理机 ,1995 ,3:8]

- [2] Yang Hongguan, Shi Yi, L Win, et al. p-channel Ge/Si heteronanocrystal based MOSFET memory and its logic array. Chinese Journal of Semiconductors, 2004, 25(2):179(in Chinese) [杨红官, 施毅, 闾锦,等. p 沟道锗/硅异质纳米结构 MOSFET 存储器及其逻辑阵列. 半导体学报, 2004, 25(2):179]

- [ 3 ] Ou Wen, Qian He. SCDI flash memory device : simulation and analysis. Chinese Journal of Semiconductors, 2004, 25

(4):361

- [4] Chung S S, Yih C M, Cheng S M, et al. A new technique for hot carrier reliability evaluations of flash memory cell after long-term program/erase cycles. IEEE Trans Electron Devices, 1999, 46(9):1883

- [5] Iannaccone G, Crupi F, Neri B, et al. Theory and experiment of suppressed shot noise in stress-induced leakage current. IEEE Trans Electron Devices, 2003, 50(5):1363

- [6] Wang Tahui, Zous N K, Yeh C C. Role of positive charge in stress-induced leakage current for flash EERPOM devices. IEEE Trans Electron Devices, 2002, 49 (11):1910

- [7] Yih C M, Ho Z H, Liang M S, et al. Characterization of hothole injection induced SILC and related disturbs in flash memories. IEEE Trans Electron Devices, 2001, 48(2):300

- [8] Chung S S, Yih C M. A new oxide damage characterization technique for evaluating hot carrier reliability of flash memory cell after long-term program/erase cycles. Proc Symp VLSI Tech, 1997:111

- [ 9 ] Yokozawa A, Shirai H, Okazawa T, et al. Simulation for the degradation of flash memory due to charge trap in the tunnel oxide. Proc IEEE SISC, Charleston, SC, 1995, (12):44

- [10] Satoh S, Hemink G, Hatakeyama K, et al. Stress-induced leakage current of tunnel oxide derived from flash memory read-disturbed characteristics. IEEE Trans Electron Devices, 2002,45(2):482

# Degradation in Flash Memory Under Low Electric Field Stress

Zheng Xuefeng, Hao Yue, Liu Hongxia, and Ma Xiaohua

(Key Laboratory of the Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, Microelectronics Institute, Xidian University, Xi'an 710071, China)

**Abstract:** Based on the negative gate source side erased flash memory cell, three conduction mechanisms causing stress induced leakage current are studied. The voltage shifts which cause steady state and transient currents are measured by new experimental methods. The reliability of flash memory cells is investigated using the capacitance coupling effect model. The results show that the cell reliability under a low electric field stress is mainly affected by the carriers charging and discharging inside the oxide.

Key words: flash memory; stress induced leakage current; low electric field stress; capacitance coupling effect

**PACC**: 7200J; 7300 **EEACC**: 2810D **Article ID**: 0253-4177 (2005) 12-2428-05

<sup>\*</sup>Project supported by the National High Technology Research & Development Program of China(No. 2004AA1Z1070) and the National Defence Pre-Research Foundation of China(No. 41308060305)

Zheng Xuefeng male, was born in 1979, PhD candidate. He is engaged in research on the reliability of UDSM devices.

Hao Yue male, was born in 1958, professor and adviser of PhD candidates. He is engaged in research on the reliability of MOS devices and wide bandgap semiconductor devices.