# n型 4H-SiC MOS 电容的特性

### 宁 瑾 刘忠立 高见头

(中国科学院半导体研究所 微电子中心, 北京 100083)

摘要: 在 n 型 4H-SiC 外延层上,采用 H₂,O₂ 合成的办法,热生长 30nm 的 SiO₂ 层,并制备出 Al 栅 MOS 电容,完 成了 C-V 特性的测试和分析工作,根据测试结果得出了  $SiO_2$  与 4H-SiC 外延层的界面特性,并计算出 n 型 4H-SiC外延层的掺杂浓度. 结果表明  $H_2$ ,  $O_2$  合成热生长的  $SiO_2$  与 4H-SiC 外延层之间具有较好的界面特性,界面态密度 较小, n 型 4H-SiC 外延层的掺杂均匀,浓度为  $1.84 \times 10^{17}$  cm<sup>-3</sup>.

关键词: 4H-SiC; MOS 电容; C-V 特性; 热生长 SiO2

**EEACC**: 2520M; 2530F; 7310B

中图分类号: TN304.2+4 文献标识码: A 文章编号: 0253-4177(2005)S0-0140-03

### 1 引言

SiC 是新型宽禁带化合物半导体材料,具有许 多优越的性能,如带隙宽、热导率高、击穿场强高、饱 和速度高,适合制作高温大功率、高温高频以及抗辐 射器件[1],这样的器件在发动机、核电站、石油钻井 及空间技术中具有广泛的用途,因此从上世纪60年 代开始,世界各发达国家就开始了对 SiC 材料和器 件的研究工作,近几年来,我们国家也开始涉足该领 域, 热生长的二氧化硅与衬底之间的界面特性明显 优于淀积的二氧化硅, Si MOSFET 器件就是采用 热生长的二氧化硅作为栅介质,在化合物半导体材 料中,SiC 材料是惟一能够直接形成热生长二氧化 硅的材料,因此 SiC MOSFET 一直被认为是具有较 大发展潜力和优势的新型化合物半导体器件. 热生 长 SiO<sub>2</sub>-SiC 界面特性的研究工作非常重要,是 SiC MOSFET 研制工作的前提条件和重要组成部分. 在 本文中,我们在 n型 4H-SiC 外延层上制备出 MOS 电容,进行了C-V特性测试与分析工作,着重针对 热生长 SiO<sub>2</sub>-SiC 界面特性和 n 型 4H-SiC 外延层的 掺杂浓度进行了分析和计算. 本文的工作为下一步 制备 SiC 器件奠定了基础.

#### 实验 2

衬底选用 Cree 公司的 n+型 SiC 材料,晶向为 (0001),掺杂浓度为 3×10<sup>18</sup> cm<sup>-3</sup>,采用 LPCVD 方 法外延生长 n-型 SiC 材料,外延层掺杂浓度约为 10<sup>17</sup> cm<sup>-3</sup>,厚度约为 1μm. 对外延结构材料清洗以 后,在 1100 °C 下,采用  $H_2$ ,  $O_2$  合成的办法进行栅氧 氧化, 经椭偏仪测试, 氧化层厚度为 30nm 左右, 采 用电子束蒸发的办法,双面蒸发 500nm 的 Al 作为 MOS 电容的两个电极,电容的正面电极为圆形,直 径为 280 μm.

### 3 结果与讨论

#### 3.1 4H-SiC MOS 电容 C-V 特性测试与分析

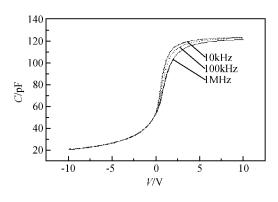

C-V 特性的测量仪器为 HP4275 LCR 测试仪, 偏压扫描速率为 0.1V/s,首先在常温下测试了 4H-SiC MOS 电容的 C-V 特性,测试频率分别为 10, 100 和 1MHz,测试曲线如图 1 所示. 从图 1 给出的 C-V 曲线中能清楚地看出积累、耗尽和深耗尽区域. 样品加负偏压时,进入深耗尽状态,这是因为在覆盖 整个偏压的时间内,在耗尽层中产生的电子空穴对 远小于形成强反型层所需要的电荷量,半导体的屏 蔽电荷只能是耗尽层电荷,耗尽层的宽度将不再保持平衡状态,而是随偏压增加. 主要是由于 SiC 的热产生率极低所致,室温下,偏压加在反型区,耗尽区的电荷可能需要几年到几十年才能达到平衡. 图 1 中不同的测试频率得到的三条 C-V 曲线比较一致,通常对于 Si MOS 电容来说,在 10kHz 的频率下,测试出的 C-V 曲线为低频 C-V 曲线,而我们在 10kHz 的频率下,测试出 4H-SiC MOS 电容的 C-V 曲线仍然为高频 C-V 曲线. 这点有可能是因为外延层的掺杂浓度较高(达到  $10^{17}$  cm $^{-3}$ )所致,同时也可以说明 SiC 的热产生率低,耗尽层中电子空穴对的产生率远低于 Si. 测试曲线接近理想 C-V 曲线,平带电压接近零,略向右漂移. 因此可以认为,采用  $H_2$ , $O_2$  合成的办法生长的 SiO<sub>2</sub> 与 SiC 的界面较好,可以制备 MOS 器件.

图 1 n 型 4H-SiC MOS 电容的 C-V 特性

Fig. 1 C-V plots of n type 4H-SiC MOS capacitor

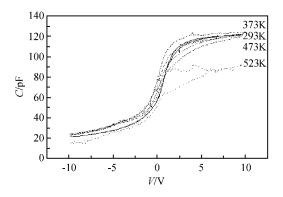

由于 SiC 材料是热导率高的宽禁带半导体,适合制作高温器件,所以本文也测试分析了其在不同温度下的高频 CV 特性,以观察其热稳定性,测试结果如图 2 所示. 从图中可以看出,在 293,373 和473K 时,CV 曲线比较接近,但温度升高以后,正扫曲线和反扫曲线之间出现迟滞,可能是由于氧化层中界面附近的陷阱与半导体通过隧穿交换电荷引起<sup>[2]</sup>. 当温度升高到 523K 时,CV 曲线发生变化,积累区的电容值明显下降,分析原因如下:测试的MOS 电容采用 Al 栅,而  $SiO_2$  层比较薄,仅为30nm,当温度升高后,Al 原子有可能通过氧化层隧穿入半导体中,而且温度升高也导致本征载流子浓度变大,少数载流子的产生率增加,界面态及慢态的俘获和发射也随之增加,总之,界面态密度明显增加. 如果将 Al 栅改为多晶硅栅,SiC MOS 电容的温

度特性将会改善.

图 2 不同温度下 n型 4H-SiC MOS 电容的 C-V 特性 Fig. 2 C-V plots of n type 4H-SiC MOS capacitor at different temperatures

#### 3.2 4H-SiC 外延层杂质浓度的计算

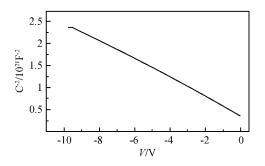

利用 MOS 电容的高频 CV 曲线,从 CV 特性耗尽区的斜率可以计算出 4H-SiC 外延层杂质浓度<sup>[3]</sup>. 这种方法与其他方法相比(如金属半导体接触势垒电容法等)具有以下两个特点:其一是可测衬底氧化以后的掺杂浓度. 由于热氧化过程中硅表面的杂质会发生再分布,因而用此法测得的杂质浓度更能反映制成器件后的实际情况. 其二,用 CV 特性测得的杂质浓度是器件有源工作区内的浓度,对器件参数的设计与控制更有现实意义.

MOS 结构归一化电容  $C/C_{ox}$  在耗尽区的斜率  $d/dV_G(C/C_{ox})$ 与衬底杂质浓度  $N_A$  的关系为[ $^{3}$ ]:

$$\frac{\mathrm{d}}{\mathrm{d}V_{\mathrm{G}}} \left( \frac{C}{C_{\mathrm{ox}}} \right) = -\left( \frac{C}{C_{\mathrm{ox}}} \right)^{3} \frac{\varepsilon_{\mathrm{ox}}^{2}}{\varepsilon_{\mathrm{s}} q d_{\mathrm{ox}}^{2} N_{\mathrm{A}}} \tag{1}$$

式中 C 为 MOS 电容值;  $C_{ox}$  为氧化层电容;  $V_{G}$  为外加偏压;  $\epsilon_{ox}$  为氧化层介电常数;  $\epsilon_{s}$  为 SiC 介电常数;  $d_{ox}$  为氧化层厚度;  $N_{A}$  为 SiC 外延层掺杂浓度; q 为基本电荷.

把上式化简,可以得到如下简化公式:

$$N_{\rm A} = \frac{2}{q\varepsilon_{\rm s} \frac{\mathrm{d}(1/C^2)}{\mathrm{d}V_{\rm o}} A^2} \tag{2}$$

式中 A 为 MOS 电容的面积. 从(2)式可以看出,只要确定了  $1/C^2-V$  的斜率,就可以计算出 4H-SiC 外延层掺杂浓度  $N_A$ . 利用 1MHz 频率下测得的 C-V 特性曲线,只取耗尽区域,将其变换为  $1/C^2-V$  曲线,如图 3 所示. 图 3 中直线更进一步地说明了 4H-SiC 外延层与热生长  $SiO_2$  的界面特性较好,且外延层掺杂浓度较为均匀,适合制备 SiC 器件. 把该直线

的斜率代入公式(2),可算出外延层掺杂浓度为  $1.84 \times 10^{17} \, \mathrm{cm}^{-3}$ .

图 3 1MHz 频率下 n 型 4H-SiC MOS 电容的  $1/C^2$  -V 特性曲线

Fig. 3 C-V plot of n type 4H-SiC MOS capacitor in the frequency of 1MHz

### 4 结论

本文在 n 型 4H-SiC 外延层上,采用  $H_2$ , $O_2$  合成的办法,热生长 30nm 的  $SiO_2$  层,并制备出 Al 栅 MOS 电容,在不同温度和频率条件下完成了 C-V 特性的测试和分析工作. 结果表明热生长的  $SiO_2$  与 4H-SiC 外延层之间具有较好的界面特性,界面态密

度较小,适于制备 4H-SiC MOS 器件. 在 473K 的高温下,MOS 电容仍然具备基本的 C-V 特性,从而验证了 4H-SiC 可以用来制备高温器件的特性. 最后根据 1MHz 频率下 C-V 测试结果计算出 4H-SiC 外延层的掺杂浓度为  $1.84 \times 10^{17}$  cm<sup>-3</sup>,4H-SiC 外延层掺杂浓度均匀,适于作为沟道层制备 MESFET 器件. 本文的工作为 SiC 电子器件的研制奠定了基础.

致谢 本文制备 MOS 电容所用的 n 型 4H-SiC 外延层由中国科学院半导体研究所材料中心的孙国胜老师制备提供,在此致以衷心的感谢!

### 参考文献

- [1] Sriram S, Augustine G, Burk A A, et al. 4H-SiC MESFET's with 42GHz  $f_{\rm max}$ . IEEE Eeletron Device Lett, 1996, 17(7): 369

- [2] Wang Shurui, Liu Zhongli, Liang Guirong, et al. Electrical characterization of n-type 6H-SiC MOS capacitors. Chinese Journal of Semiconductors, 2001, 22(6); 755(in Chinese) [王 殊春,刘忠立,梁桂荣,等. N型 6H-SiC MOS 电容的电学特性,半导体学报,2001,22(6); 755]

- [3] Guo Weilian. The interface physics of Si-SiO<sub>2</sub>. Beijing: National Defense Industry Press, 1989; 6 (in Chinese) [郭维廉. 硅-二氧化硅界面物理.北京;国防工业出版社,1989;6]

## Electrical Characteristics of n-Type 4H-SiC MOS Capacitor

Ning Jin, Liu Zhongli, and Gao Jiantou

(Microelectronics R&D Center, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China)

**Abstract:** Al gate MOS capacitor is fabricated using thermally oxidized 30nm SiO<sub>2</sub> layer grown on n type 4H-SiC epitaxial layer by synthesizing  $H_2$  and  $O_2$ . The C-V characteristics are measured and analysed. According to the results, the interface feature of SiO<sub>2</sub>-SiC and doping concentration of the n type 4H-SiC epitaxial layer are obtained. The interface has quite good quality and the interface state density is small. The doping concentration of uniform n type 4H-SiC epitaxial layer is  $1.84 \times 10^{17} \, \text{cm}^{-3}$ .

Key words: 4H-SiC; MOS capacitor; C-V characteristics; thermally oxidized SiO<sub>2</sub>

EEACC: 2520M; 2530F; 7310B

**Article ID**: 0253-4177(2005)S0-0140-03

Ning Jin female, was born in 1976, PhD, assistant professor. Her main research field is in novel semiconductor devices. Email: ningjin@red. semi. ac. cn