# Analysis on Characteristic of Static Induction Transistor Using Mirror Method

Hu Dongqing, Li Siyuan, and Wang Yongshun

(Institute of Static Induction Device, School of Physical Science and Technology, Lanzhou University, Lanzhou 730000, China)

**Abstract :** A cylindrical gates model of the static induction transistor is proposed and mirror method is used to calculate the distribution of electric potential. The results show that :the potential barrier is directly determined by channel over pinchedoff factor ;gate efficiency decreases as the gate dimension <sub>2</sub> and shifted gate voltage are minished ,and what differs from the first-order theory is that will tend to zero at the shifted gate voltage tends to zero when  $V_D = 0$ ; at low current ,the voltage amplification factor  $\mu$  increases as the drain current rising. When the drain current reaches certain degree ,the voltage amplification factor keeps almost constant. In the end ,an analytical description of SIT 's characteristic suited to both triode-like and mixed *FV* characteristics are obtained. The predicted *FV* curves are consistent perfectly with the reported experimental ones.

Key words : static induction transistor ; mirror method ; *I-V* characteristic

PACC : 0239P

CLC number : TN32

Document code : A

Article ID : 0253-4177 (2005) 02-0258-08

### 1 Introduction

Since static induction transistor (SIT) was reported in  $1972^{[1]}$ , many works have been done for its structure optimization<sup>[2~7]</sup>, but the theoretical studies on its working mechanism have always been lagged behind practical researches.

SIT is a kind of structurally sensitive device. Its electric parameters and I-V characteristics depend strongly on its structural parameters (such as channel length, channel thickness, etc.), material parameters (such as channel doping concentration), and biasing voltage ( $V_D$  and  $V_G$ ). Generally, SIT 's I-V characteristics exhibit triode-like, pentode-like, and mixed between triode- and pentode-like ones. In the past thirty years, some analyses have been done for the basic theoretical model of  $SIT^{[8~10]}$ . Bulucea and Rusu followed Shockley 's JFET analytical model and proposed a first-order theory of the  $SIT^{[8]}$ . Strollo and Spirito developed a self-consistent model using the voltage-doping transformation (VDT) approach<sup>[9]</sup>. All these results fit well to the triode-like *I-V* characteristic ,but ill-suited to the mixed one.

Our purpose of this work is to (1) propose a cylindrical gates model, work out the distribution of electric field using mirror method, and give a fundamental insight into the mechanisms involved in SIT operation under low biasing voltages; (2) provide a general I-V equation, which is suitable for both of triode-like and mixed I-V characteristics under unipolar SIT operation.

Wang Yongshun male, PhD candidate. He is interested in technology and theory of static induction devices.

Received 26 June 2004 , revised manuscript received 3 September 2004

Hu Dongqing female, PhD candidate. She is interested in technology and theory of static induction devices. Email : hudq02 @st.lzu.edu.cn

Li Siyuan male, professor, advisor of PhD candidates. His research fields include microelectronics, solid-state electronics, silicon devices, and static induction devices.

#### 2 Model structure

SIT has many types of structure. In this paper we will focus on buried-gate one.

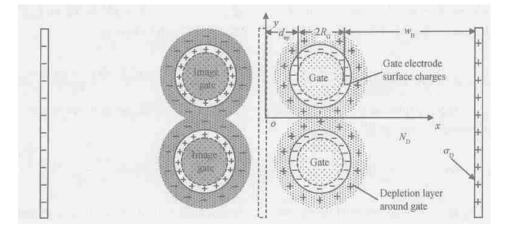

For simplicity, we hypothesize that the gates are cylindrical. The sketched structure of SIT is shown in Fig. 1 (right part). The channel depletion region around the gate and surface charges on the electrodes are also depicted in Fig. 1.

Fig. 1 Analyzing model of SIT

The drain electrode far from the gates is heavily dopped ,and the drain surface charge can be regarded as uniform distribution. Also ,the study is focused on the channel ,we can group the net charges in the long base area with two heads :one is under the depletion layer around the gates ;the other is attributed to drain surface charge. Being very close to the gates, the source surface charge can be equivalent to a group of image gates whose polarity is opposite to and whose volume is equal to the gates and their surrounding depletions by using mirror method. Considering charge conversation law , the image drain surface charge should also be calculated. On all these accounts , the analytical

Table 1 Structural and material parameters of device

| Parameter definition                       | Notation       | Value                             |

|--------------------------------------------|----------------|-----------------------------------|

| Channel doping concentration               | ND             | $10^{14} \text{cm}^{-3}$          |

| Gate doping concentration                  | NA             | 10 <sup>19</sup> cm <sup>-3</sup> |

| Source doping concentration                | n <sub>s</sub> | $10^{19} \text{cm}^{-3}$          |

| Center distance between two adjacent gates | d              | 20µm                              |

| Width of the long base                     | wB             | 200µm                             |

| Radius of the cylindrical gate             | R <sub>G</sub> | 6µm                               |

| Thickness of the secondary epitaxial layer | $d_{\rm ep}$   | 6µm                               |

model used in this paper is shown in Fig. 1. The main structural dimension and material parameters are given in Table 1.

#### **3** Potential distribution

Under different biasing voltages, the device can be split into three (the channel is not pinched off) or four subregions (the channel is pinched off) —gate zone, electrical neutral zone, depletion zone, and depletion-overlapped zone. Considering the symmetry and using superposition principle of the electric field, we can obtain

(1) In gate zone,  $(d_{ep} - x)^2 + (d/2 - y)^2$

$R_{\rm G}^2$ , the gates can be regarded as an equipotential bulk :

$$\Phi(x, y) = V_{\rm G} - \Phi_{\rm BO} \tag{1}$$

where  $\phi_{BO} = V_{T} \ln \frac{N_{A} N_{D}}{n_{i}^{2}}$  is gate-channel build-in voltage,  $V_{G}$  is gate voltage.

(2) In electrical neutral zone,  $(d_{ep} - x)^2 + (d/2 - y)^2 = R_C^2$ , all charges of electrode and depletion region are contributed to the electric field.

$$\Phi_{1}(x, y) = \frac{-D}{x} + \frac{-G}{4} \ln \left[ \frac{\left(\frac{d_{ep} - x}{d_{ep} + x}\right)^{2} + \left(\frac{nd - y}{d_{ep} + x}\right)^{2}}{\left(\frac{d_{ep} - x}{d_{ep} + x}\right)^{2} + \left(\frac{nd - y}{d_{ep} + x}\right)^{2} + \left(\frac{nd + y}{d_{ep} + x}\right)^{2}} \right]$$

(2)

where D is surface charge density of drain electrode,

$_{\rm G} = _{\rm G}$  -  $_{\rm C}$  is general linear density (along z axis) of the gate-channel depletion charge,  $_{\rm G}$  is linear density (along z axis) of the gate surface charge,  $_{\rm C} = qN_{\rm D}$  ( $R_{\rm C}^2 - R_{\rm G}^2$ ) is linear density (along z axis) of channel depletion charge,  $d_{\rm ep} = d_{\rm ep} + R_{\rm G}$ . (3) In depletion zone ,only part of depletion zone charge affects the electric field. This involves two cases: depletion overlapped and nonoverlapped. For nonoverlapped region ,i.e. that of  $R_{\rm G}^2$   $(d_{\rm ep} - x)^2 + (d/2 - y)^2$   $R_{\rm C}^2$  and  $(d_{\rm ep} - x)^2 + (d/2 + y)^2$   $R_{\rm C}^2$ , having :

+  $(d/2 + y)^2$   $R_{\rm C}^2$  are met, we have:

$$\Phi_{2}(x, y) = \Phi_{1}(x, y) + \frac{qN_{\rm D}}{4}R_{\rm C}^{2}\left[\ln\frac{(d_{\rm ep} - x)^{2} + (d/2 - y)^{2}}{R_{\rm C}^{2}} + 1 - \frac{(d_{\rm ep} - x)^{2} + (d/2 - y)^{2}}{R_{\rm C}^{2}}\right]$$

(3)

(4) For overlapped depletion region ,i.e. that  $R_G^2$ ( $d_{ep} - x$ )<sup>2</sup> + (d/2 - y)<sup>2</sup>  $R_C^2$  and ( $d_{ep} - x$ )<sup>2</sup>

$$\Phi_{3}(x, y) = \Phi_{2}(x, y) + \frac{qN_{\rm D}}{4}R_{\rm C}^{2}\left[\ln\frac{(d_{\rm ep} - x)^{2} + (d/2 + y)^{2}}{R_{\rm C}^{2}} + 1 - \frac{(d_{\rm ep} - x)^{2} + (d/2 + y)^{2}}{R_{\rm C}^{2}}\right] \quad (4)$$

where  $_{G, D}$ , and  $R_{C}$  can be determined by boundry conditions , i.e.

$$\frac{d \Phi(0,0)}{d x} = 0,$$

$$\phi(w,0) = V_{\rm D},$$

$$\phi(d_{\rm ep}, d/2) = V_{\rm G} - \phi_{\rm BO}$$

$$w_{\rm B} + 2 R_{\rm G} + d_{\rm ep}.$$

(5)

### 4 Barrier height $\phi_{\min}$

where w =

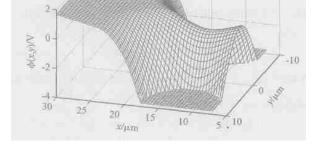

Figure 2 shows a 2D plot of the potential distribution in the device for  $V_D = 20V$  and  $V_G = -3V$ . In order to manifest the potential distribution along y-

Fig. 2 Two-dimension distribution of the potential obtained from our model for  $V_D = 20V$  and  $V_G = -3V$

axis, we start from  $x = 7\mu$ m. It is very clear that a channel barrier occurs along the channel axis and its position  $x_{\min}$  can be obtained by

$$\frac{\mathrm{d}\,\phi(x,0)}{\mathrm{d}\,x} = 0 \tag{6}$$

When the channel exists in neutral region ,equation (6) has no solution. This indicates that the barrier control mechanism occurs only when the channel is pinched off. Also ,the barrier position is the function of biasing voltages. When  $V_{\rm D} = 0$  ,it is at the center of channel. If  $V_{\rm D}$  is not equal to zero ,it will fluctuate from the channel center. We obtain

$$x_{\min} = (1 - ) d$$

(7)

where

$$=\frac{B_{1} - \sqrt{B_{1}^{2} - 4(A_{6} + 4A_{3} - 4A_{4})(A_{3} - A_{4})}}{2(A_{6} + 4A_{3} - 4A_{4})}$$

(8)

It is a fluctuation from the channel center due to the static induction effect.  $B_1 = A_5 + \frac{qN_D d^2}{V_D} (^2 + 2) (A_1 + _3A_3)$  is a parameter related to the device structure and biasing voltages,  $_1 = \frac{d_{ep}}{d}, A_1 = \frac{1}{n + 1/2} \left( \frac{(3 - 1)^2 + n^2}{(3 + 1)^2 + n^2} \right), \quad A_3 = \frac{4}{n + 1/2} \frac{4}{1 + n^2},$  $A_4 = \frac{4}{n + 1/2} \frac{4}{1 + 1/2}, \quad A_5 = \frac{2}{n + 1/2} \left( \frac{2}{n^2} - \frac{2}{4} \frac{1}{1 + n^2} \right) + \frac{4}{1 + n^2} + \frac{4}{$

$$A_{n=1/2}\left(\frac{4}{4},\frac{1}{1}+n^2\right)^2$$

,  $A_6 = \frac{8}{n=1/2}\frac{4}{(4},\frac{2}{1}+n^2)^2$  are parameters are parameters.

rameters related to device structure.  $\frac{R_{\rm C} - d/2}{d/2}$  is channel over pinched-off factor.

Substitute Eq. (7) into Eq. (4), we can obtain the barrier height,

$$\Phi_{\min} = \frac{V_{D} \left[ \frac{\ln \frac{2}{(2_{1} - \frac{1}{2})^{2} + n^{2}} + A_{3}(1_{1} - \frac{1}{2})}{A_{1} + \frac{1}{3}A_{3}} + \frac{\frac{qN_{D}}{2}R_{C}^{2}(\ln \frac{4^{2} + 1}{(1 + \frac{1}{2})^{2}} + 1 - \frac{4^{2} + 1}{(1 + \frac{1}{2})^{2}}) \right]$$

(9)

where  $_3 = w/d$  is a parameter related to device structure.

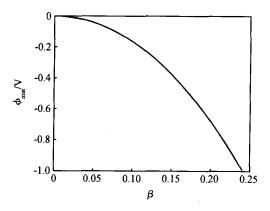

Figure 3 gives the relationship of barrier height and channel over pinched-off factor under zero voltage of drain. It shows that the potential barrier is directly determined by channel over pinched-off factor. Meanwhile it is necessary of channel deep pinched-off for the forming of barrier high enough to control the drain current.

Fig. 3 Relationship of potential barrier height  $\phi_{min}$  and channel over pinch-off factor under zero drain voltage

## 5 Gate efficiency and voltage amplification factor µ

Noting that  $\frac{\partial \phi_{\min}}{\partial} = -d \frac{\partial \phi(x_{\min}, 0)}{\partial x} = 0$ , the gate efficiency and voltage amplification factor  $\mu$  can be obtained:

$$= \frac{\partial \phi_{\min}}{\partial V_{G}} = \frac{(-+1)\ln((1+-)^{2}/(4^{-2}+1))}{[1 - \ln(2_{-2})] - \ln(2_{-2})}$$

(10)

$$\boldsymbol{\mu} = \left( \begin{array}{c} \mathbf{1} & \mathbf{x} \frac{\partial \phi_{\min}}{\partial V_{D}} \right)^{-1} \\ = \left( \begin{array}{c} \ln \frac{2 + n^{2}}{(2 - 1 - 2)^{2} + n^{2}} + A_{3}(1 - 2) + n^{2} +$$

Equations (10) and (11) are the function of biasing voltages and rely on gate dimension  $_2$  directly.  $_2 = \frac{R_G}{d}$ ,  $A_2 = \lim_{n=1} \ln \frac{(2 + 1 - 2)^2 + n^2}{2 + n^2} + \ln \frac{2 + 1 - 2}{2}$  are the perpendicular related to the device structure.

the parameters related to the device structure.

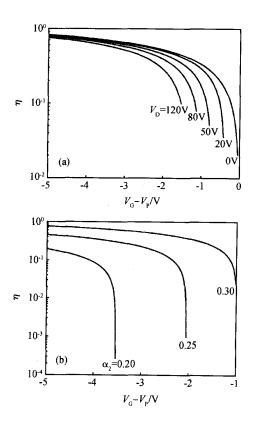

Figure 4 gives the dependences of gate efficiency on shifted gate voltage ( $V_{\rm G}$  -  $V_{\rm P}$ ) under different drain voltages and gate dimensions. Here  $V_{\rm P}$  is pinched-off gate voltage for  $V_{\rm D} = 0$ :

Fig. 4 Dependences of the gate efficiency on the shifted gate voltage under different drain voltages  $V_D$  and different gate dimension  $_2$  (a) Under different drain voltages for the same  $_2$ ; (b) Under different gate dimension for the same  $V_D$

$$V_{\rm P} = \frac{qN_{\rm D}d^2}{16} \times (1 - 4 \ {}^2_2 + 2\ln(2 \ {}_2)) + \phi_{\rm BO} \quad (12)$$

Figure 5 shows that will decrease when the gate dimension 2 and shifted gate voltage become less. This result is similar to that of the first-order theory<sup>[8]</sup>. What differs from the first-order theory is that will tend to be zero when the shifted gate voltage tends to zero under zero drain voltage. This indicates once more that it is essential of the channel over pinched-off for the barrier control mechanism.

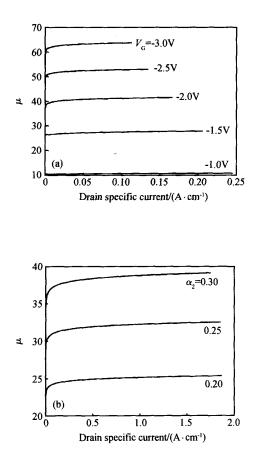

Fig. 5 Dependences of the voltage amplification factor  $\mu$  on the drain specific current under different  $V_{\rm G}$  and  $_2$  (a) Under different gate voltages for the same  $_2$ ; (b) Under different gate dimension for some

Figure 5 also gives the dependences of voltage amplification factor  $\mu$  on specific current of drain under different gate voltage and gate dimensions. At low drain current, the voltage amplification factor  $\mu$  increases as the drain current rising. When the drain current reaches certain ralue, the voltage amplification

factor keeps almost constant. This agrees with the experimental results obtained from buried gate SIT<sup>[1]</sup>.

#### 6 I-V characteristic

The current density along channel axis can be obtained by the following current continuity equation:

$$j_{n} = q\mu_{n} n(x) E(x) + D_{n} \frac{dn(x)}{dx}$$

$$= qD_{n} \left(\frac{E(x)}{V_{T}} n(x) + \frac{dn(x)}{dx}\right) \qquad (13)$$

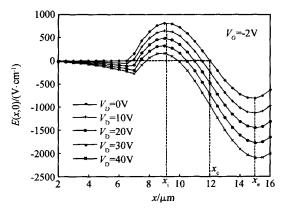

The electric field strength along channel axis is given in Fig. 6. Around the center of the channel ,the field is nearly linear variation. Considering  $E(x_{\min}, 0) = 0$ , letting :

$$E(x,0) - V_{T-1}(x - x_{\min})$$

(14)

Fig. 6 Electric field strength along channel axis

From Eqs. (13) and (14) ,we can obtain :

$$n(x) = \left\{ \int_{2-1}^{1} \frac{i_n}{\sqrt{qD_n}} Q(\sqrt{-1/2}(x - x_{\min})) + n_0 \right\} \times e^{1(x - x_{\min})^2/2}$$

(15)

where  $n_0$  is electron concentration at the barrier (E = 0). It is determined by the boundary condition. Using Boltzmann approximation ,we have :

$$n_0 = n(x_{\min}) = n_{\rm s} e^{\phi_{\min}/V_{\rm T}}$$

(16)

Q is error function,  $_{1} = \frac{(A_3 - A_4) V_{\rm D}}{(A_1 + _3A_3) d^2 V_{\rm T}(_1 - )}$ is a new introduced parameter.

At the end of the channel (that is  $x = x_e$ , see

Fig. 6) ,drift field is so high that the carriers are hard to accumulate, so the carrier concentration gradient inclines to zero. Then we can obtain :

$$j_{\rm n} = -qD_{\rm n} \left( \sqrt{\frac{2}{1}} Q \left( \sqrt{\frac{1}{2}} \left( x_{\rm e} - x_{\rm min} \right) \right) + \frac{e^{-1} \left( x_{\rm e} - x_{\rm min} \right)^2 / 2}{1 \left( x_{\rm e} - x_{\rm min} \right)} \right)^{-1} n_{\rm s} e^{\phi_{\rm min} / V_{\rm T}}$$

(17)

Following the analysis reported in Ref. [10], the effective half channel thickness  $a_{\text{eff}}$  can be written as

$$a_{\rm eff} = \frac{I_{\rm n}}{2 j_{\rm n} w_{\rm t}} = \int_{0}^{y_2} \exp\left(\frac{\phi(x_{\rm min}, y) - \phi_{\rm min}}{V_{\rm T}}\right) dy$$

(18)

where  $I_n$  is the drain current,  $w_t$  is the total width of channel,  $y_2$  is half minimum of cross section of channel. Then

$$2 a_{\text{eff}} = \sqrt{B_5} dQ \left( \frac{\sqrt{B_3} y_1}{d} \right) + \sqrt{B_4} d \times \left( Q \left( \sqrt{B_4} \left( \frac{y_2}{d} + \frac{B_5}{B_4} \right) \right) - Q \left( \sqrt{B_4} \left( \frac{y_1}{d} + \frac{B_5}{B_4} \right) \right) \right)$$

(19)

where  $y_1 = \sqrt{R_C^2 - (d_{ep} - x_{min})^2} - \frac{d}{2}$ ,  $y_2 = \frac{d}{2} - \sqrt{R_G^2 - (d_{ep} - x_{min})^2}$ ,  $B_2 = \frac{A_5 V_D / V_T}{2(A_1 + A_3)}$ ,  $B_3 = B_2 + \frac{2 q N_D}{V_T} (R_C^2 + \frac{d^2}{4})$ ,  $B_4 = B_2 + \frac{q N_D}{V_T} (R_C^2 + \frac{d^2}{4})$ ,  $B_5 = \frac{q N_D}{V_T} (R_C^2 - \frac{d^2}{4})$  are parameters related to the device structure and biasing voltages.

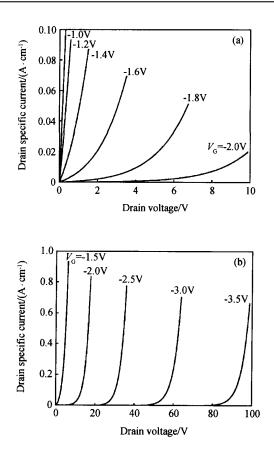

Using above equations, the I-V characteristics under different gate voltages are obtained and shown in Fig. 7:(a) is a typical group of mixed I-V characteristic curves and (b) is a group of triode-like ones.

The error function has the properties of Q(x) $\frac{x-3}{2}1$  and  $Q(x)\frac{x-0}{2}0$ . If the reverse gate voltage is high, the channel is deep pinched off,  $\frac{\sqrt{B_3 y_1}}{d} = 3$ and  $\sqrt{\frac{1}{2}}(x_e - x_{\min}) = 3$  are met, Equations (17) and (19) can be simplified to

$$j_{\rm n} - qD_{\rm n} \sqrt{\frac{2}{N}} n_{\rm s} e^{\phi_{\rm min}/V_{\rm T}}$$

(20)

$$2 a_{\rm eff} = \sqrt{\frac{2}{B_3}} d \left( \frac{2 qN_{\rm D}}{V_{\rm T}} \left( R_{\rm C}^2 + \frac{d^2}{4} \right) \right)^{-1/2} d$$

(21)

Fig. 7 Calculated *FV* characteristic of SIT (a) Mixed characteristics under lower gate voltage; (b) Triode-like characteristics under higher gate voltages

Then

$$I_{\rm n} = 2 w_{\rm t} q D_{\rm n} \sqrt{1 - \frac{d^2/2}{R_{\rm C}^2 + d^2/4}} n_{\rm s} e^{\phi_{\rm min}/V_{\rm T}}$$

$$= I_0 e^{\phi_{\rm min}/V_{\rm T}}$$

(22)

where the pre-exponential factor  $I_0 = 2 w_t q D_n \times \sqrt{1 - \frac{d^2/2}{R_c^2 + d^2/4}} n_s$  (the so called saturation current)

is almost constant with  $V_D$ .

If channel pinched off degree is low,

$$Q(\sqrt{1/2}(x_{e} - x_{\min})) \ll \frac{e^{-1(x_{e} - x_{\min})^{2}/2}}{1(x_{e} - x_{\min})} - \frac{1}{E_{\max}}$$

and  $\sqrt{B_4} \frac{y_1}{d} = 0$ , Euquations (17), (19) and drain current can be simplified to

$$j_{\rm n} \quad q\mu_{\rm n} E_{\rm max} n_{\rm s} {\rm e}^{\phi_{\rm min}/V_{\rm T}}$$

(23)

$$2 a_{\text{eff}} \approx \sqrt{B_4} d \qquad \sqrt{B_2} d \qquad (24)$$

$$I_{\rm n} - w_{\rm t} q \mu_{\rm n} n_{\rm s} e^{\phi_{\rm min} / V_{\rm T}} \frac{A_{5} V_{\rm T} V_{\rm D}}{\sqrt{3(A_{1} + 3A_{3})}}$$

(25)

From Eqs. (20), (22), (23), and (25), we can see that, when the pinched-off degree of channel is deep, the current flowing through the channel is mainly by diffusion, the so called saturation current is almost constant with  $V_D$ , the device exhibits exponential *I-V* characteristics; when the pinched-off degree of channel is low, the current flowing through the channel is mainly by drifting, the so called saturation current is almost 1/2 power with  $V_D$ , the device exhibits mixed *I-V* characteristics.

#### 7 Conclusion

Basing on cylindrical gates model, the distribution of channel potential has been calculated directly by mirror method. Two opposite action fields in the channel are obtained and the saddle resembled potential distribution is gotten. In addition, we have proposed the concept of channel over pinch-off factor and pointed out definitely that it is essential that the channel over pinched-off for the barrier control mechanism. Moreover, the forming of potential barrier relies on channel over pinched-off ;and the controlling of barrier height lies in channel over pinched-off factor.

Meanwhile, the gate efficiency and voltage amplification factor are given. Both of them are gate dimension  $_2$  related parameters. The more  $_2$  is, the more and  $\mu$  are.

Though this model is under the assumption that the channel overlapped depletion zone is much less than the total depletion zone, it still has great help to understand the mechanism of SIT. It works well for the analysis of the SIT which has mixed I-V characteristics. And using this model, we have presented a group of  $I \cdot V$  characteristic curves, which fits quite well to the experimental result published up to now<sup>[1~3]</sup>. This confirms further that our model is correct and available.

#### References

- [1] Nishizawa J , Terasaki T , Shibata J . Field-effect transistor versus analog transistor (static induction transistor). IEEE Trans Electron Devices ,1975 ,22 (4) :185

- [2] Li S Y, Zhang T J, Jia X T, et al. A static induction transistor with insulator covered-gate and with triode-like *I-V* characteristics. Solid State Electron, 1990, 33 (3) :345

- [3] Nishizawa J. The 2.45 GHz 36W CW Si recessed gate type SIT with high gain and high voltage operation. IEEE Trans Electron Devices ,2000 ,47 (2) :482

- [4] Bencuya I, Cogan A I, Butler S J, et al. Static induction transistor optimized for high-voltage operation and high microwave power putput. IEEE Trans Electron Devices, 1985, 32(7):1321

- [5] Baliga B J. High-voltage junction-gate field-effect transistor with recessed gates. IEEE Trans Electron Devices, 1982, 29 (10):1560

- [6] Wang Yongshun, Li Siyuan, Hu Dongqing. A microwave high power static induction transistor with double dielectrics gate structure. Chinese Journal of Semiconductors, 2004, 25(1):19

- [7] Wang Yongshun, Liu Su, Li Siyuan, et al. Electrical performance of static induction transistor with mixed *I-V* characteristics. Chinese Journal of Semiconductors, 2004, 25 (3):266

- [8] Bulucea C, Rusu A. A first-order theory of the static induction transitor. Solid State Electron, 1987, 30(12):1227

- [9] Strollo A G M. Trade-off between blocking gain and on-resistance in static induction transistor. Solid State Electron, 1995, 38 (2):309

- [10] Yamamoto T, Matsumoto K, Yusa A. Analysis of SIT FV characteristics by two-dimensional simulation. Solid State Electron, 1987, 30(5):549

## 镜像法分析静电感应晶体管特性

#### 胡冬青 李思渊 王永顺

(兰州大学物理科学与技术学院 静电感应器件研究所, 兰州 730000)

摘要:针对埋栅型静电感应晶体管(SIT)提出一种柱栅模型.用镜像法计算了器件内电势分布,并在此基础上计算 了沟道势垒、栅效率、电压放大因子等.结果表明:沟道势垒直接取决于沟道过夹断因子;栅效率随栅尺寸和位移栅 压的减小而减小,并随位移栅压一起趋向于0;在小电流情况下电压放大因子随电流的增大而增大,到一定数值后, 电压放大因子趋于常数.最后给出了SIT *FV* 特性解析表达式,它既适用于类三极管特性(加大栅压下)也适用于 混合特性(较小栅压下),且由此得到的 *FV* 特性曲线和实验符合较好.

关键词:静电感应晶体管;镜像法; FV 特性

PACC: 0239P

中图分类号: TN32

文献标识码: A

文章编号: 0253-4177(2005)02-0258-08

2004-06-26 收到,2004-09-03 定稿

胡冬青 女,博士研究生,研究方向为静电感应器件的工艺和理论.

李思渊 男,教授,博士生导师,研究领域为微电子学、固体电子学、硅器件和静电感应器件.

王永顺 男,博士研究生,研究方向为静电感应器件的工艺和理论.