## A Systematical Approach for Noise in CMOS L NA

#### Feng Dong and Shi Bingxue

(Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

**Abstract :** A systematic approach is used to analyze the noise in CMOS low noise amplifier (LNA) ,including channel noise and induced gate noise in MOS devices. A new analytical formula for noise figure is proposed. Based on this formula ,the impacts of distributed gate resistance and intrinsic channel resistance on noise performance are discussed. Two kinds of noise optimization approaches are performed and applied to the design of a 5. 2 GHz CMOS LNA.

Key words: amplifier noise; channel noise; channel resistance; induced gate noise; low noise amplifier; noise op-

timization EEACC: 1205; 1220 CLC number: TN402

Document code : A

Article ID: 0253-4177 (2005) 03-0487-07

### 1 Introduction

The progress in CMOS process makes it possible to integrate more functions on one chip, including radio frequency front-end and digital signal processing back-end. WLAN (wireless local area network) transceiver is one of these digital communication systems, which connects laptops and other mobile terminals to ethernet backbone through AP (access point). As MAC (media access control) part of WLAN transceiver is implemented in CMOS technology, it is appealing to implement the RF front-end circuit in the same technology. It is promising to integrate the whole system on a single chip.

As the first critical component of the receiver, low noise amplifier (LNA) should sufficiently amplify the weak RF signal coming from antenna and duplexer with as less distortion and noise as possible. From the Friis noise equation<sup>[11]</sup>, the noise figure of the receiving system is dominated by the noise contribution of the first stage or two.

The source inductive degeneration configuration is widely used for LNA due to its superior

noise performance<sup>[2]</sup>. This LNA architecture has been analyzed<sup>[3]</sup> especially on noise performance. There are three main noise sources, which should be taken into consideration to fully appreciate the noise performance. One is the noise associated with the distributed gate resistance and other losses in series with the gate; the others are induced gate noise and channel noise in submicron MOS devices due to hot electron effects. The analysis in Ref. [3] dealt with the contribution of each noise source separately, thus the interactions among these components were neglected. The correlation between induced gate noise and channel noise was not treated rigidly in mathematics. The induced gate noise was simply split into two components, one of which is fully correlated with the channel noise and the other is uncorrelated with the channel noise<sup>[3]</sup>. Although this technique simplified the analysis, it was just a conjecture without proof. Only the amplitude of the correlation coefficient, which is a complex number, was considered. As frequency approaching cut-off frequency  $f_{\rm T}$ , the gate impedance of the MOS device exhibits a significant phase shift from its purely capacitive value at lower frequencies. In the RF applications, the channel of MOSFET must be viewed as a bias dependent RC distributed transmission line<sup>[4]</sup>. To model the finite time needed to build up the channel charge, one way is to insert a noiseless equivalent resistors  $R_{ch}$  in series with the gate capacitors  $C_{gs}$  and  $C_{gd}$ , respectively<sup>[5]</sup>. The existence of  $R_{ch}$  was verified through simulation and measurement<sup>[6]</sup>. Meanwhile  $R_{ch}$  complicates the analysis of noise figure, and its effect on noise performance was dropped out<sup>[3]</sup>. This was noted in Ref. [7], but the analysis there is a simple extension of the results in Ref. [3] and is not accurate and rigor in mathematics.

To fully appreciate the noise performance of CMOS LNA, a comprehensive analysis is presented in this paper. The noise performance of source inductive degeneration CMOS LNA is analyzed and a new analytical formula for noise figure is derived. Two approaches of noise optimization are performed with respect to fixed transconductance gain  $G_m$  and fixed power dissipation  $P_D$ , respectively, and they are applied in the design of a 5. 2 GHz CMOS LNA.

## 2 CMOS L NA noise analysis

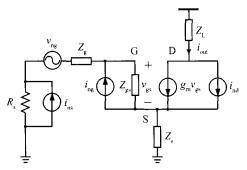

The CMOS LNA analyzed here is the source inductive degeneration architecture (Fig. 1) for its superior noise performance and prevalence.

Fig. 1 Source inductive degeneration LNA architecture

To perform a comprehensive noise analysis of the LNA with a systematic approach, a generic small-signal model of source inductive degeneration LNA is used. The small-signal model is shown in Fig. 2. The parasitic components between gate and drain are not shown in Fig. 2 ,as there are methods (such as cascode configuration) to improve reverse-isolation.  $Z_g$  denotes the impedance in series with the gate.  $Z_{gs}$  is the impedance between the gate and the source including parasitic  $C_{gs}$  and channel resistance  $R_{ch}$ .  $Z_s$  and  $Z_L$  are the source degeneration and load impedances of the LNA , respectively.  $g_m$  is the transconductance of the MOS device.

Fig. 2 Generic small-signal model for LNA noise analysis

$i_{ns}$  is the noise current source associated with source resistance  $R_s$ . Three main noise sources are fully considered here.  $v_{ng}$  is the noise voltage source associated with gate impedance  $Z_g$  which includes distributed gate resistance and other parasitic losses. In RF CMOS circuits, transistors are commonly implemented with multi-finger gate layout. The PSD (power spectral density) of  $v_{ng}$  is given by

$$\overline{v_{ng}^2} = 4kT \frac{R_g}{3} f \tag{1}$$

where the factor of 1/3 is due to the distributed effect of the gate resistance, assuming the fingers are only contacted at one end<sup>[8]</sup>. If both ends are contacted, the factor is reduced to 1/12. *i*<sub>nd</sub> is channel noise source, which is the dominant noise source in MOS device. *i*<sub>nd</sub> is white noise, the PSD of which is given by

$$i_{\rm nd}^2 = 4 k T g_{\rm d0} f$$

(2)

where is a bias-dependent factor, and  $g_{d0}$  is the zero-bias drain conductance of the MOS device.  $i_{ng}$  is induced gate noise source, the PSD of which is given by<sup>[9]</sup>

$$\overline{i_{ng}^2} = 4kT \frac{2C_{gs}^2}{5g_{d0}} f$$

(3)

where is the coefficient of gate noise. This equation is valid when the device is operated in saturation.  $i_{ng}$  is induced by the fluctuations in the channel charge due to capacitive coupling when MOS device is biased so that the channel is inverted. Thus  $i_{ng}$  and  $i_{nd}$  are partially correlated, and the correlation coefficient is given by<sup>[9]</sup>

$$c = \frac{i_{\rm ng} i_{\rm nd}^{\star}}{\sqrt{i_{\rm ng}^2 i_{\rm nd}^2}} \tag{4}$$

where asterisk (\*) indicates the conjugate of complex number. It is worth noting that the choice of directions of correlated noise sources has effect on the phase of the correlation coefficient c. The value of c for long-channel devices is 0. 395j.

Applying the noisy two-port network based analysis outlined in Ref. [10], the input impedance and noise factor F of the source degeneration LNA are given by

$$Z_{in} = Z_g + Z_{gs} + Z_s + g_m Z_{gs} Z_s$$

(5)

$$F = 1 + \frac{v_{ng}}{R_{s}^{2}} + |A|^{2} \frac{\frac{i_{ng}}{r_{s}^{2}}}{i_{ns}^{2}} + |A|^{2} \frac{\frac{i_{ng}}{r_{s}^{2}}}{i_{ns}^{2}} + |A|^{2} \frac{\frac{i_{ng}}{r_{s}^{2}}}{i_{ns}^{2}} + 2 \frac{Re(AB^{*} - i_{ng} i_{nd})}{i_{ns}^{2}}$$

(6)

$$A = 1 + \frac{Z_{g} + Z_{s}}{R_{s}}$$

$$B = \frac{1}{g_{m} Z_{gs}} \left( 1 + \frac{Z_{g} + Z_{gs} + Z_{s}}{R_{s}} \right)$$

where it is assumed that  $v_{ng}$  is uncorrelated with  $i_{nd}$ and  $i_{ng}$ . It is worth noting that the load impedance  $Z_L$  does not appear in the noise factor expression, because the reverse path between gate and drain has been disregarded.

For the source inductive degeneration LNA considered here, the explicit expressions for  $Z_g$ ,  $Z_{gs}$ , and  $Z_s$  are

$$\begin{cases} Z_{g} = j L_{g} + R_{g} \\ Z_{gs} = R_{ch} + \frac{1}{j C_{gs}} \\ Z_{s} = j L_{s} \end{cases}$$

(7)

where  $R_g$  includes the distributed gate resistance and loss of inductor  $L_g$ .  $R_{ch}$  is the noiseless equivalent channel resistance to model the deviation of gate impedance of MOS device from its purely capacitive value at lower frequencies as operating frequency approaching T. The expression of  $R_{ch}$  is

$$R_{\rm ch} = \frac{1}{5 g_{\rm d0}}$$

(8)

assuming that operating frequency 0 satisfies

$$_{0} \ll \frac{5_{T}}{2} \tag{9}$$

with the definition that

$$=\frac{g_{\rm m}}{g_{\rm d0}}\tag{10}$$

Note that is always less than one.

From Eq. (5), the impedance matching input and the corresponding resonant frequency  $_0$  are determined by

$$R_{s} = R_{g} + R_{ch} + g_{m} \frac{L_{s}}{C_{gs}}$$

$$0 = \frac{1}{\sqrt{C_{gs} \left[ L_{g} + L_{s} \left( 1 + \frac{1}{5} \right) \right]}}$$

(11)

The impact of neglecting  $R_{ch}$  on input impedance matching and intended operating frequency can be appreciated from Eq. (11).

Substituting Eqs. (1) ~ (4) and (7) into Eq. (6) ,the noise factor F of source inductive degeneration LNA can be explicitly given by

$$F = 1 + F_{1} + F_{2} + F_{3} + F_{4}$$

$$F_{1} = \frac{R_{g}}{3R_{s}}$$

$$F_{2} = \left(\frac{-0}{T}\right)^{2} \frac{g_{d0}^{2}}{5R_{s}} \left[\left(R_{s} + R_{g}\right)^{2} + \frac{2}{0}\left(L_{g} + L_{s}\right)^{2}\right]$$

$$F_{3} = \frac{g_{d0}^{2}\left(\frac{-0}{T}\right)^{2}}{1 + \left(\frac{-0}{T}\right)^{2} \frac{2}{25}} \times \frac{\left(R_{s} + R_{g} + R_{ch}\right)^{2} + \frac{2}{0}L_{s}^{2}\frac{2}{25}}{R_{s}}$$

$$F_{4} = \left\{\frac{\left(\frac{-0}{T}\right)^{2}g_{m}^{2}}{1 + \left(\frac{-0}{T}\right)^{2} \frac{2}{25}} \left[\left(R_{s} + R_{g}\right)^{2} + \frac{2}{0}\left(L_{g} + L_{s}\right)^{2}\right] - \frac{L_{g} + L_{s}}{L_{g} + L_{s}\left(1 + \frac{-5}{5}\right)}\right\} \times \frac{2/c}{g_{m}R_{s}} \sqrt{5} \qquad (12)$$

$F_1$  is due to the distributed gate resistance only where the noise contribution of loss in  $L_g$  has been disregarded.  $F_2$  and  $F_3$  are attributed to induced gate noise and channel noise ,respectively.  $F_4$  is due to the correlation between induced gate noise and channel noise. During the derivation ,some assumptions have been made

$$C = / c / j$$

(13)

From the explicit noise factor expression, it is clear that gate resistance  $R_{\rm g}$  increases noise factor through  $F_2$ ,  $F_3$ , and  $F_4$  in addition to its direct contribution to F. This has been ignored in the previous work<sup>[3,7]</sup>, where the noise sources are treated individually for simplicity. Multi-finger gate layout and salicide CMOS process can alleviate this plague without power penalty. Another conclusion is that  $L_{g}$  should be implemented with bond wire and external high-Q inductor instead of on-chip spiral inductor if lower NF is desirable ,because the loss of on-chip spiral inductor is larger. Even if on-chip spiral inductor is used for higher integration, the AC coupling capacitor at the RF input should be implemented with external component. Rch also increases the noise factor only through  $F_3$ . It is clear that improvement of T of MOS devices will improve the noise performance. The negative term in the braces of  $F_4$  is due to the impact of inductance  $(L_g \text{ and } L_s)$  on the correlation between induced gate noise and channel noise. This can not be overlooked in this complicated case for accurate estimation of F, which has not been predicted in the previous literatures<sup>[3,7]</sup>.

# 3 Optimization of CMOS L NA noise performance

To simplify the expression for F and gain more insight on noise optimization,  $R_g$  in F is omitted except for  $F_1$  and a new variable Q is defined as

$$Q = \frac{0(L_{g} + L_{s})}{R_{s} + R_{g}} \frac{0(L_{g} + L_{s})}{R_{s}} \frac{1}{0 C_{gs} R_{s}}$$

(14)

After tedious algebraic manipulations, noise factor F can be denoted as

$$F = 1 + \frac{R_{g}}{3R_{s}} + \frac{-0}{T} \left\{ Q + \frac{1}{Q} \left( + - \right) + \frac{2}{5} \times \frac{-0}{T} \right\} - \frac{2/d}{g_{m}R_{s}} \int_{5}^{-1} (15)$$

$$= \frac{-0}{5} + \left( \frac{-0}{T} \right)^{2} \times \frac{2}{25} + 2/d \int_{5}^{-1} \sqrt{5}$$

Based on the new expression for F, noise performance of CMOS LNA can be optimized. The optimization presented here is different from the conventional procedure detailed in Ref. [11], which based on the parameters of a fixed device the source impedance is transformed to a noise optimum impedance by an impedance matching network. Thus the input power matching and noise matching may not occur at the same time. For CMOS LNA design, the size and bias of device are under the control of designers. Noise performance can be optimized by seeking optimum device size or bias to minimize noise factor for a design parameter, such as power or gain, under the condition of perfect input power matching.

A simple second-order model of MOS transistor is used to optimize the noise performance, which accounts for high-field effects in short-channel devices<sup>[12]</sup>.

$$I_{\rm d} = W C_{\rm ox} v_{\rm sat} \frac{V_{\rm od}^2}{V_{\rm od} + L_{\rm sat}}$$

(16)

where  $V_{od}$  is the overdrive voltage,  $C_{ox}$  is the gate oxide capacitance per unit area,  $v_{sat}$  is the saturation velocity, <sub>sat</sub> is the velocity saturation field strength, and W and L are channel width and length, respectively. The definition of  $V_{od}$  is

$$V_{\rm od} = V_{\rm gs} - V_{\rm T} \tag{17}$$

where  $V_{T}$  is the threshold voltage of the transistor. Thus the device transconductance  $g_{m}$  is given by

$$g_{\rm m} = \frac{\partial I_{\rm d}}{\partial V_{\rm gs}} = \frac{3 v_{\rm sat}}{_0 L R_{\rm s} Q}$$

(18)

with the definition that

$$=\frac{V_{\rm od}}{L_{\rm sat}}$$

(19)

Substituting Eq. (18) into (15) , noise factor F can be rewritten as

$$F = 1 + \frac{R_{\pi}}{3R_{s}} + \frac{-0}{T} \left\{ Q \left[ -\frac{2/c/L_{T}}{3v_{sat}} + \frac{1}{\sqrt{5}} \right] + \frac{1}{Q} \left[ + - \right] + \frac{2}{5} \times \frac{-0}{T} \right\}$$

(20)

To optimize the noise performance of the LNA, it is useful to formulize the quantities , T, and Q.

$$=\frac{2+}{2(1+)^2}$$

(21)

$${}_{\rm T} \quad \frac{g_{\rm m}}{C_{\rm gs}} = \frac{3v_{\rm sat}}{2L} \times \frac{(2+)}{(1+)^2}$$

(22)

$$Q = \frac{3}{2 \circ WL C_{\rm ox} R_{\rm s}}$$

(23)

It is clear that all quantities in Eq. (20) except for Q depend on bias voltage. Q depends on device width. The input circuit of the LNA takes the form of a series-resonant network and the output current is proportional to the voltage on  $Z_{gs}$ . At the resonant frequency  $_{0}$ , the input power matching is achieved and the transconductance gain  $G_{m}$  of the LNA is

$$G_{\rm m} = g_{\rm m} Q_{\rm in} \left(1 + j \circ R_{\rm ch} C_{\rm gs}\right)$$

=  $g_{\rm m} \frac{1 + j \circ R_{\rm ch} C_{\rm gs}}{\circ C_{\rm gs} \left[R_{\rm s} + R_{\rm g} + R_{\rm ch} + g_{\rm m} \frac{L_{\rm s}}{C_{\rm gs}}\right]}$

=  $\frac{T}{2 \circ R_{\rm s}} \left[1 + j \frac{\circ}{T} \times \frac{1}{5}\right]$  (24)

where  $Q_{in}$  is the effective quality factor of the LNA input circuit. Here the influence of channel resistance  $R_{ch}$  on the transconductance gain  $G_m$  has been considered, which was ignored in Ref. [7]. It is clear that to fix the value of transconductance gain  $G_m$ , (or  $V_{od}$ ) should be assigned a constant value. Once is determined,  $G_m$  is determined and noise factor F can be minimized for fixed  $G_m$  by choosing the appropriate device width. The optimum noise factor for fixed  $G_m$  optimization is

$$F_{\min, G_{m}} = 1 + \frac{R_{g}}{3R_{s}} + \frac{-0}{T} \times \left\{ 2 \sqrt{\left( -\frac{2/c/L}{3v_{sat}} + \sqrt{5} \right)} \left( + - \right) + \frac{2}{5} \times \frac{0}{T} \right\}$$

$$(25)$$

The corresponding  $Q_{opt}$  for  $F_{\min, G_m}$  is determined by

$$Q_{\text{opt}} = \frac{+-}{\sqrt{-\frac{2/c/L_{-T}}{3\nu_{\text{sat}}}}}$$

(26)

Further the device width corresponding to  $F_{\min,G_m}$  can be obtained through Eqs. (23) and (26).

From the expression of  $I_d$ , the power dissipation of the LNA is formulated as

$$P_{\rm D} = V_{\rm dd} I_{\rm d} = \frac{P_0}{Q} \times \frac{2}{+1}$$

$$P_0 = \frac{3V_{\rm dd} v_{\rm sat}}{2_0 R_{\rm s}}$$

(27)

where  $V_{dd}$  is the power supply voltage for the LNA. It is worth noting that  $P_0$  is a constant determined by intended design specs ( $V_{dd}$ ,  $_0$ , and  $R_s$ ) and physical technological parameters ( $v_{sat}$  and sat). The corresponding power dissipation for  $F_{\min,G_m}$  can be determined from Eqs. (26) and (27).

An alternative of fixed  $G_m$  noise performance optimization fixes the power dissipation  $P_D$  and adjusts bias (or  $V_{od}$ ) to find the minimum noise factor. It is instructive to recast the noise factor in  $P_D$ and .

$$F = 1 + \frac{R_{e}}{3R_{s}} + \frac{-n}{T} \left[ \frac{P_{0}}{P_{D}} \times \frac{2}{+1} \left( -\frac{2/c/L}{3v_{sat}} + \sqrt{5} \right) + \frac{P_{0}}{P_{0}} \times \frac{+1}{2} \left( + - \right) + \frac{2}{5} \times \frac{-n}{T} \right]$$

(28)

The noise factor F is minimized for a fixed  $P_{\rm D}$  when

$$\frac{\partial F}{\partial} = 0 \tag{29}$$

The solution to this equation is too complex to be given in a closed form for fixed  $P_D$  noise optimization. But in a specific design, the optimum bias point can be determined numerically.

#### 4 **Results**

The noise performance of a CMOS LNA working at 5. 2 GHz frequency band is investigated applying the work presented in the previous sections. The technology used is TSMC 0. 25µm 3. 3V mixed-signal CMOS process. The physical technological parameters of this process are that  $L = 0.35\mu$ m,  $V_T = 0.55$ V,  $C_{ox} = 4.86 \times 10^{-3}$  F/m<sup>2</sup>,  $v_{sat} =$

1. 05 ×10<sup>5</sup> m/s, and  $\mu_{eff} = 0.03 \text{ m}^2/(\text{V} \cdot \text{s})$ . Power supply  $V_{dd} = 3.3 \text{V}$  and source resistance  $R_s = 50$ . Parameters c, ,and are bias dependent, while /  $= 2^{[13,14]}$ . Here the assumption that c = 0.395j and = 1.3 is reasonable. As  $R_g$  can be reduced by multi-finger gate layout and salicide process, its effect has not been included in the results below.

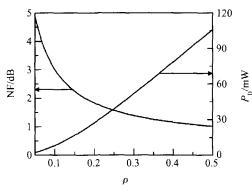

For fixed  $G_m$  optimization, the curve of optimum NF versus is shown in Fig. 3. In the design process of LNA, bias voltage (or  $V_{od}$ ) of the device can be determined from the noise requirement. The corresponding device width is found from Eq. (26). As usually power is another important concern, to appreciate the tradeoffs among NF, and  $P_D$ , the corresponding  $P_D$  is also shown in the same figure. It makes sense that the optimum NF decreases with the increasing at the cost of more power dissipation. In practical design, only the portion where <0.3 is useful.

Fig. 3 Optimum NF for fixed  $G_m$  optimization and corresponding  $P_D$  versus

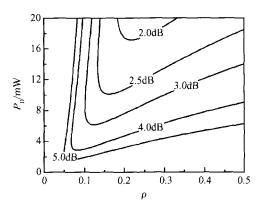

Fixed  $P_D$  optimization is more useful in practical LNA design. The contours of constant noise figure relating and  $P_D$  are useful to reveal the design tradeoffs among gate overdrive ,power dissipation and noise figure ,which are shown in Fig. 4. In the practical design process of LNA ,the bias voltage and device width can be determined from the requirements of both noise and power graphically.

#### 5 Conclusion

The noise performance of LNA is crucial for the sensitivity of receiver. All kinds of noise

Fig. 4 Contours of constant NF relating and  $P_D$  for fixed  $P_D$  optimization

sources and components complicate the analysis of noise performance. A systematic approach based on noisy two-port network theory to analyze the noise performance of CMOS LNA is presented in this paper. A new analytical noise figure formula is proposed. Channel noise and induced gate noise in MOS devices are rigidly treated in mathematics.

Investigating the new noise figure formula reveals that distributed gate resistance and other losses in series with the gate have both direct and indirect contributions to the noise figure, which was not obtained in the previous work<sup>[3,7]</sup>. The impact of channel resistance  $R_{ch}$  is evaluated fully for frequency approaching T. Both the input impedance matching and the intended operating frequency are affected by this resistance. This resistance also increases the noise contribution of channel noise to noise figure. The correlation between induced gate noise and channel noise in MOS devices is manipulated rigidly to result in a negative term in the noise figure. This negative term is due to the impact of inductors on the correlation between induced gate noise and channel noise.

For a second-order model of MOS transistor that accounts for high-field effects in short-channel devices, noise optimization of CMOS LNA is performed. The optimization is to minimize the noise figure by seeking the appropriate bias voltage or device width for a design parameter, such as power or transconductance gain, under the condition of perfect input impedance matching. The results of fixed  $G_m$  optimization and fixed  $P_D$  optimization are applied to the design of a 5. 2 GHz CMOS LNA using the TSMC 0. 25µm 3. 3V mixed signal CMOS process.

The comprehensive analysis and optimization of CMOS LNA noise performance presented in this paper will benefit the design of high performance LNA, as the design tradeoffs among noise figure, power dissipation and overdrive voltage are revealed quantificationally and visually.

#### References

- Friis H T. Noise figures of radio receivers. Proceedings of the IRE,1944,32(7):419

- [2] Gramegna G,Magazzu A, Sclafani G, et al. Ultra-wide dynamic range 1. 75dB noise-figure ,900MHz CMOS LNA. Digest of Technical Papers of ISSCC ,2000:380

- [3] Shaeffer D K, Lee T H. A 1. 5V, 1. 5GHz CMOS low noise amplifier. IEEE J Solid-State Circuits, 1997, 32(5):745

- [4] Tsividis Y. Operation and modeling of the MOS transistor.

2nd ed. Boston: WCB/ Mc Graw- Hill ,1998

- [5] Chan M, Hui K Y, Hu C, et al. A robust and physical BSIM3 non-quasi-static transient and AC small-signal model for circuit simulation. IEEE Trans Electron Devices, 1998, 45 (4): 834

- [6] Tsui H Y,Lau J. SPICE simulation and tradeoffs of CMOS LNA performance with source-degeneration inductor. IEEE Trans Circuits and Systems : Analog and Digital Signal Processing, 2000, 47(1):62

- [7] Chen J, Shi B. Impact of intrinsic channel resistance on noise performance of CMOS LNA. IEEE Electron Device Lett, 2002,23(1):34

- [8] Razavi B, Yan R H, Lee K F. Impact of distributed gate resistance on the performance of MOS devices. IEEE Trans Circuits and Systems :Fundamental Theory and Applications, 1994, 41(11):750

- [9] Van der Zel A. Noise in solid state devices and circuits. New York: Wiley, 1986

- [10] Feng D, Shi B. A 2. 5-V 2. 45/5. 25 GHz dual-band CMOS LNA. Proceedings of 5th International Conference on ASIC, 2003:1110

- [11] Gonzalez G. Microwave transistor amplifiers : analysis and design. 2nd ed. Upper Saddle River, N.J. : Prentice Hall, 1997

- [12] Einspruch N G. VLSI electronics : microstructure science. New York : Academic Press ,1981

- [13] Goo J S, Choi C H, Morifuji E, et al. RF noise simulation for submicron MOSFET 's based on hydrodynamic model. Symposium on Digest of Technical Papers of VLSI Technology, 1999:153

- [14] Goo J S, Choi C H, Danneville F, et al. An accurate and efficient high frequency noise simulation technique for deep submicron MOSFETs. IEEE Trans Electron Devices, 2000, 47 (12):2410

# CMOS 低噪声放大器中噪声的系统研究方法

#### 冯 东 石秉学

(清华大学微电子学研究所,北京 100084)

摘要:采用系统研究方法来分析包括 MOS 器件的沟道噪声和感应栅噪声在内的 CMOS 低噪声放大器中的噪声, 并提出了一个新的噪声系数解析式.基于此解析式,讨论了分布栅电阻和内部沟道电阻对噪声性能的影响.对噪声 性能进行了两种不同的优化,并应用于 5.2 GHz CMOS 低噪声放大器的设计.

关键词:放大器噪声;沟道噪声;沟道电阻;感应栅噪声;低噪声放大器;噪声优化 EEACC:1205;1220 中图分类号:TN402 文献标识码:A 文章编号:0253-4177(2005)03-0487-07