# Compact Threshold Voltage Model for FinFETs<sup>\*</sup>

Zhang Dawei, Tian Lilin, and Yu Zhiping

(Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

**Abstract :** A 2D analytical electrostatics analysis for the cross-section of a FinFET (or tri-gate MOSFET) is performed to calculate the threshold voltage. The analysis results in a modified gate capacitance with a coefficient *H* introduced to model the effect of tri-gates and its asymptotic behavior in 2D is that for double-gate MOSFET. The potential profile obtained analytically at the cross-section agrees well with numerical simulations. A compact threshold voltage model for FinFET, comprising quantum mechanical effects, is then proposed. It is concluded that both gate capacitance and threshold voltage will increase with a decreased height, or a decreased gate-oxide thickness of the top gate ,which is a trend in FinFET design.

Key words:FinFET; 2D analytical electrostatic analysis; compact model; threshold voltagePACC:7340Q; 6185; 0300CLC number:TN304.02Document code:Article ID:0253-4177 (2005) 04-0667-05

1 Introduction

DGMOSFET and FinFET appear to be two of the most promising device structures<sup>[1~4]</sup> substituting current MOSFET beyond 65nm regime due to the electrostatic concern (i. e. off-state leakage current). Compact analytical modeling for these new structures is in order in anticipation of technology maturity. There have been active work on the compact modeling for DGMOSFET, e. g. in Refs. [5 ~ 8]. However, analytical model for FinFETs is so far not seen yet, and it is critical to provide IC designers one because of FinFET 's strong gate control capability and thus superior performance.

In this paper, a compact model for threshold voltage of FinFETs is presented based on 2D analytical electrostatic-analysis for the cross-section of a FinFET, comprising quantum mechanical effects. This compact model has the following two features: (1) since the derivation is fully physicsbased, there are no fitting parameters and the analytical electrostatic potential profile agrees well with the numerical results; (2) the relation between device parameters and gate capacitance and threshold voltage are in explicit form, which makes it convenient to analyze the effect of the surrounding gate (both sides and on top) on device characteristics. It is concluded that gate capacitance and the threshold voltage increase with a decreasing height of channel slab and a decreasing gate-oxide thickness of the top gate.

### 2 Modeling and results

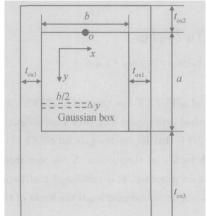

First of all ,for the convenience of discussion ,a diagram of the cross-section of a FinFET is plotted in Fig. 1. In our notation , a is the height of the silicon channel region , b is the width of the channel region ,  $t_{ox1}$  is the double side-gate (both front and

<sup>\*</sup> Project supported by National High Technology R &D Program of China (No. 2003AA1Z1370)

Zhang Dawei male, was born in 1980, master candidate. His major interest is compact modeling for novel physical effects in nanoscaled devices. Email:zdw99 @mails.tsinghua.edu.cn

Received 7 September 2004, revised manuscript received 12 November 2004

t<sub>ox2</sub> Gaussian box

Fig. 1 Cross-section of FinFET x is the direction along width while y is the direction along height. The origin of the 2D coordinate is set at o.

In Ref. [5], considering 1D electrostatics within the channel of a DG MOSFET, the following expression of surface electron density  $n_{\rm e}$  is obtained.

$$n_{\rm e} = 2 C_{\rm g} \left( V_{\rm G} - \Phi_{\rm c} \right) / q \qquad (1)$$

$$C_{\rm ex} C_{\rm d} / \left( C_{\rm ex} + C_{\rm d} \right) \text{ represents the gate}$$

where  $C_g = C_{ox} C_d / (C_{ox} + C_d)$  represents the gate capacitance per unit area with  $C_{\text{ox}} = \frac{1}{100} \text{ / } t_{\text{ox}}$  the oxide capacitance per unit area ( ox is oxide permittivity,  $t_{ox}$  gate-oxide thickness of a DG-MOSFET) and  $C_d$ = 4 si/d the depletion capacitance per unit area (si is silicon permittivity, d is width of a DGMOS-FET).  $V_{\rm G} = V_{\rm G} - (\Phi_{\rm M} - + V_{\rm A} - V_{\rm D})$  is the effective gate voltage with  $\Phi_M$  of the work function of the gate material, of the electron affinity of the semiconductor,  $V_{\rm A} = qn_{\rm A}/2C_{\rm g}$  (n<sub>A</sub> is acceptor density per unit area) and  $V_{\rm D} = qn_{\rm D}/2C_{\rm g}$  ( $n_{\rm D}$  is donor density per unit area).  $\phi$  is the minimum point of the electric potential profile along the width direction, i. e. the electric potential at the center of the channel. Actually, the above equation reflects the relation of  $\Phi_c$  to  $n_e$  and  $V_G$ . Therefore, for the Fin-FET case if  $\phi_c$  is defined as the minimum point of the electric potential profile at the cross-section, a similar equation as Eq. (1) may be found once the relation of  $\phi_c$  to  $n_e$  and  $V_G$  is derived according to

2D electrostatics.

From 2D numerical simulation ,one knows that along the width direction (at any point of the height direction), the potential profile is parabolic with the minimum point at x = 0. Thus,  $\oint_{c}$  for Fin-FETs can be defined as  $\phi(0, y_{\min})$ , which is obtained by

$$\left. \frac{\mathrm{d}\phi(0,y)}{\mathrm{d}y} \right|_{y=y_{\min}} = 0 \tag{2}$$

Consequently, the analytical form to the electric potential profile  $\phi(0, y)$  is essential to solve Eq. (2). The 2D Poisson 's equation is presented for the first instance

$$\frac{d^2 \phi(x, y)}{dy^2} + \frac{d^2 \phi(x, y)}{dx^2} = \frac{q(N_e + N_A - N_D)}{s_i} (3)$$

where  $N_{\rm e}$ ,  $N_{\rm A}$ , and  $N_{\rm D}$  are the electron concentration, the donor, and acceptor concentration, respectively. With the parabolic approximation of the electric potential along the x-direction, the electric potential may be expressed as

$$\Phi(x, y) = (y) x^{2} + (y)$$

(4)

The electric displacement continuity at the silicon/ oxide interfaces is shown as

$$-\frac{d\phi(x,y)}{dx}\Big|_{x=b'2} = -2 (y) \times \left(-\frac{b}{2}\right)$$

$$= \frac{-\alpha x}{s_{i}} \times \frac{V_{G} - (\phi_{M} - x) - \phi(-b'2,y)}{t_{ox1}} (5)$$

Therefore, the second derivative respect to x of  $\phi$ (x, y), i. e. 2 (y), is obtained. Equation (3) at the 1D cut line of x = 0 is then rewritten as

$$\frac{d^{2} \phi(0, y)}{dy^{2}} + \frac{8 C_{\text{oxl}}}{b^{2} (C_{\text{oxl}} + C_{\text{d}})} [V_{\text{G}} - (\phi_{\text{M}} - ) - \phi(0, y)] = \frac{q(N_{\text{e}} + N_{\text{A}} - N_{\text{D}})}{s_{\text{i}}}$$

(6)

Integrating both side by  $\int_{0}^{b^{\prime}2} dx$ , one transforms Eq. (6) into Eq. (7)

$$\frac{d^{2} \phi(0, y)}{dy^{2}} \times \frac{b_{Si}}{2} + C_{g} [V_{G} - (\phi_{M} - ) - \phi(x, y)] = \frac{q(n_{e} + n_{A} - n_{D})}{2}$$

(7)

Equation(7) is further solved analytically. The solution is as follows

$$\Phi(0, y) = A + B \frac{\sinh(y/D)}{\sinh(a/D)} + C \frac{\sinh[(a-y)/D]}{\sinh(a/D)}$$

(8)

back) oxide thickness,  $t_{0x2}$  is the top-gate oxide

thickness, and tox3 is the buried oxide thickness.

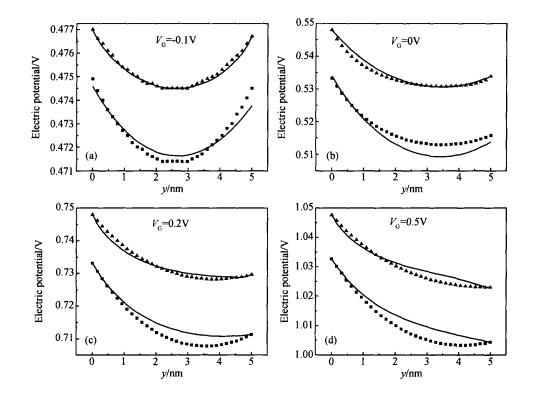

where  $A = V_G - (\Phi_M - ) - q(n_e + n_A - n_D)/2C_g$ ,  $B = \Phi_{0,a} - A$ ,  $C = \Phi_{0,0} - A$ ,  $D = \sqrt{b_{S}/2C_g}$  where  $\Phi_{0,a}$   $= \Phi(0, a)$  and  $\Phi_{0,0} = \Phi(0,0)$  are two constants whose values need to be found. In Fig. 2, the analytical results of  $\Phi(-b/2, y)$  (this can be obtained straightforwardly from  $\Phi(0, y)$ ) and  $\Phi(0, y)$  of a FinFET are compared to numerical results (executed using DESSIS in ISE 8.0, a 2D self-consistent Poisson-Schrödinger solver<sup>[9]</sup>) at various  $V_G$  with given  $\Phi_{,0}$  and  $\Phi_{,a}$  (these two constants are provided by numerical simulation). The analytical profiles agree well with numerical ones and are not uniform along y-direction, which shows the difference between DGMOSFETs and FinFETs. This proves the applicability of Eq. (8).

Fig. 2  $\phi(-b/2, y)$  and  $\phi(0, y)$  profiles along height direction at various gate voltages a = b = 5 nm,  $t_{\text{ox1}} = t_{\text{ox2}} = 1 \text{ nm}$  and  $t_{\text{ox3}} = 25 \text{ nm}$ . Symbols stand for numerical simulation results (triangles for  $\phi(-b/2, y)$  and squares for  $\phi(0, y)$ ) while solid lines stand for analytical results.

Consider the boundary conditions  $\phi(0, y)$  along the height direction:  $\frac{d\phi(0, y)}{dy}\Big|_{y=0} = \frac{C_{0x2}}{s_i} \{ \phi_{0,0} - [V_G - (\phi_M - )] \}$  ( $C_{0x2} = ox/t_{0x2}$  is top-gate oxide capacitance per unit area) and  $\frac{d\phi(0, y)}{dy}\Big|_{y=a} = \frac{C_{0x3}}{s_i} \{ [V_B - (\phi_M - )] - \phi_{0,a} \}$  ( $C_{0x3} = ox/t_{0x3}$  is the back-gate oxide capacitance per unit area and  $V_B$  is

the back-gate voltage). Given these two equations,  $\Phi_{,0}$  and  $\Phi_{,a}$  are deduced,

$$\Phi_{0,0} = (FG + F) (GG - 1)$$

(9)

$$\Phi_{0,a} = (FG + F) / (GG - 1)$$

(10)

where  $F = E[V_G - (\Phi_M - )] + [\cosh(a'D) - 1]A$ with  $E = C_{0x2} D \sinh(a'D) / s_i$ ,  $F = E[V_B - (\Phi_M - )] + [\cosh(a'D) - 1]A$  with  $E = C_{0x3} D \sinh(a'D) / s_i$ ,  $G = E + \cosh(a'D)$  and  $G = E + \cosh(a'D)$ . Thus, the analytical form of  $\Phi(0, y)$  is derived as a function of  $n_e$  and  $V_G$ . Using Eq. (2) and Letting E = 0 (holding true since the thickness of buried oxide is practically much larger than the channel width , i. e.  $t_{0x3} \gg t_{0x} D \sinh(a'D) / s_i$ ), the relation between  $\Phi_e$  and  $n_e$  and  $V_{GS}$  is finally obtained,

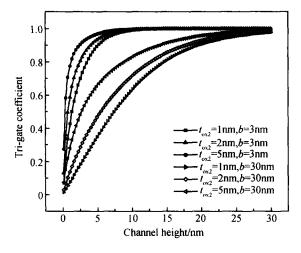

This equation is very similar with Eq. (1) except for the substitution of  $C_g$  for  $C_g$  and the corresponding replacement in  $V_{GS}$  where  $V_A = qn_A/2C_g$ and  $V_{\rm D} = q n_{\rm D} / 2 C_{\rm g}$ .  $C_{\rm g} = C_{\rm g} / H$  with H = 1 - $\frac{E}{GG - 1} \times [2e^{-a/2D} \sqrt{\cosh(a/D)} - e^{-a/D}], \text{ is denoted}$ as tri-gate coefficient, which essentially reflects the effect of the top-gate. In Fig. 3, H is plotted versus a with different  $t_{ox2}$  and b. As it is shown in the figure ,the tri-gate coefficient stays always lower than unity, implying larger gate capacitances of Fin-FETs than those of DGMOSFETs. It may also be drawn that the larger the height is, the larger H is, meaning that the effect of the top gate is weaker since gate capacitance gets closer to the DG case. When  $a \gg D$ , H approaches to unity, leading Eq. (11) to Eq. (1) so that the asymptotic behavior to DGMOSFETs is correct. H decreases with a decreasing  $t_{0x2}$  or an increasing b, meaning the effect of top gate is more severe with thinner top-gate oxide or wider width.

Fig. 3 Tri-gate coefficient *H* versus channel height *a* with different  $t_{0x2}$  and *b*  $t_{0x1} = 1$  nm and  $t_{0x3} = 30$  nm.

With the deduced Eq. (10) ,the threshold voltage model is finally derived as follows (the procedure of which is similar with that in Ref. [5] and therefore is not presented here),

$$V_{\rm T} = \Phi_{\rm M} - + V_{\rm A} - V_{\rm D} + \frac{k_{\rm B} T}{q} lg \left( \frac{2 C_{\rm g} k_{\rm B} T}{q^2 N_{\rm c}} \right)$$

(12)

where  $k_{\rm B}$  is the Boltzmann constant, T is the tem-

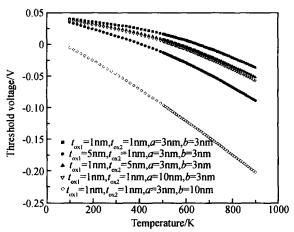

perature ,and  $N_c$  is the effective density of states. This formula comprises quantum mechanical effects<sup>[5]</sup>. In Fig. 4,  $V_T$  is plotted against temperature for different  $t_{ox1}$ ,  $t_{ox2}$ , a, and b. It is concluded that  $V_T$  decreases when any of these four device parameters increases. It should be noted that the temperature coefficient of  $V_T$  increases and the curve of  $V_T - T$  becomes more linear with an increasing value of any of these four parameters. Although the parameters along height direction ( $t_{ox2}$  and a) affect  $V_T$  less severe than the parameters along width direction ( $t_{ox1}$  and b) do , they do have an influence on  $V_T$  and thus the device characteristics.

Fig. 4 Threshold voltage  $V_T$  versus temperature T with different  $t_{\text{ox1}}$ ,  $t_{\text{ox2}}$ , a, and b  $t_{\text{ox3}} = 30$  nm.

## 3 Conclusion

In this paper, a compact threshold voltage model for FinFETs is presented with the relation to device parameters clearly clarified. It is concluded that both gate capacitance and threshold voltage will increase with decreasing of height or topgate oxide thickness.

#### References

- Frank D J ,Laux S E, Fischetti M V. Monto Carlo simulation of a 30nm dual-gate MOSFET: how short can Si Go. Digest of IEDM, 1992:553

- [2] Balestra F. Comments on: double-gate operation and volume inversion in m-channel SOI MOSFET 's. IEEE Electron Device

Lett ,1992 ,13:658

- [3] Fiegna C, Abramo A. Solution of Schrodinger and Poisson equation in single and double gate SOI MOS. Digest of IEDM, 1997:93

- [4] Yang Fuliang. 5nm gate nanowire FinFET. IEEE Symposium on VLSI Technology ,2004

- [5] Giorgio B ,Susanna R. A compact double-gate MOSFET model comprising quantum-mechanical and nonstatic effects. IEEE Trans Electron Devices, 1999, 46(8):1656

- [6] Suzuki K, Tanaka T, Tosaka Y, et al. Analytical surface potential expression for thin-film double-gate SOI MOSFET 's.

Solid-State Electron ,1994 ,37:327

- [7] Suzuki K, Sugii T. Analytical models for n<sup>+</sup>-p<sup>+</sup> double-gate SOI MOSFET 's. IEEE Trans Electron Devices, 1995, 42: 1940

- [8] Suzuki K, Tosaka Y, Sugii T. Analytical threshold voltage model for short channel n<sup>+</sup>-p<sup>+</sup> double-gate SOI MOSFET 's. IEEE Trans Electron Devices, 1996, 43:732

- [9] http://www.ise.ch ISE 8.0 User Manual

- [10] Liu Zhihong, Hu Chenming, Huang Jianhui, et al. Threshold voltage model for deep-submicrometer MOSFET 's. IEEE Trans Electron Devices, 1993, 40(1):86

## FinFET 器件的集约阈电压模型<sup>\*</sup>

张大伟 田立林 余志平

(清华大学微电子学研究所,北京 100084)

摘要:对 FinFET器件(或称三栅 MOSFET器件)的二维截面做了解析静电学分析以得出阈电压的计算公式.结果显示,由于三栅结构在高度方向的限制作用,需要引入一个 H系数来修正栅电容,随着高度不断变大,它渐近于 双栅 MOSFET器件的情况.由该解析模型得出的电势分布与数值模拟结果吻合.提出了一个包含量子效应的 Fin-FET器件的集约阈电压模型,结果表明,当高度或者顶栅的氧化层厚度变小时,栅电容及阈电压都会上升,这与 FinFET设计时发现的趋势是相符合的.

关键词: FinFET 器件;二维解析静电学分析;集约模型;阈电压

PACC: 7340Q; 6185; 0300

中图分类号: TN304.02

文献标识码: A

文章编号: 0253-4177(2005)04-0667-05

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2003AA1Z1370)

张大伟男,1980年出生,硕士研究生,主要从事纳米级器件中新型物理效应的集约解析建模.Email:zdw99@mails.tsinghua.edu.cn2004-09-07收到,2004-11-12定稿©2005中国电子学会