# A 12bit 300MHz Current-Steering CMOS D/ A Converter \*

Ni Weining, Geng Xueyang, and Shi Yin

(Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China)

Abstract: The proposed DAC consists of a unit current-cell matrix for 8MSBs and a binary-weighted array for 4LSBs, trading-off between the precision, speed, and size of the chip. In order to ensure the linearity of the DAC, a double Centro symmetric current matrix is designed by the  $Q^2$  random walk strategy. To achieve better dynamic performance, a latch is added in front of the current switch to change the input signal, such as its optimal cross-point and voltage level. For a 12bit resolution, the converter reaches an update rate of 300M Hz.

Key words: D/ A converter; current-steering; CMOS mixed integrated circuit; cross-point;  $Q^2$  random walk EEACC: 1265 H; 1280; 2570

**CLC number :** TN432 **Document code : A** Article ID : 0253-4177 (2005) 06-1129-06

## 1 Introduction

The digital to analog converter (DAC), widely used in the modern digital and analog circuits, is a very important component of the interface. The current steering DAC is based on an array of matched current cells organized in unary encoded or binary weighted elements that are steered to the DAC output depending on the digital input code. The segmented architecture is most frequently used to combine high conversion rate and high resolution. In this architecture the least significant bits steer binary weighted current sources, while the most significant bits, which are thermometer encoded, steer a unary current source array<sup>[1]</sup>. The influence of current switches on output glitch of the high-speed current-steering CMOS DAC is thoroughly analyzed ,and the methods for reducing glitch are presented<sup>[2]</sup>.

The proposed DAC in this work is composed of a unit current-cell matrix for 8MSBs and a binary-weighted array for 4LSBs to obtain high linearity at 12bit level. In double centro symmetric current matrices, the  $Q^2$  random walk strategy is adopted to improve the nonlinearity, which can be degraded by the symmetric error and two-dimensional graded error of the DAC. In order to achieve better dynamic performance, a latch has been added in front of the current switch to change the input signal, such as its optimal cross-point and voltage level. The delay time difference of digital signals is minimized with the intermediate latches placed in front of the related decoders. In addition, a clock tree is designed to make sure that the difference in delay among all the branches from the source pins to drive pins after routing is minimized.

# 2 DAC architecture

Considering a N bit current steering segmented DAC with a unit current source I:the  $N_1$  MSBs control  $2^{N_1}$  - 1 equal current source of  $2^{N_2}$  I, and the  $N_2$  LSBs control  $N_2$  binary weighted current sources multiple of I. A simple estimation for the integral nonlinearity (INL) is found by adding the variances of  $2^N$  - 1 uncorrelated current sources<sup>[3]</sup>. One sigma confidence value for the INL is given by

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2002AA1Z1200)

Received 20 October 2004 ,revised manuscript received 28 February 2005

©2005 Chinese Institute of Electronics

INL

$$\sqrt{2^{N-1}} - \mathbf{X} L SB$$

(1)

where /I is the unit current source relative standard deviation. Equation (1) shows that the INL is independent of the used segmentation and it is only a function of the required accuracy. The worst differential nonlinearity (DNL) is defined in the transition from the binary weighted LSBs to the unity decoded MSBs<sup>[3]</sup>. One sigma confidence value for the DNL is given by

DNL

$$\sqrt{2^{N_2}} - \times LSB$$

(2)

The INL related yield specification imposes a maximum constraint on the allowed mismatch of the unit current source. This constraint results in a minimum channel area dimension for the transistor as is given by

$$WL = \frac{I^2}{2^2} \left[ A^2 + \frac{4A_{\rm VT}^2}{(V_{\rm OS} - V_{\rm T})^2} \right]$$

(3)

where A and  $A_{\rm VT}$  are mismatch technology parameters and  $V_{\rm CS}$  -  $V_{\rm T}$  is the gate overdrive voltage of the current source transistor.

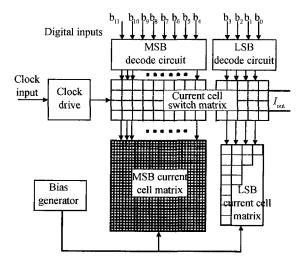

To achieve good DNL and INL specification, the number of bits implemented in the binary weighted part of the DAC should to be small<sup>[1]</sup>. For every extra bit implemented in the unity decoded part , however , the number of control lines needed to select the current sources doubles and the decoding logic complexity increase significantly. Equally important, the area used by the decoding inside the matrix increases and consequently the process and electric systematic errors become more difficult to compensate<sup>[1]</sup>. A direct consequence is often a reduction in the maximum operating speed. In addition, the area occupied by interconnections inside the decoding circuit quickly increases. The area of interconnections is obtained using silicon ensemble (SE) that is used to produce a layout of the netlist generated by the synthesis tool. The 12bit DAC is implemented as a segmented current DAC. Figure 1 gives a schematic representation of the realized chip. The DAC is composed of the unit

current-cell matrix for 8MSBs and the binaryweighted array for 4LSBs, considering the error of circuit, speed, yield, and chip area at 12bit resolution.

Fig. 1 Simplified DAC architecture with current

## **3** Static performance

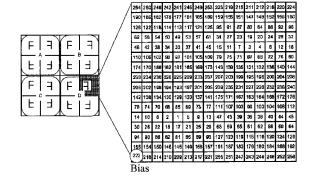

In the unit decoded matrix, it is difficult to make current sources identical due to layout mismatches, output impedance of the current source and switch, edge effects, voltage drops in the supply lines, thermal gradients, doping gradient, and oxide thickness. The nonlinear secondary effects cause graded ,symmetrical ,and random errors ,thus result in the reduced linearity of DACs. The proposed DAC employs a novel switching scheme to minimize the degradation of integral linearity caused by mismatches of current sources. This switching scheme will be referred to as quad quadrant  $(Q^2)$ , because four (quad) units in every quadrant compose one current source<sup>[4]</sup>. The switching sequence of the unit current cells in the matrix for 8MSBs is illustrated in Fig. 2. The 256 current sources are divided into 16 centro symmetric regions ,and then the 16 current sources in every region are divided into 16 centro symmetric regions. Since the 16 current sources in every region do not have exactly the residue, there is a remaining small second-order residue. By "random walking" through the 256 current sources, the residual error is not accumulated but rather "randomized", hence named  $Q^2$  random walk switching scheme. Only 255 current sources are required for the DAC function. One of the 256 current sources is used as a biasing circuit.

Fig. 2 Switching sequence of the  $Q^2$  random walk switching scheme

### 4 Dynamic performance

It is well known that the dynamic performance of a current steering DAC is limited by three factors:(1) voltage fluctuation in the output nodes of the current sources due to improper timing of the switching OFF and ON of the transistors;(2) digital signal feed-through through the gate-drain capacitance from the current switches directly to the output;(3) imperfect synchronization of the control signals of the switching transistors<sup>[5,6]</sup>.

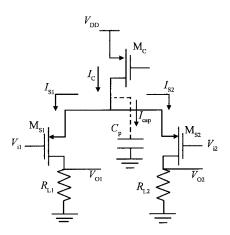

Figure 3 shows the figure of the unit current cell of a current-steering DAC where the parasitic capacitance  $C_{\rm p}$  is indicated. The unit current cell consists of the pMOS switching transistors  $M_{\rm S1}$  and  $M_{\rm S2}$ , the output resister  $R_{\rm L}$ , and the pMOS current source transistor  $M_{\rm C1}$ . To determine the dimensions of the transistor  $M_{\rm S1}$ ,  $M_{\rm S2}$  and  $M_{\rm C}$  are taken into account<sup>[7]</sup>. pMOS can decrease the high frequency noise generated by common substrate at the n-well process.

During the switching OFF or ON state of the transistor, the discharge or charge of the parasitic capacitance  $C_p$  takes place, leading to a deteriora-

Fig. 3 Basic current cell block

tion of the dynamic performance of the DAC. Especially ,two switching transistors can be at the OFFstate simultaneously for a short period of time. In order to avoid this situation ,the general way is to adjust the cross-point of control signals , and the time of two switching transistors being at the ONstate must be shortened. Therefore ,the cross point must be carefully selected.

As shown in Fig. 3, at the node A:

$$I_{\rm s} = I_1 + I_2 + I_{\rm cap}$$

(4)

where  $I_s$  is the current of the cell,  $I_1$  and  $I_2$  are the output current of two switching transistors, and  $I_{cap}$  is the discharge and charge current of the parasitic capacitance  $C_p$ .

Provided that  $I_{cap} = 0$ , the voltage variation at the node A is minimized when the switching control signals change. Namely,

I.

$$= I_1 + I_2$$

(5)

Even as the switching control signals appear in the cross-point and the two pMOS switching transistors are at the ON-state, the current of the two pMOS switching transistors can be approximately expressed as

$$I_{1} = \frac{\mu_{\rm p} C_{\rm ox}}{2} \times \frac{W}{L} (V_{\rm GS1} - V_{\rm T})^{2}$$

(6)

$$I_{2} = \frac{\mu_{\rm p} C_{\rm ox}}{2} \times \frac{W}{L} (V_{\rm GS2} - V_{\rm T})^{2}$$

(7)

where  $\mu_p C_{ox}$  is the device-transconductance parameter and  $V_{CS}$ - $V_T$  is the gate overdrive voltage of the transistor. When the switching control signals appear in the cross-point ,the following formula is obtained.

$$V_{\rm GS1} = V_{\rm GS2} = V_{\rm GS(CP)} \tag{8}$$

Combining Eqs. (6)  $\sim$  (8) ,we obtain

$$V_{\rm GS(CP)} = V_{\rm T} + \sqrt{I_c/2K}$$

$$K = \mu_{\rm p} C_{\rm ox} W/2L$$

(9)

when one pMOS switching transistor is in the ONstate and the other is in the OFF-state ,the voltage is given by

$$V_{\rm GS(ON)} = V_{\rm T} + \sqrt{I_{\rm C}}/K$$

(10)

Combining Eqs. (9) and (10), the optimal crosspoint voltage is calculated by the following formula.

$$V_{\rm G(CP)} = V_{\rm GS(ON)} - V_{\rm GS(CP)} = \left(1 - \frac{1}{\sqrt{2}}\right) \sqrt{I_{\rm s}/K}$$

(11)

For the nMOS transistor, the optimal cross-point voltage is higher than  $V_{G(CP)}$ , namely  $V_{DD}$  -  $V_{G(CP)}$ .

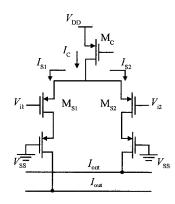

This project is to minimize the feedthrough to the output lines. The drain of the switching transistors is isolated from the output lines by adding two cascaded transistors (with the same dimensions as the switching transistors), as shown in Fig.  $4^{[8]}$ .

Fig. 4 Current cell with cascaded transistors

The proposed DAC employs extra digital latches just in front of the unit current cells to synchronize the digital inputs as well as employ the cascaded current sources to minimize the current variation effect. This is to overcome the skew between the row and the column select signals in the local decoder.

#### 5 DAC implementation

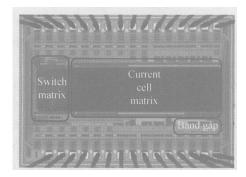

The chip photograph is shown in Fig. 5. The chip has been implemented in a 2-poly and 4-metal 0. 35µm CMOS process of Chartered Foundry and occupies the active die area of 1. 0mm ×1. 6mm. The digital encoder is placed on the top of the chip, far away and well shielded form the sensitive analog parts. During the layout of the current sources matrix, cadence Skill language is used to help the sorting and routing of the unit current sources, which greatly improves the design efficiency and guarantees the success of the tape out. Different power supply lines have been used for different parts of the circuit to reduce the noise coupling to the sensitive analog blocks<sup>[8]</sup>. Finally, in the very few exception where digital signals cross sensitive analog lines, a cleanly biased metal line is used as a shield. The clock driver which drives the digital encoder and analog latches in the switch array has been added to the chip. The clock is distributed through a tree to ensure low skew between the different analog latches (see Fig. 5). The clock tree is routed on the top level metal layer (lowest resistance).

Fig. 5 Chip photograph of the D/ A converter

#### 6 Experiment results

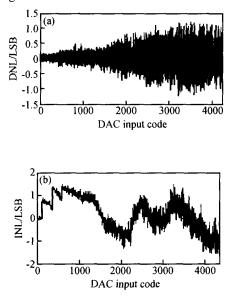

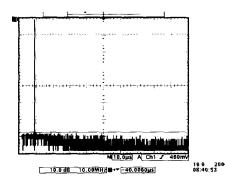

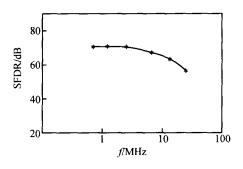

The DAC is measured at 3. 3V and the maximum output current for the 50 termination resister is 20mA to obtain the maximum single-ended analog output voltage of 1V. As show in Fig. 6, the measured DNL and INL of the prototype DAC are within  $\pm 1.1LSB$  and  $\pm 1.6LSB$ , respectively. Figure 7 shows the output spectrum of the DAC with a 9M Hz input signal at a 300M Hz update rate. The measured spurious-free dynamic range (SFDR) is 66dB. Figure 8 shows the measured SFDR of the

Fig. 6 DNL (a) and INL (b) measurement

Fig. 7 Output spectrum at 300MHz update rate approximately 9MHz signal

Fig. 8 Measured SFDR

prototype DAC with different input signal frequencies at 300M Hz. Table 1 summarizes the performance of the DAC and the AD9753 of the analog device. Their performances are very similar.

Table 1 Comparison of performance of 12bit DACs

| Parameter         | This paper      | AD9753 <sup>[9]</sup> |

|-------------------|-----------------|-----------------------|

| Resolution        | 12bit           | 12bit                 |

| Update rate       | 300 M Hz        | 300 M Hz              |

| DNL               | 1. 1LSB         | 1. 0LSB               |

| INL               | 1. 6L SB        | 1. 5L SB              |

| SFDR              | 66dB            | 69dB                  |

|                   | (9MHz @300MSPS) | (26MHz @300MSPS)      |

| Power voltage     | 3.3V            | 3.3V                  |

| Power dissipation | 150mW           | 155mW                 |

|                   | @300MHz ,3. 3V  | @300MHz ,3. 3V        |

| Process           | 0. 35µm         | 0. 35µm               |

# 7 Conclusion

In this paper a 3. 3V 12bit 300M Hz CMOS DAC for a high-speed direct digital frequency synthesizer is designed and implemented. The DAC employs a novel switching scheme called  $Q^2$  random walk. In order to achieve better dynamic performance, a latch has been added in front of the current switch to change the input signal, such as its optimal cross-point and voltage level. The DAC consumes 150mW in the total power consumption with a 3. 3V supply at 300M Hz. The measured DNL and INL are within  $\pm 1$ . 1LSB and  $\pm 1$ . 6LSB, respectively, and the SFDR is 66dB for a 9M Hz input at an update rate of 300M Hz.

#### References

- [1] Lin Chihung ,Bult K. A 10-b 500-M sample/s CMOS DAC in 0. 6mm. IEEE J Solid-State Circuits ,1998 ,33(12) :1948

- [2] Zhao Weibing, Shen Yanzhao, Zhang Xiangmin. Current swithes in improved high speed DAC and control signals of switches. Chinese Journal of Semiconductors, 2003, 24 (9): 991 (in Chinese) [赵伟兵,沈延钊,张向民. 一种改进的高速 DAC 电流开关及其控制信号的产生. 半导体学报, 2003, 24 (9):991]

- [3] Marques A, Bastos J, Steyaert M, et al. A current steering architecture for 12-bit high-speed D/ A converters. IEEE Circuits and Systems International Conference, 1998:23

- [4] Van der Plas GAM, Jan V, Will S, et al. A 14-bit intrinsic accuracy Q<sup>2</sup> random walk CMOS DAC. IEEE J Solid-State Circuits, 1999, 34(12):1708

- [5] Bastos J, Augusto M, Marques A, et al. A 12-bit intrinsic accuracy high-speed CMOS DAC. IEEE J Solid-State Circuits, 1998, 33(12):1959

- [6] Yu Xuefeng, Shi Yin. High-performance CMOS D/A converter based on offsetting variations in processing. Chinese Journal of Semiconductors, 2003, 24(11):1211(in Chinese)[于雪 峰,石寅.基于制作离散性对策的高性能 CMOS DAC. 半导体

学报,2003,24(11):1211]

- [7] Pelgrom M J M, Duinmaijeret A C J, Welberas A P G, et al. Matching properties of MOS transistors. IEEE J Solid-State Circuits, 1989, 22 (5):1433

- [8] Takakura H, Yokoyama M, Yamaguchi A. A 10 bit 80 MHz glitchless CMOS D/ A converter. Proc IEEE Custom Integrated Circuits Conference, 1991:26.5.1

- [9] Analog Device Inc., Data Sheet: AD 9 7 5 3 12-bit 3 0 0 MSPS high speed TxDAC + D/ A converter ,2003

# 12 位 300MHz 电流驱动型 DAC\*

倪卫宁 耿学阳 石 寅

(中国科学院半导体研究所,北京 100083)

摘要:在电路误差、电路占用芯片面积相互折中和妥协的前提下提出了一种 8 + 4 结构的电流驱动型数模转换器. 采用 Q<sup>2</sup> random walk 方法设计了一个新型的双中心对称的电流矩阵,确保数模转换器的线性度.分析并求出了最 佳电平交叉点,设计了电平钳位锁存器对开关电平限幅,DAC 动态性能得到改善.在 12 位分辨率下,刷新率达到 300M Hz 以上.

关键词: D/A转换器;电流驱动; CMOS 混合集成电路;电平交叉点; Q<sup>2</sup> random walk

EEACC: 1265 H; 1280; 2570

中图分类号: TN432

文献标识码: A

文章编号: 0253-4177(2005)06-1129-06

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2002AA1Z1200) 2004-10-20 收到,2005-02-28 定稿