# Analysis and Optimum Design of Differential Inductors Using Distributed Capacitance Model \*

Jian Hongyan, Tang Zhangwen, He Jie, and Min Hao

(State Key Laboratory of ASIC & System, Fudan University, Shanghai 200433, China)

**Abstract :** A distributed capacitance model for monolithic inductors is developed to predict the equivalently parasitical capacitances of the inductor. The ratio of the self-resonant frequency  $(f_{SR})$  of the differential-driven symmetric inductor to the  $f_{SR}$  of the single-ended driven inductor is firstly predicted and explained. Compared with a single-ended configuration, experimental data demonstrate that the differential inductor offers a 127 % greater maximum quality factor and a broader range of operating frequencies. Two differential inductors with low parasitical capacitance are developed and validated.

Key words: distributed capacitance model; self-resonant frequency ratio; quality factor; differential inductor; optimum design

EEACC: 2140; 2530B; 2550F CLC number: TN405 Document code: A Article ID: 0253-4177(2005)06-1077-06

## 1 Introduction

A monolithic inductor is an important component in highly integrated radio frequency circuits (RF ICs) for wireless communication systems. But a monolithic inductor has a low quality factor Qdue to metal ohmic loss and conductive silicon substrate loss. Many researchers found quite a few methods to improve the Q of the monolithic inductor<sup>[1]</sup>. The Q and  $f_{SR}$  (self-resonant frequency) are the two most important parameters of the monolithic inductor. The lower parasitical capacitance the inductor has, the higher Q and  $f_{SR}$  are.

It should be noted that the differential circuits (amplifiers, mixers, and oscillators) are commonly used in monolithic transceiver designs because of their robustness and superior noise rejection properties (e. g. power supply noise rejection). A symmetric inductor consumes less chip area as compared to single-ended equivalents when used in a typical circuit. A symmetric inductor that is excited differentially (also called a differential inductor) can realize a substantially greater factor without altering the fabrication process<sup>[2]</sup>.

The distributed capacitance model (DCM) for monolithic inductors, which is for a single-ended inductor but not for the differential inductor has been studied in recent years<sup> $[3^{-5}]</sup>$ .</sup>

In this paper, from the view of the parasitical capacitance of the inductor, the reason for a differential inductor with both a higher Q and  $f_{SR}$  is analyzed and firstly interpreted by DCM. Two differential inductors with the low equivalently parasitical capacitances ( $C_{m\_m}$ ) between the two terminals are developed and validated.

Received 14 November 2004 , revised manuscript received 1 February 2005

<sup>\*</sup> Project supported by the Shanghai Science & Technology Committee (No. 037062019)

Jian Hongyan male, PhD candidate. He is interested in monolithic inductor and antenna optimization, RF circuits design such as LNA, mixer, and VCO, and antenna design for RFID. Email : hyjian @fudan.edu.cn

### 2 Distributed capacitance model

Inductors that are driven differentially or single-ended (See Fig. 1) have different equivalent parasitic capactiances ( $C_{eq}$ ). The equivalent capacitance of the spiral inductor can be expressed as<sup>[3]</sup>

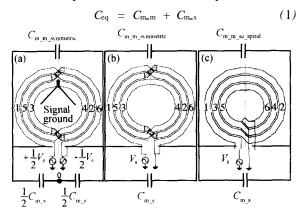

Fig. 1 Planar monolithic inductors with the same track width ,space ,inner ,and outer radius (a) Differentialdriven symmetric configuration (DSPI); (b) Single-ended-driven symmetric configuration (SSPI); (c) Singleended spiral configuration (SEPI) 1,2,3,4,5, and 6 are current flow direction in inductor, i. e. AC signal voltage profile or half-turns serial number; Capacitances are the equivalently parasitical capacitance of the monolithic inductor.

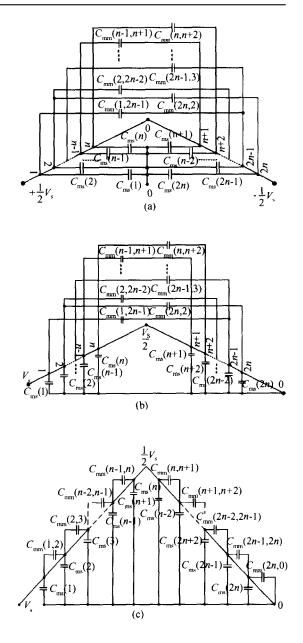

The DSPI can be regarded as two single-ended planar inductors having same the  $C_{m\_s}$ , whose connection point is signal ground and whose  $C_{m\_s}$  are in series. The  $C_{m\_m}$  of the DSPI are partly in series connection and partly in parallel as shown in Fig. 2 (a). The  $C_{m\_m}$  of the SSPI are partly in series connection and partly in parallel and its  $C_{m\_s}$  are in parallel as shown in Fig. 2 (b). The  $C_{m\_m}$  of the SEPI are in series connection and its  $C_{m\_s}$  are in parallel. Voltage profiles of three inductors are different as shown in Fig. 2.

#### 2. 1 Assumptions and definitions

To accurately quantify the  $C_{m\_m}$  and  $C_{m\_s}$  in inductors, the DCM can be used to analytically calculate them rather than qualitatively approximate. The DCM is validated by the previous papers<sup>[3,4]</sup>.

Fig. 2 Voltage profile and distributed capacitance model of the r turn planar inductor (a) DSPI; (b) SSPI; (c) SEPI

This paper also applies the same method for the differential inductors. The fundamental assumptions of the DCM can be derived from the voltage distribution over the inductor ,which is called voltage profile<sup>[4]</sup>. For the conveniences of calculation and analysis ,the following assumptions are made.

(1) The same layer metal traces of the inductor have the same resistivity ,current ,metal track width w (at least in the same half-turn) ,and metal thickness t;

(2) Voltage distribution is proportional to the lengths of the metal tracks<sup>[4]</sup>;

(3) The kth unit voltage difference between the adjacent half-turns is regarded as a constant and is determined by averaging the beginning voltage and the ending voltage of the half-turns, regardless of the type of the inductor.

The length of each half-turn can be defined as  $l_1$ ,  $l_2$ , ...,  $l_m$ ,  $l_{2n}$  (*n* is the half-turn number, sequential *m* represents current flow direction in the inductor), and the total length is defined as  $l_{\text{tot}}$  ( $= l_1 + l_2 + ... + l_{2n}$ ). The AC signal voltage of one terminal of the inductor is  $V_{\text{beg}}$ , while that of the other is  $V_{\text{end}}$ . By assumptions, AC signal voltage at the end terminal of the *m*th half-turn inductor [ $V_{\text{end}}$  (*m*)] can be expressed as

$$V_{\text{end}}(m) = \frac{l_j}{l_{\text{tot}}} (V_{\text{beg}} - V_{\text{end}})$$

(2)

The AC signal voltage at the beginning terminal of the *m*th half-turn inductor  $[V_{beg}(m)]$  equals  $V_{end}(m-1) \cdot V_{beg}(0) = V_{beg}$ .

#### 2. 2 Equivalent capacitance formula

The lowest layer metal track of the *m*th halfturn inductor is equally divided into k units (*i*

). According to assumption (2), the voltage of the *i*th unit is  $V_i$ ,

$$V_i = V_{\text{beg}}(m) - \frac{i}{k} V_{\text{m}}(i)$$

(3)

where  $V_{m}(i)^{k} = \frac{1}{k} (V_{beg}(m) - V_{end}(m))$ . There-

fore, the electrical energy stored in the capacitor between the *i*th unit metal and the substrate can be expressed as

$$E_{\rm c,ms}(i) = \frac{1}{2} C(i) (V_{\rm m})^{2}$$

=  $\frac{1}{2} C_{\rm ms} \frac{wl}{k} \times \left[ \frac{1}{k} (V_{\rm beg}(m) - V_{\rm end}(m)) \right]^{2}$  (4)

where  $C_{\rm ms}$  represents the capacitance per unit area between the *m*th half-turn and the substrate. The electrical energy stored in the equivalent capacitance between the metal tracks of the  $L_{\rm ms}(m)$  and the substrate can be derived<sup>[6]</sup>

$$E_{c,m_{s}} = \frac{1}{6} C_{ms} w l (V_{beg}^2 + V_{end}^2 + V_{beg} V_{end}) \quad (5)$$

Whatever the structure of the inductor is, the entire  $E_{c,m_s}$  can be figured by adding all the  $E_{c,m_s}$ (m).

The two terminal voltages of the DSPI are +  $\frac{1}{2}V_s$  and -  $\frac{1}{2}V_s$ , respectively. Hence

$E_{c,ms\_diff} = \frac{1}{2} \times \frac{1}{12} C_{ms} w l_{tot} V_s^2 = \frac{1}{2} C_{m\_s\_diff} V_s^2$ So,

$$C_{\rm m\_s\_diff} = \frac{1}{12} C_{\rm ms} w l_{\rm tot}$$

(6)

where  $C_{\text{m-s-diff}}$  is the equivalent capacitance between the metal track and the substrate of the DSPI.

The signal terminal voltage of the SEPI is  $V_s$ and that of the other terminal is 0 ,hence

$$E_{\rm c,ms\_diff} = \frac{1}{2} \times \frac{1}{3} C_{\rm ms} \, w \, l_{\rm tot} \, V_{\rm s}^2 = \frac{1}{2} \, C_{\rm m\_s\_se} \, V_{\rm s}^2$$

So

$$C_{\text{m_ss_se}} = \frac{1}{3} C_{\text{ms}} w l \tag{7}$$

where  $C_{m\_s\_se}$  is the equivalent capacitance between the metal track and the substrate of the SEPI.

According to Eqs. (6) and (7) ,under the same equivalent-area between the metal track and the substrate ,we can get the following equation

$$C_{\text{m-s-diff}} = \frac{1}{4} C_{\text{m-s-se}}$$

(8)

#### 2. 3 Equivalent capacitance C<sub>m.m</sub> formula

The voltage difference between the *i*th and *j*th half-turn can be expressed as

$$V_{i,j} = V_i - V_j = \frac{l_k}{l_{\text{tot}}} \times (V_{\text{beg}} - V_{\text{end}}),$$

0 i, j n (9)

The electrical energy stored in the equivalent capacitance between the metal tracks of the *i*th half-turn and *j*th half-turn can be expressed as

$$E_{c,m_m}(i,j) = \sum_{k=1}^{2n \cdot 2} E_{c,m_m}(k) = \frac{1}{2} \times \frac{C_{m_m,ij}W(l_i + l_j) {j \choose k=i+1} l_k^2}{2 l_{\text{tot}}^2} (V_{\text{beg}} - V_{\text{end}})^2 (10)$$

where  $C_{mm\_ij}$  is the unit capacitance between the *i*th and *j*th adjacent half-turns of the inductor; *W* is the metal tracks width *w* of the inductor when the *i*th half-turn and *j*th half-turn are stacked or metal thickness *t* when the *i*th half-turn and *j*th half-turn are in the same layer.

Regardless of the structures (stacked, spiral, symmetric, etc.), and driven modes (differentially or single-ended), the electrical energy stored in the equivalent capacitance between the metal can be expressed as the sum of the electrical energy stored in the equivalent capacitance between the metal traces at the same layers and at the adjacent layers. Different  $C_{m\_m}$  formulas can be derived from Eq. (10) and  $E_{c,mm} = \frac{1}{2} C_{m\_m} (V_{beg} - V_{end})^2$ . We define the  $C_{m\_m}$  of the DSPI as  $C_{m\_m\_diff}$ , the  $C_{m\_m}$  of the SSEI as  $C_{m\_m\_diff\_se}$ , and the  $C_{m\_m}$  of the SEPI as  $C_{m\_m\_se\_spiral}$ . Thus,

$$C_{\text{m-m-diff}} = C_{\text{m-m-diff-se}} = \prod_{i=1}^{n-1} C_{\text{mm}}(i, 2n - i) \frac{w(l_i + l_{2n-i})}{2} \left(\frac{l_i}{l_{\text{tot}}}\right)^2 + \prod_{i=2}^{n} C_{\text{mm}}(i, 2n - i + 2) \frac{w(l_i + l_{2n-i+2})}{2} \left(\frac{l_i}{l_{\text{tot}}}\right)^2$$

(11)

$C_{m_m_se_spiral} = 2n \cdot 2$

$$\sum_{i=1}^{2n-2} \left( C_{mm}(i,i+2) \frac{w(l_{i}+l_{i+2})}{2} \left( \frac{l_{i}+l_{i+2}}{l_{tot}} \right)^{2} \right)$$

(12)

### **3** Experiment and discussions

In order to verify accuracy, the inductors have been fabricated in a 0.  $35\mu$ m two-poly four-metal CMOS processes as shown in Fig. 3. The prototype chips also include the de-embed layouts to calibrate the on-wafer testing wiring and pads<sup>[7]</sup>. The *S* parameters are measured by a network analyzer and Cascade Microtech Probe Station using coplanar ground-signal-ground probes.

#### 3. 1 Ratio of self-resonant frequency

The equivalent capacitance of the inductor can

Fig. 3 Die photos of the inductors in 0. 35m CMOS processes (a) and one inductor with probes (b)

be calculated when the inductance is gotten. According to previous equations, the self-resonant frequency ratio of the optional two inductors with equivalent inductance  $L_{eq1}$ ,  $L_{eq2}$  and the equivalent capacitor  $C_{eq1}$ ,  $C_{eq2}$ , respectively, can be expressed as

$$\operatorname{Ratio}_{f_{\mathrm{SR}}} = \frac{f_{\mathrm{SR}}^{L_1}}{f_{\mathrm{SR}}^{L_2}} = \sqrt{\frac{L_{\mathrm{eq2}} C_{\mathrm{eq2}}}{L_{\mathrm{eq1}} C_{\mathrm{eq1}}}}$$

(13)

The inductance  $L_{unsymmetric}$  equals  $L_{symmetric}$  approximately, if the current flows in the same direction along each adjacent conductor of the planar inductors with the same geometric parameters [such as Figs. 1 (a), (b), and (c)], and the voltage difference between the adjacent turns of the DSPI and SSPI is larger than those of the SEPI, so  $C_{m\_m\_SSPI} = C_{m\_m\_SEPI}$ , but  $4C_{m\_s\_DSPI} = C_{m\_m\_SSPI}$  and  $Q_{DSPI} > Q_{SEPI}$ , but  $4C_{m\_s\_SPI} > f_{SR\_SSPI}$  and  $Q_{DSPI} > Q_{SEPI} > Q_{SSPI}$ . This conclusion and Equation (13) can offer design guidelines for inductor and circuit configurations.

The self-resonant frequency ratio ( $\operatorname{Ratio}_{f_{SR}}$ ) of the DSPI to the same inductor that is driven singleended can be expressed as

$$1 < \operatorname{Ratio}_{f_{\mathrm{SR}}} = \frac{f_{\mathrm{SR\_diff}}}{f_{\mathrm{SR\_se}}} = \frac{4 + C_{\mathrm{m\_m}} / C_{\mathrm{m\_s\_diff}}}{\sqrt{1 + C_{\mathrm{m\_n}} / C_{\mathrm{m\_s\_diff}}}} < 2$$

(14)

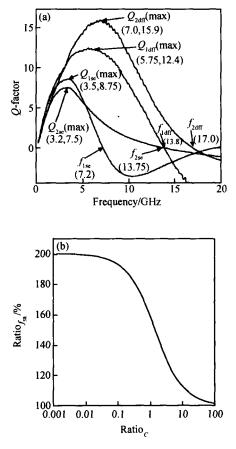

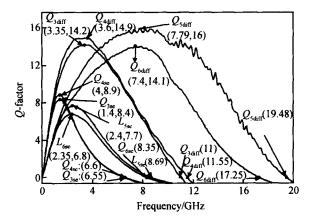

Figure 4(b) shows that the  $\operatorname{Ratio}_{f_{SR}}$  decreases with the  $C_{m\_m}/C_{m\_s\_diff}$ . The  $\operatorname{Ratio}_{f_{SR}}$  can be predicted and explained from Eq. (14). Compared with a singleended configuration, the experimental data demonstrate that the differential inductor offers a 127 % greater  $Q_{max}$  and a much broader range of operating frequencies. In Fig. 4(a)  $\operatorname{Ratio}_{f_{SR}}(L_1)/\operatorname{Ratio}_{f_{SR}}(L_2)$ = 1. 55. The pn junction is formed at the interface between the n-well and p-substrate, and the pn junction capacitor is in series with the oxide capacitance between the inductor and the silicon substrate, thus the equivalent  $C_{m\_s}$  are greatly reduced, but the  $C_{m\_m}$  of both inductors are the same, i. e.  $C_{m\_m}/C_{m\_s\_diff}$  is variable, which results in the different Ratio<sub>f\_SR</sub>. The patterned ground shielding made of the lowest layer metal reduces the substrate loss more than the patterned n-well floating does, therefore,  $Q_{se}^{L_1} > Q_{se}^{L_2}$  at a low frequency and  $Q^{L_1} < Q^{L_2}$  at a high frequency due to  $f_{SR}^{L_2} > f_{SR}^{L_1}$ .

Fig. 4 (a) Q factor as a function of fregnency; (b) Ratio<sub>f SR</sub> as a function of Ratio<sub>C</sub> =  $C_{\text{m-n}}/C_{\text{m-s-diff}}$

### 3.2 Optimum design of differential inductor

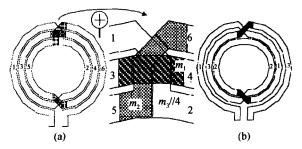

The lower the total parasitic capacitance is ,the higher quality factor the inductor has. Two kinds of optimum designs of the DSPI are developed.  $C_{m\_m\_diff}$  is reduced by decreasing the voltage difference between the adjacent turns in Fig. 5 (a) through multilevel interconnects and by increasing

the space of adjacent turns with larger voltage difference as shown in Fig. 5(b). According to Eq. (6), the  $C_{m\_m}$  will be reduced if the lowest metal tracks layer of the stacked or 3D inductor has the voltage which is nearer to the signal ground. Compared to the conventionally differential inductor with the same width and turns, two differential inductors with low  $C_{m\_m}$  structures have high Q and  $f_{SR}$  as shown in Fig. 6.

Fig. 5 Two differential inductors with low  $C_{m-m} = 1, 2$ , 3,4,5, and 6 are current in inductor flow direction, i. e. AC signal voltage profile. In  $m_i$ , *i* represents metal layer number.

Fig. 6 Q and  $f_{SR}$  of two differential inductors with low  $C_{m_{m}}$   $L_3$  is the inductor in Fig. 5 (b) and  $L_5$  is the inductor in Fig. 5 (a) ; $L_4$  and  $L_6$  are the conventionally differential inductor with the same width and turns as  $L_3$  and  $L_5$ , respectively.

#### **3. 3 Prediction errors**

Table 1 is the prediction errors of the inductors with the DCM. The prediction error of  $f_{SR}$ with the DCM is less than 10 %, demonstrating the accuracy of the DCM. The DCM would have higher accuracy for the different structure inductors if the current crowding effects are considered in assumption (2).

| Table 1 | Prediction | errors | with | DCM |  |

|---------|------------|--------|------|-----|--|

|---------|------------|--------|------|-----|--|

| f SR     | L <sub>1se</sub> | $L_{2se}$   | L <sub>3se</sub>   | L <sub>4se</sub> | L <sub>5se</sub> | L <sub>6se</sub> |

|----------|------------------|-------------|--------------------|------------------|------------------|------------------|

| Error/ % | 6.4              | 8.2         | 5.6                | 7.3              | 6.7              | 7.2              |

| f sr     | $L_{1 diff}$     | $L_{2diff}$ | L <sub>3diff</sub> | $L_{4 diff}$     | $L_{5diff}$      | $L_{6diff}$      |

| Error/ % | 8.3              | 9.2         | 6.4                | 9.5              | 7.8              | 8.9              |

#### Conclusion 4

The DCMs of inductors are developed to accurately quantify the  $C_{m-m}$  and the  $C_{m-s}$  of the symmetric and single-ended inductor. The  $C_{m_s}$  of the differential inductor is only a quarter of the  $C_{m_s}$  of the single-ended inductor, therefore, the differential inductor has higher a Q and  $f_{SR}$ . The ratio of the  $f_{SR\_diff}$  to the  $f_{SR\_se}$  are firstly predicted and explained. Two optimum differential-inductors with low  $C_{m_m}$  are developed and validated.

**Acknowledgments** The authors would like to thank Prof. Sun Lingling, Dr. Hu Jiang of Hangzhou University of Electronic Science & Technology and Prof. Li Fuxiao, Shi Jiangwei of the Nanjing 55th Research Institute of Information Industrial Department for measurements.

### References

- [1] Burghartz J N, Rejaei B. On the design of RF spiral inductors on silicon. IEEE Trans Electron Devices ,2003 ,50(3) :718

- [2] Danesh M, Long J R. Differentially driven symmetric microstrip inductors. IEEE Trans Microw Theory Tech, 2002, 50 (1):332

- [3] Wu C H, Tang C C, Liu S I. Analysis of monolithic spiral inductors using the distributed capacitance model. IEEEJ Solid-State Circuits ,2003 ,38(6) :1040

- [4] Zolfaghari A, Chan A, Razavi B. Stacked inductors and transformers in CMOS technology. IEEE J Solid-State Circuits, 2001,36(4):620

- [5] Tang C C, Wu C H, Liu S I. Miniature 3-D inductors in standard CMOS process. IEEE J Solid-State Circuits, 2002, 37(4): 471

- [6] Tang Zhangwen. LC voltage-controlled oscillators. PhD Dissertation, Fudan University, 2004

- [7] Maget J. Varactors and inductors for integrated RF circuits in standard MOS technologies. PhD Dissertation, University of Bundeswehr ,Neubiberg , Germany ,2002

## 用分布电容模型分析和优化差分电感

菅洪彦 唐长文 何 捷 闵 昊

(复旦大学专用集成电路与系统国家重点实验室,上海 200433)

摘要:建立了预测片上等效寄生电容的片上电感分布电容模型.预测和解释了差分电感的自激振荡频率的差异. 实测数据显示 ,与单端驱动模式下的相同对称电感相比 .差分驱动模式电感提高最大品质因数 127 % .具有更大的 工作频率范围.设计和验证了低寄生电容的差分电感.

关键词:分布电容模型;自激振荡频率比;品质因素;差分电感;优化设计 EEACC: 2140; 2530B; 2550F **中图分类号**: TN405 文献标识码: A **文章编号**: 0253-4177(2005)06-1077-06

\*上海市科委资助项目(批准号:037062019)

©2005 中国电子学会

菅洪彦 男,博士研究生,研究方向为片上电感和片上天线的优化设计,射频电路设计(例如低噪声放大器、混频器和压控振荡器等),射频识 别天线设计. Email: hyjian @fudan. edu. cn 2004-11-14 收到,2005-02-01 定稿