Vol. 26 No. 6 June, 2005

## 适用于高品质射频集成电感的多孔硅 新型衬底制备技术 \*

## 周 毅 杨 利 张国艳 黄 如

(北京大学微电子所,北京 100871)

摘要:提出了背向选区腐蚀生长多孔硅的集成电感衬底结构. ASITIC 模拟证明,该新型衬底结构的集成电感在高频下仍具有较高的品质因子. 采用此工艺,在固定腐蚀液配比的条件下,变化电流密度和阳极氧化时间,制备出了高质量的厚膜多孔硅,并测量了多孔硅的生长厚度、孔径大小和表面形貌,得出了多孔硅生长速率随阳极氧化时间和电流密度的变化关系,为背向选区腐蚀工艺制备高品质硅基集成电感奠定了理论和实验基础.

关键词:射频集成电路;多孔硅;集成电感;品质因子

**PACC:** 3220D; 7230; 7740

中图分类号: TN405. 95 文献标识码: A 文章编号: 0253-4177(2005)06-1182-05

### 1 引言

随着移动电话、无线局域网以及数字电视等产业的蓬勃发展,CMOS 射频集成电路(RFIC)已经成为当今微电子和通信领域的研究热点之一[1]. 在硅(Si)衬底上制作射频集成电路,符合射频集成电路低成本、全集成的发展要求[2]. Si 衬底具有成本低、导热性好以及加工工艺成熟等优点,但是由于 Si 衬底的电阻率比较小,介电常数比较高,使得平面螺旋电感在衬底中产生较大的损耗,很难实现高品质因子(Q)的集成电感<sup>[3,4]</sup>,因此制作高 Q 值的集成电感已经成为当前 CMOS 射频集成电路面临的主要挑战之一.

从减小衬底损耗入手,人们尝试了多种方法来制作高Q值的集成电感,例如采用高电阻率硅衬底、聚酰亚胺层以及多层金属技术等,但效果都不甚理想 $^{[5,6]}$ .

近年来,一种常用且有效的方法是在多孔硅上制作集成电感,这是因为多孔硅具有高电阻率(大约

为 10<sup>6</sup>  $\cdot$ cm) 和低介电常数 (<10) 的特点 .使得衬 底损耗和耦合效应大大减小,从而取得0值较为理 想的片上集成电感 . 文献报道<sup>[7]</sup> ,电感值为 11. 4n H 的集成电感,在普通硅衬底和高电阻率的硅衬底上 制作的集成电感,Q值分别在 440 和 590 MHz 时达 到最大值,分别为12.5和19;而在300µm厚的多孔 硅衬底上制作的集成电感,在电感值相同的条件下, 当频率为  $15\,\mathrm{GHz}$  时,品质因子 Q 达到最大值  $45.\,\mathrm{U}$ 当多孔硅厚度减小时,Q 值会减小很多. 可见在高频 的情况下,在厚度较大的多孔硅衬底上(>300µm) 制作集成电感,是一种有效提高  $\varrho$  值的方法.在多 孔硅衬底上制作电感,通常的做法是先在硅衬底上 制备一层多孔硅,然后再在多孔硅上制备电感[8].这 种方法很容易造成硅片的严重污染,不利于其他有 源、无源器件的制备和射频电路的全集成,因此这种 方法不适于实际的大规模工业生产. 如果先采用常 规工艺制备射频集成电路 ,将正面保护起来 ,然后再 增加一步后序工艺,即在电感和需要隔离的衬底区 域进行背向选区电化学腐蚀,选择性地背向生长多 孔硅,这样既可以得到高o值的集成电感,提高电

<sup>\*</sup>国家自然科学基金资助项目(批准号:60306005)

周 毅 男,1981年出生,硕士研究生,主要从事射频电路衬底研究以及射频电路系统模拟.

杨 利 男,1977年出生,博士研究生,主要从事射频电路衬底研究以及射频电路模块设计.

黄 如 女,1969年出生,教授,主要从事新结构、新工艺的半导体器件研究及电路设计.

路的整体性能,又不会造成污染,适于射频集成电路的大规模生产.我们先采用 ASITIC 软件模拟证明了多孔硅衬底对集成电感性能有所提高,并探索了背向选区电化学腐蚀的厚膜多孔硅生长工艺,为射频集成电路背向选区电化学处理工艺提供了理论和实验基础.

## 2 设计和实验

#### 2.1 ASITIC 数值模拟

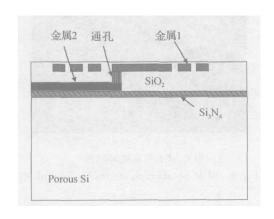

在进行多孔硅制备实验之前,我们使用了ASITIC 软件分别对制作在普通硅衬底和多孔硅衬底上的电感的 Q 值和电感值进行了数值模拟 (ASITIC 是 Berkeley 大学开发的一款免费软件,主要用于射频电路中对螺旋电感、变压器、电容和衬底耦合的建模和优化). 模拟过程中,以方形平面螺旋电感为例,电感的参数为金属线,宽度  $W=6\mu m$ ,线间距  $S=6\mu m$ ,金属线厚度 =  $1\mu m$ ,电感圈数 = 5,总线长  $170\mu m$ . 在电感和多孔硅中间是一层  $Si_3N_4$ ,其具体结构如图 1 所示.

图 1 多孔硅衬底上的集成电感示意图

Fig. 1 Schematic view of integrated inductor on PS substrate

#### 2.2 多孔硅的制备

实验所采用的原始材料为 p 型 100 硅片 ,电阻率为 3~5 ·cm. 为了实现良好的欧姆接触 ,在硅片正面溅射金属铝之前进行  $p^+$ 注入. 电化学腐蚀液是由 40 %的 HF 和乙醇近似以 1 1 的比例配制而成的 ,在腐蚀液中加入乙醇的目的是增大多孔硅的亲水性 ,并在反应过程中把产生的气泡带走. 有电感一侧的硅片制备为正面 ,接电源正极 :浸入 HF 溶液

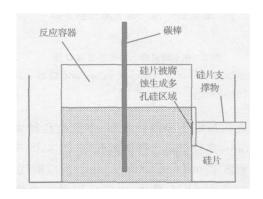

的碳棒接电源负极. 在进行电化学腐蚀的时候,让没有电感的一侧,即硅片反面与腐蚀液接触. 硅片在腐蚀前,需要做一些处理,在硅片反面采用抗 HF的材料把正面对应的没有电感的区域保护起来,留出电感所对应的需要腐蚀的区域和 HF接触,这样便达到了选区腐蚀的目的. 在硅片正面,焊细铜丝引出接电源正极. 腐蚀装置如图 2 所示.

图 2 电化学腐蚀装置示意图

Fig. 2 Schematic view of electrochemistry equipment

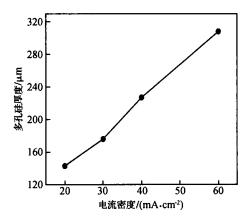

多孔硅的生长速率取决于 HF的浓度和电流密度大小<sup>[9]</sup>.本实验分为两组.一组是时间为常数,恒定为 2h,改变电流密度的大小,分别为 20,30,40,60mA/cm²,测量生成多孔硅的厚度;另一组是电流密度设为常数,设定为 30mA/cm²,改变反应时间,分别为 2.5,3.0,3.5,4.0,5.0h,测量生成多孔硅厚度.实验环境为恒温(大约 22 ),所制备样品的表面和截面形貌观测采用 FEI 公司的环绕扫描电子显微镜(ESEM,型号为 QUANTA 200F).

## 3 结果与分析

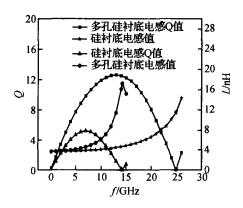

分别在硅衬底和多孔硅衬底的条件下,频率  $100 \, \mathrm{MHz} \sim 26 \, \mathrm{GHz}$  范围内,对上述的电感进行仿真,如图  $3 \, \mathrm{m}$  示. 分析发现硅衬底上的电感 Q 值在  $7 \, \mathrm{GHz}$  左右达到最大值,为 7.83,自谐振频率为  $21.74 \, \mathrm{GHz}$ ;而在多孔硅衬底上的电感 Q 值在  $13 \, \mathrm{GHz}$  左右达到最大值,为 12.61,自谐振频率为  $24.09 \, \mathrm{GHz}$ . 从中可以看出基于多孔硅衬底的电感 Q 值大约提高了 61%,谐振频率提高了 10.8%. 尤其在频率大于  $7 \, \mathrm{GHz}$  的范围内,两者差距尤为明显,这说明在射频集成电路中多孔硅衬底对提高平面集成电感的 Q 值和自谐振频率起了很大的作用.

图 3 在不同衬底上的电感值和 Q 值

Fig. 3 Comparison of inductor values and Q as a function of frequency

通过扫描电子显微镜观察,多孔硅孔径大小约为  $1\sim 2\mu m$ ,并且有相当高的多孔率,图 4,图 5分别为电流密度  $20mA/cm^2$ , $40mA/cm^2$ ,反应时间为 2h的多孔硅表面 SEM 照片.由图可以看出电流密度的大小对多孔硅孔径大小有一定影响,孔径大小和电流密度成正比.图 6为电流密度  $30mA/cm^2$ ,反应时间 4h 的多孔硅截面图,此时多孔硅平均厚度大约为  $354\mu m$ ,厚度十分均匀,多孔硅与硅的界面非常平直,并与生长方向垂直,说明多孔硅的生长速率非常稳定.多孔硅表面稍显粗糙,是由于多孔硅表面在空气中氧化所致.这种厚膜多孔硅对制作高 Q 值的集成电感有很大的帮助.

图 4 20mA/cm² 多孔硅表面 SEM 照片 Fig. 4 SEM photograph of PS surface with 20mA/cm²

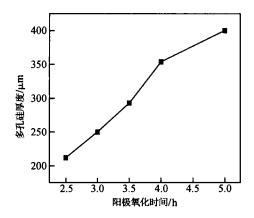

对于在不同条件下生成的多孔硅,分别以氧化时间、氧化电流密度为横轴,生成的多孔硅厚度为纵

图 5 40mA/cm<sup>2</sup> 多孔硅表面 SEM 照片 Fig. 5 SEM photograph of PS surface with 40mA/cm<sup>2</sup>

图 6 多孔硅截面 SEM 照片 Fig. 6 SEM photograph of cross section of PS

轴绘制两条曲线,如图 7,8 所示. 从两条曲线可以看出,在电流密度恒定(30mA/cm²)的情况下,多孔硅厚度与氧化时间近似成线性关系,也就是生成多孔硅速率保持恒定,速率大约是 80µm/h;在氧化时间一定的情况下,多孔硅厚度和电流密度也近似有着线性关系. 因此在 HF浓度一定的情况下,通过控制电流密度和反应时间,就可以比较精确地得到所期望的多孔硅厚度.

在成功地制备多孔硅衬底的基础上,我们进一步对电感的硅衬底进行多孔硅化实验,所得的电感 Q值以及自谐振频率等电学特性参数结果将会进一步给出.

图 7 氧化时间与多孔硅厚度关系曲线

Fig. 7 Comparison of depth of PS as a function of time

图 8 电流密度与多孔硅厚度关系曲线

Fig. 8 Comparison of depth of PS as a function of current density

## 4 结论

射频集成电感的 Q 值偏低一直是工业界没有解决的难题,这对于射频电路的发展是一个很大的制约因素. 在厚膜多孔硅衬底上制作电感能够极大地减小衬底损耗,对提高电感 Q 值有着积极的意义. 本文采用 ASITIC 软件模拟证明了多孔硅衬底对集成电感性能的提高,在此基础上探索了背向选区电化学腐蚀的厚膜多孔硅生长工艺,为射频集成电路背向选区电化学处理工艺提供了理论和实验基础. 实验采用不同的电流密度以及不同的反应时间,得到了厚度均匀、孔径大小合适的厚膜多孔硅衬底,

其中最大厚度达到 400µm,完全符合作为衬底的多孔硅所要求的 300µm 理论值厚度.整个实验工艺简单、可重复性强,并且与常规的 CMOS 工艺完全兼容.更为重要的是,多孔硅衬底的生成作为后续工艺,将在整个电路制作完备的基础上进行,不会对电感以及其他的器件造成污染和损伤,这是与以往报道在已经生成的多孔硅衬底上实现器件和电路的最大不同之处.

#### 参考文献

- [1] Kim H S Jenkins K A, Xie Y H. Effective crosstalk isolation through p<sup>+</sup> Si substrates with semi-isulating porous Si. IEEE Electron Device Lett, 2002, 23:160

- [2] Long Yongfu, Zhu Ziqiang, Lai Zongsheng, et al. A low-loss interlayer thick layer of porous silicon and oxidized porous silicon for application to the microwave/RFIC. Chinese Journal of Semiconductors, 2002, 23(6):609 (in Chinese) [龙永福,朱自强,赖宗声,等.用于微波/射频集成电路的一种新型低损耗介质-多孔硅及氧化多孔硅厚膜.半导体学报, 2002, 23(6):609]

- [ 3 ] Nguyen N M, Meyer R G. Si IC-compatible inductors and LC passive filters. IEEE J Solid-State Circuits, 1990, 25:1028

- [4] Lovelace D, Camilleri N. Silicon MMIC inductor modeling for high volume ,low cost applications. Microwave J, 1994:60

- [5] Soyuer M, Burghartz J N Jenkins K A, et al. Multilevel monolithic inductors in silicon technology. Electron Lett, 1995, 31

(5):359

- [ 6 ] Burghartz J N, Soyuer M, Jenkins K A, et al. High-Q inductors in standard silicon interconnect technology and its application to an integrated RF power amplifier. IEDM 95, 1995: 1015

- [7] Royet A S, Cuchet R, Pellissier D, et al. On the investigation of spiral inductors processed on Si substrates with thick porous Si layers. European Solid-State Device Research, 2003:

- [8] Kim H S, Xie Yahong. Unoxidized porous Si as an isolation material for mixed-signal integrated circuit applications. J Appl Phys, 2003, 93(7):4226

- [9] Zhou Jun, Wang Xiaohong, Yao Pengjun, et al. Analysis and design of an accelerometer fabricated with porous silicon as sacrificial layer. Chinese Journal of Semiconductors, 2003, 24 (7):687

# Fabrication of a Porous Silicon New Substrate for a High Q Radio Frequency Integrated Inductor $^{\star}$

Zhou Yi, Yang Li, Zhang Guoyan, and Huang Ru

(Institute of Microelectronics, Peking University, Beijing 100871, China)

**Abstract:** A new method to grow porous silicon substrate from the back-end of silicon substrate is presented. High Q integrated inductors can be obtained at high frequencies with this kind of substrate, which has been proved by ASITIC simulator. High quality and thick porous silicon films are fabricated using this new technique. The influence of the velocity of growth, time and current density on the porous silicon is achieved. The results can serve as a guideline for fabricating high quality integrated inductors based on silicon substrate.

Key words: radio frequency integrated circuit; porous silicon; integrated inductor; quality factor

PACC: 3220D; 7230; 7740

**Article ID**: 0253-4177 (2005) 06-1182-05

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60306005)

Zhou Yi male, was born in 1981, graduate student. His research interests are in the substrates of RF circuits and RF systems simulation.

Yang Li male, was born in 1977, PhD candidate. His research interests are in the substrates of RF circuits and RF blocks design.

Huang Ru female, was born in 1969, PhD, professor. Her research interests are in novel structure devices, novel process, device modeling, and circuit design.