# Preparation of Semi-Insulating Material by Annealing Undoped InP

Zhao Youwen<sup>1</sup>, Dong Hongwei<sup>1</sup>, Jiao Jinghua<sup>1</sup>, Zhao Jianqun<sup>1</sup>, Lin Lanying<sup>1</sup>, Sun Niefeng<sup>2</sup> and Sun Tongnian<sup>2</sup>

(1 Materials Science Center & Materials Science Laboratory, Institute of Semiconductors,

The Chinese A cademy of Sciences, Beijing 100083, China)

(2 Hebei Semiconductor Research Institute, Shijiazhuang 050051, China)

Abstract: Semi-insulating (SI) InP wafers of 50 and 75mm in diameter can be obtained by annealing of undoped liquid encapsulated Czochralski (LEC) InP at 930°C for 80h. The annealing ambient can be pure phosphorus (PP) or iron phosphide (IP). The IP-SI InP wafers have good electrical parameters and uniformity of whole wafer. However, PP-SI InP wafers exhibit poor uniformity and electrical parameters. Photoluminescence which is subtle to deep defect appears in IP-annealed semi-insulating InP. Traps in annealed SI InP are detected by the spectroscopy of photo-induced current transient. The results indicate that there are fewer traps in IP-annealed undoped SI InP than those in as-grown Fe-doped and PP-undoped SI InP. The formation mechanism of deep defects in annealed undoped InP is discussed.

Key words: indium phosphide; semi-insulating; annealing

PACC: 6110C; 8160; 7120

CLC number: T N 304. 2\* 3 Document code: A Article ID: 0253-4177 (2002) 03-0285-05

#### 1 Introduction

InP is an important semiconductor material for the fabrication of opto-electronic and microwave devices. The wide-band communication system of 40GB will appreciate and adopt InP-based devices and components. To manufacture devices of superior performance, such as heterojunction bipolar transistor (HBT) and high electron mobility transistor (HEMT), semi-insulating (SI) InP substrate with good uniformity and thermal stability is needed. The commercial SI InP wafer is prepared by Fe doning with a concentration for more than  $10^{16} \, \mathrm{cm}^{-3}$  in the process of crystal growth [1-3]. However, there are some disadvantages, such as out-diffusion

of Fe into the epitaxial layer<sup>[4]</sup>, and radial and axial non-uniformity caused by impurity segregation effects<sup>[5,6]</sup>, etc., of the SI InP substrate with high concentration of Fe. These disadvantages are harmful to the epitaxial growth and performance of InP-based devices. Although new technologies for growth, such as double crucible growth, have been worked on to avoid the shortcomings of Fe-doped SI InP<sup>[7]</sup>, SI InP with low concentration of Fe-doping and with good uniformity is still not available reproducibly.

It has been found that the carrier concentration of undoped LEC grown InP decreases significantly after annealing [8-10]. SI sample can be obtained by annealing undoped InP at high temperature for several tens hours [11-13]. Reproducible

preparation of standard SI InP wafers by using this method has been limited due to the requirement of high purity of undoped InP<sup>[12]</sup>.

In this paper, we report the reproducible preparation of SI wafers at high temperature to anneal undoped InP in the ambient of pure phosphorus (PP) or iron phosphide (IP). The defects in such SI InP wafers have been studied by using photoluminescence (PL) spectroscopy and photo-induced current transient spectroscopy (PICTS).

### 2 Experimental procedure

InP wafers were sliced from LEC grown ntype undoped InP ingots with diameters of 50 or 75mm. At room temperature, the free electron concentrations of the wafers are about  $(2 \sim 6) \times 10^{15}$ cm<sup>-3</sup>. Before annealing, the wafers were etched, cleaned and dried. Then, the wafers were put on a wafer holder and charged into a quartz tube that had been evacuated. A quantity of red phosphorus or phosphorus mixed with iron powder were also put into the tube to give more than 10<sup>5</sup>Pa of phosphorus pressure to avoid the decomposition of InP wafers in the annealing process. The quartz tube was evacuated to a pressure of 1.33Pa, was fused and charged into a furnace. The temperature in the tube was controlled by a computer in the whole process of annealing. The wafers were annealed at 930°C for 80h, then cooled to room temperature slowly.

Samples of annealed undoped InP were measured by conventional Hall effect to get the electrical parameters. PL spectra of annealed InP were measured by using a Brucker ISF120 system at 10K. PICTS of undoped SI InP were obtained in a home-made measurement system. One side of chemi-mechanically polished samples was used for the measurements.

#### 3 Results

High purity of undoped InP with carrier con-

centration of  $2\times10^{15} \, \mathrm{cm}^{-3}$  and mobility of  $4000 \, \mathrm{cm}^2/$  (V • s) can be changed to SI by annealing in PP ambient. The resistivity and mobility of such a sample are  $10^6 \Omega$  • cm and  $1800 \, \mathrm{cm}^2/(\mathrm{V} \cdot \mathrm{s})$ , respectively. Good SI wafers with resistivity of higher than  $10^7 \Omega$  • cm, mobility of  $3000 \, \mathrm{cm}^2/(\mathrm{V} \cdot \mathrm{s})$  can be obtained by annealing undoped InP with carrier concentration below  $6\times10^{15} \, \mathrm{cm}^{-3}$  in IP ambient.

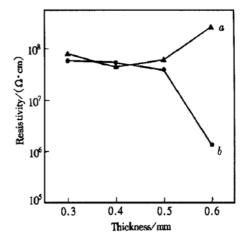

To check the axial uniformity of IP-SI InP, two samples were thinned to different thickness for Hall effect measurement. The results are shown in Fig. 1. It can be seen that the samples exhibit uniform SI property from surface to internal regions.

Fig. 1 Resistivity profiles of two IP-SI InP samples Before annealing, the two undoped InP samples are in different carrier concentrations: Curve  $a\ 2\times10^{15} {\rm cm}^{-3}$  and  $b\ 6\times10^{15} {\rm cm}^{-3}$ .

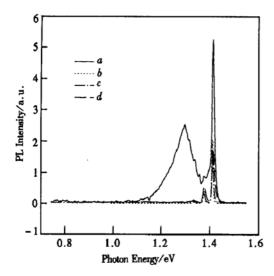

PL spectra of four samples are shown in Fig. 2. The sample a is an as-grown undoped InP wafer. The sample b and sample c were annealed in the ambient of PP and IP, respectively. Before annealing, they were cut from one undoped InP wafer with carrier concentration of  $6 \times 10^{15}$  cm<sup>-3</sup>. The sample d is an annealed in IP ambient, and undoped InP that has carrier concentration of  $1.2 \times 10^{16}$  cm<sup>-3</sup> before annealing. The sample c is the only semi-insulating material among the four samples. A noticeable broad PL peak at 1.30eV can be observed in the PL spectrum of sample c, while there is no such peak in the spectra of other three samples.

Fig. 2 Photoluminescence spectra of four annealed undoped InP samples at 10K Curve a: IP-annealed SI InP; b: IP-annealed semiconducting InP; c: PP-annealed semiconducting InP, and d: PP-annealed SI InP Before annealing, samples correspond to curves a and c were cut from one wafer. The curves have been moved vertically for clarity.

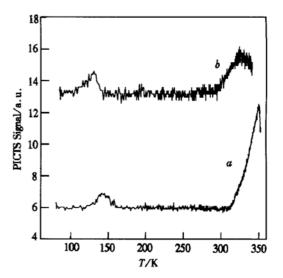

The PICTS results of the samples of as-grown Fe-doped and an IP annealed undoped SI InP are shown in Fig. 3. Only two defects were found in the undoped IP-SI InP sample. It seems that undoped IP-SI InP has fewer defects than those in Fe-doped SI InP and undoped PP-SI InP reported before [14,15].

### 4 Discussion

The low mobility and high resistivity of PP-annealed InP imply the formation of compensation semiconductor due to the annihilation of native donor after annealing [16,17]. The uniformity of such material will be poor as evidenced by PL mapping which will be discussed in a separate publication. In contrast, IP-annealed InP has good electrical property and uniformity. This is the result of strong compensation of Fe that was diffused into the wafer in the annealing process. By comparison of PL spectra shown in Fig. 2, it can be concluded that the diffusion of Fe induces defects in addition to

Fig. 3 PICTS spectra of two IP-annealed undoped SI InP samples at rate windows of 100/s (curve a) and 50/s (curve b) respectively. The curves have been moved vertically for clarity.

the well-known mid-gap Fe<sup>2+</sup> /Fe<sup>3+</sup> defects in the annealing process. This statement can be supported by the fact that there are no 1.3eV peaks in the PL spectra of as-grown Fe-doped SI InP<sup>[3]</sup>, PP-annealed undoped SI and semiconducting InP and PP-annealed Fe pre-doped InP<sup>[12,18]</sup>. The study in detaile of the formation and property of 1.3eV peak related defect would be published elsewhere.

On the other hand, PICTS of IP-annealed SI InP indicates that two defects were formed in the annealing process. The shallow one is around 0. 2eV below conduction band and the deep one is at 0.64eV below conduction band. The latter is definitely a Fe deep acceptor level Fe2+ /Fe3+ . However, the origin of the shallow is not clear. A obvious fact is that the defects in IP-annealed SI InP are much fewer than those in SI InP prepared by annealing undoped[12] and Fe pre-doped[18] InP in the ambient of PP. Since indium vacancy defect is formed by the thermal dissociation of the hydrogen indium vacancy complex V<sub>In</sub>H<sub>4</sub><sup>[19]</sup>, one possible reason is that the diffusion of Fe atom into the wafer leads to the occupation of a part of indium vacancy site, preventing the further formation of defects in the material.

#### 5 Summary

Good quality semi-insulating wafers can be prepared reproducibly by annealing undoped LEC InP at 930°C in a controlled ambient of iron phosphide. The electrical property and uniformity of whole wafer of IP-SI InP are much better than those of as-grown Fe-doped SI InP. Optical active defects related with the Fe diffusion in IP-SI InP have been formed in the annealing process. IP-SI InP has fewer defects than those of SI InP obtained by annealing undoped and Fe pre-doped LEC InP.

Acknowledgements Thanks to the members of the group to study indium phosphide for their help of this work. Thanks are also given to Dr. Chen Yonghai and Ms. Zhang Yanhua for their assistance in the PL and PITCS measurements.

#### References

- [1] Iseler G W. Proc 7<sup>th</sup> Int Symp GaAs and Related Compounds, 1978, 1979: 144

- [2] Lambert B, Coquille R, Gauneau M, et al. Semicond Sci Technol, 1990, 5: 616

- [3] Erman M, Gillardin G, Le Bris J, et al. J Crys Growth, 1989,

96: 469

- [4] Holmes D E, Wilson R G, Yu P W. J Appl Phys, 1981, 52: 3396

- [5] Longère J Y, Schohe K, Krawczyk S K. J Appl Phys, 1990,68: 755

- [6] L'Haridon H, Callec R, Coquillé R, et al. J Cryst Growth, 1991, 113: 39

- [7] Fornari R, Gilioli E, Moriglioni M, et al. J Cryst Growth, 1998, 166: 572

- [8] Guha S, Hasegawa F. Solid State Electron, 1977, 20: 27

- [ 9 ] Tsubaki K, Sugiyama K. Jpn J Appl Phys, 1980, 19: 1185

- [10] Yamazoe Y, Sasai Y, Nishno T, et al. Jpn J Appl Phys, 1980, 20: 347

- [11] Hofmann D, Müller G, Streckfuss N. Appl Phys A, 1989, 48: 315

- [12] Kainosho K, Shimakura H, Yamamoto H, et al. Appl Phys Lett, 1991, 59: 932

- [13] Fornari R, Brinciotti A, Gombia E, et al. Mater Sci Eng B1994, 28: 95

- [14] Marrakchi G, Cherkaoui K, Karoui A, et al. J Appl Phys, 1996, 79: 6947

- [15] Hirt G, Wolf D, Müller G. J Appl Phys, 1993, 74: 5538

- [16] Wolf T, Bimberg D, Hirt D, et al. 4<sup>th</sup> conference on InP and related materials, New Port, Rhode Island, 1992

- [17] Zhao Y W, Xu X L, Gong M, et al. Appl Phys Lett, 1998, 72: 2126

- [18] Uchida M, Oda O, Warashina M, et al. J Electrochem Soc, 1998, 145: 1048

- [19] Darwich R, Pajot B, Rose B, et al. Phys Rev, B1993, 48: 17776

## 高温退火非掺杂磷化铟制备半绝缘材料

赵有文' 董宏伟' 焦景华' 赵建群' 林兰英' 孙聂枫' 孙同年'

(1 中国科学院半导体研究所 材料中心及材料科学开放实验室, 北京 100083) (2 河北半导体研究所, 石家庄 050051)

摘要:对液封直拉(LEC) 非掺磷化铟(InP) 进行 930℃ 80h 的退火可重复制备直径为 50 和 75mm 的半绝缘 (SI) 衬底. 退火是在密封的石英管内纯磷(PP) 或磷化铁(IP) 两种气氛下进行的. 测试结果表明 IP-SI InP 衬底具有很好的电学性质和均匀性,而 PP-SI 的均匀性和电学参数都很差. 在 IP-SI 样品的 PL 谱中出现与深缺陷有关的荧光峰. 光激电流谱的测量结果表明: 在 IP 气氛下退火获得的半绝缘磷化铟中的缺陷明显比 PP-SI 磷化铟的要少. 并对退火后磷化铟中形成缺陷的机理进行了探讨.

关键词:磷化铟;半绝缘;退火 PACC: 6110C; 8160; 7120

中图分类号: TN 304. 2\*3 文献标识码: A 文章编号: 0253-4177(2002)03-0285-05