# A 1. 45GHz LNA with Low Power, Wide Variable Gain Range and Ultra Low Noise Degradation\*

Lin Min, Wang Haiyong, Li Yongming and Chen Hongyi

(Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

Abstract: A LNA with a novel variable gain solution is presented. Compared with the conventional variable gain solutions of LNA, which have more noise degradations when in low gain mode, this solution gives about 25dB variable gain range in 3dB steps, which would cause ultra low noise figure degradation by 0.3~ 0.5dB. In addition, extra power consumption is not needed by this solution compared with other solutions.

Key words: LNA; variable gain; noise degradation; low power

EEACC: 1205; 1220; 2570D

CLC number: TN722.3 Document code: A Article ID: 0253-4177(2004) 08-0903-05

#### 1 Introduction

In a typical RF receiver, the low noise amplifier (LNA) should have low noise figure to increase sensitivity of the receivers and high linearity to prevent interference from undesired adjacent-channel signals. To increase dynamic range of the receivers and to reduce linearity requirement for the downconversion mixers, the LNA should provide variable gain. When the RF input power is large, the gain of the LNA should be reduced.

## 2 Conventional variable gain solutions for LNA

There are some variable gain solutions for LNA in published literatures. Current splitting gain-control technique and resistor chain gain-control technique are widely used.

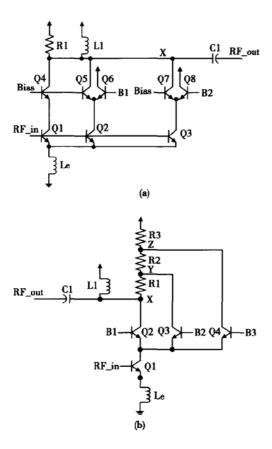

LNA gain can be controlled in discrete steps by current-splitting technique as shown in Fig. 1 (a)<sup>[1]</sup>. Transistors Q1, Q2, and Q3, form a common-emitter transconductance stage which converts RF input voltage into current. Transistor pairs Q5-Q6 and Q7-Q8 form current steering switches. In the high gain mode, all output current of the transconductance stage is injected into node X. In the low gain mode, the output currents of Q2 and Q3 are dumped to the power supply. This reduces LNA gain. In medium gain mode, only output current of Q3 is dumped to the power supply. In this gain-control scheme, the gain step between successive gain modes is quite large in order to get wide dynamic range. Although it is quite easy to implement this gain-control scheme, some disadvantages prevent it from realization. One is that the LNA employing current-splitting technique has

<sup>\*</sup> Project supported by National Natural Science Foundation of China (No. 60236020)

Lin Min was born in 1974, PhD candidate. His current research interest includes the characterization and modeling of passive components and interconnects at radio frequency.

Wang Haiyong was born is 1976, PhD candidate. His current research interest includes CMOS RFICs and mixed-signal integrated circuits

Li Yongming professor. His current interests include the design of analog integrated circuits and the speech signal processing.

high noise figure in low gain mode because of dumping away some of the signal currents at output. In some applications, however, little noise figure degradation is allowed in the LNA low gain mode. The reason is the interference levels increase when the desired signal power increases [2]. To have large signal-to-noise-plus-interference ratio (SINR), the noise figure of the LNA should remain low to allow margin for handling interference. Another disadvantage is that it consumes almost twice the current of the LNA without gain control circuits.

Fig. 1 Conventional variable gain solutions for

LNA (a) Current splitting gain control technique;

(b) Resistor chain gain control technique

A gain-control technique with less noise figure degradation in low gain mode is shown in Fig. 1 (b) [3]. Resistors R1, R2, and R3 form a resistor chain. Inductor L1 and capacitor C1 form an impedance transformation network to transform the resistance at node X to match that of the load

resistor (not shown in Fig. 1 (b)). In high gain mode, the voltage at node B1 is set to an appropriate bias voltage while Q3 and Q4 are disabled. Hence, transistor Q2 functions as cascode transistor of the transconductance stage. The gain of the LNA is the highest in this mode because the output current is injected into node X, which has the highest resistance in the resistor chain. The medium gain is realized by disabling Q2 and Q4, and letting Q3 be the cascode transistor to inject output current into node Y. In low gain mode, output current is injected into node Z, which has the lowest resistance in the resistor chain. Since both signal and noise currents of the transconductance stage are injected into the same node, the output SNR and the noise figure of the LNA are degraded only slightly in low gain mode. One disadvantage of this scheme is that the resistor chain reduces voltage headroom and increases the supply voltage about 1V provided RLOADmax = 200Ω and IDC = 5mA, which is necessary for sufficient gain and linearity [4]. Another disadvantage is that the gain step of the LNA is sensitive to parasitic impedance in the resistor chain and the impedance transformation network [5]. The amount of noise figure degradation in this scheme is about 2dB when the gain reduces from 16dB to 4dB.

### 3 Proposed variable gain solution for LNA

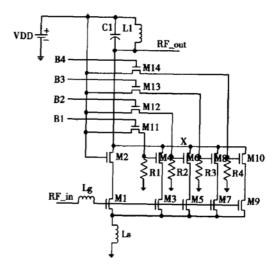

To acquire wide variable gain range and minimum noise figure degradation with no extra power consumption, a novel variable gain solution for LNA is proposed as shown in Fig. 2. Common source configuration with inductive degeneration is used as transconductance stage. Input device and cascode device are split into five different sizes of device pairs, such as M1/M2, M3/M4, M5/M6, M7/M8, and M9/M10. The gates of cascode devices M4, M6, M8, and M10 are connected to the gate of M2 through four switches M11 ~ M14, which are large size of devices to reduce on-resis-

tance. In addition, four grounded large resistors R1 ~ R4 are connected to the gates of M4, M6, M8, and M 10. The drains of the five cascode MOSFETs are connected to power supply through an on-chip spiral inductor L1 and capacitor C1. When B1~ B4 are set to digital voltage "0", the four switches are turned off and the four correspondent cascode devices' gates are set to "by the four grounded resistors. No DC current flows through the four signal paths and the gain of the LNA is reduced to the minimum. When B1~ B4 are set to digital voltage ", the four switches are turned on and the four correspondent cascode devices' gates are set to the same bias voltage as M2. There is DC current flowing through all signal paths and the gain of the LNA is the highest at that time. If B1~ B4 are set to different digital voltage combinations, a variable gain range with different gain steps is achieved. The gain step is dependent on the device size ratio, which is 1:1:2:4:8 in this paper to easily get 3dB step variable gain. No matter what state the switches are in, all the input devices are in saturation so that the input impedance match would not be affected by the states of the switches'. To meet the requirement of output impedance match, capacitance C1 is somewhat large to reduce capacitance variation of node X due to the switches' on and off. As DC current in all signal paths is used for amplification, no extra power consumption is needed as the solution in Fig. 1(a). Inductor L1 is used to reduce the supply voltage. When the switches are on, the signal-to-noise ratio (SNR) degradation in all these turned-on signal paths is the same so that the overall SNR degradation equals to that of any turned-on signal path. When the switches are off, the turned-off signal paths are high impedance paths whose noise contribution is much less than the input noise so that SNR degradation in turnedoff signal paths is small enough to be neglected and the overall SNR degradation still equals to that of any turned-on signal path. This is the principle that the proposed variable gain solution can achieve ultra low noise figure degradation in low gain

state.

Fig. 2 Proposed novel variable gain solution for LNA

#### 4 Experimental results

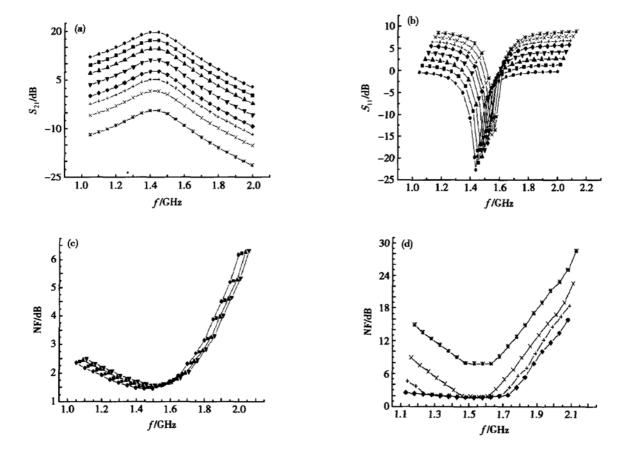

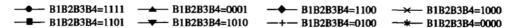

To validate the above analysis, experiment is carried out under DONGBU 0. 25µm mixed-signal CMOS process. The LNA is designed for 1.45GHz digital audio broadcast (DAB) application. The circuit draws maximum current 4.85mA from 1.5V supply voltage. When B1~ B4 are set to a set of appropriate combinations of digital voltage "0" and "1", 3dB step variable gain can be achieved in 25dB variable gain range. Figure 3(a), (b), (c), and (d) give experimental results of forward gain (S21), input return loss (SII), and noise figure (NF), respectively, under the same B1~ B4 combinations. From these curves, it is easily seen that the NF of LNA changes from 1.4dB to 1.9dB when the gain changes from 20dB to 2dB. NF increases abruptly when the LNA becomes loss. As the analysis mentioned above, the input match is not evidently affected by the gain variation. The power consumption also decreases with the decrease of LNA gain. The experimental results testify the advantages of proposed variable gain solution for LNA over the conventional solutions.

#### 5 Conclusion

A novel variable gain solution for LNA is introduced and discussed. Analysis and experimental results show that the LNA employing this variable gain solution can achieve a wide variable gain range of 25dB in 3dB step. The maximum power con-

sumption of the LNA is about 7.5mW and no extra power consumption is needed compared with other solutions. In addition to the minimum noise figure of 1.4dB when the gain of the LNA is 20dB, ultra low noise figure degradation of 0.3~ 0.5dB can be acquired easily when the gain of the LNA reduces from 20dB to 2dB.

Fig. 3 Experimental results of the proposed variable gain solution (a)Forward gain  $S_{21}$ ; (b)Input return loss  $S_{11}$ ; (c)Noise figure NF(1 $\sim$ 4); (d)Noise figure NF(5 $\sim$ 8)

**Acknowledgement** The authors would like to thank DONGBU Electronics for their supports and Zhao Guoguang from IMETU for technical discussions.

#### References

[1] Hull C D, Tham J L, Chu P R. A direct-conversion receiver for

900MHz (ISM band) spread-spectrum digital cordless telephone. IEEE J Solid-State Circuits, 1996, 31(12): 1955

- [2] Lin Min, Wang Haiyong, Li Yongming, et al. A novel IP3 boosting technique using feedforward distortion cancellation method for 5GHz CMOS LNA. IEEE Radio Frequeny Integrated Circuits (RFIC) Symposium, 2003: 699

- [ 3 ] Fong K L. Dual-band high-linearity variable-gain low-noise amplifier for wireless applications. IEEE International Solid-State Circuit Conference, 1999: 224

[4] Lin Min, Wang Haiyong, Li Yongming, et al. Design and test of 2-GHz CMOS RF low noise amplifier. Acta Electronica Sinica. [5] Razavi B. RF microelectronics. Prentice Hall PTR: Upper 2002, 30(9): 1278(in Chinese)[林敏,王海永,李永明,等. 2GHz CMOS RF 低噪声放大器的设计和测试. 电子学报,

2002, 30(9): 1278]

Saddle River NJ 07458, 1998

### 一种低功耗、宽变增益范围、极小噪声恶化的 1. 45GHz LNA\*

林 敏 王海永 李永明 陈弘毅

(清华大学微电子学研究所, 北京 100084)

摘要: 给出了一种新型的低噪声放大器的变增益方案. 与传统的噪声恶化很严重的低噪声放大器变增益方案相比, 该方案以 3dB 为步长, 可以得到 25dB 的变增益范围, 并且在低增益时的噪声恶化只有 0.3~ 0.5dB. 此外, 这种变 增益方案与传统方案相比,还有不需要额外功耗的优点.

关键词: 低噪声放大器; 变增益; 噪声恶化; 低功耗

EEACC: 1205; 1220; 2570D

中图分类号: TN722.3 文献标识码: A 文章编号: 0253-4177(2004)08-0903-05

<sup>\*</sup> 国家自然科学基金资助项目(批准号: 60236020)

林 敏 1974年出生,博士研究生,主要研究兴趣为模拟射频集成电路设计,包括低噪声、低功耗射频电路设计,功率放大器的线性化以及 数模混合集成电路设计.

王海永 1976年出生,博士研究生,主要研究兴趣包括数模混合集成电路的设计和模拟射频集成电路设计.

李永明 研究员,主要研究领域包括大规模模拟集成电路设计、无线局域网芯片组设计和语音信号处理技术.