# A Novel NeuMOS Source Follower Cell with High Precision

Yang Yuan, Gao Yong, Yu Ningmei and Liu Mengxin

(Department of Electronics Engineering, Xi'an University of Technology, Xi'an 710048, China)

Abstract: A novel neuMOS source follower circuit is presented. The cell can complete the source follower function even if the input voltage is lower than the threshold of the source follower, thus high-precision operation of the circuit is achieved. The simulation and the measurement results show that its precision is higher than that of other neuMOS source follower circuits.

Key words: neuron MOS; source follower; threshold

EEACC: 2570D

CLC number: TN432

Document code: A

Article ID: 0253-4177(2004)09-1074-05

#### 1 Introduction

Since the neuron MOS (abbreviated as neu-MOS) structure was presented by Shibata and Ohmi in Japan<sup>[1]</sup> in 1991, in many neuMOS application circuits such as neural network circuit [2], matched filter[3] and so on, the neuMOS source follower has been widely used. However, the biggest shortcoming of the source follower is that there is a threshold loss between the output and the input signal. Thus, some circuits to eliminate the threshold are developed [4]. But in these circuits, when the input voltage is less than the threshold of the source follower, the output keeps a constant value, which still leads to voltage errors. In this paper, a novel neuMOS source follower circuit is presented and the circuit performance is analyzed in details. The simulation result shows that the output voltage can well follow the input voltage even if the input volt-

age is lower than the threshold of the source follower. Finally the experiment result proves that the circuit can operate properly.

#### 2 Circuit structure and operation principle

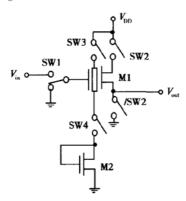

The circuit consists of two MOS transistors M1 and M2 and some assistant switches as shown in Fig. 1. M 1 and M 2 have the same threshold value Vth except that M1 is N channel neuMOS and M2 is N channel normal MOS. The floating gate of neuMOS M1 is connected to V DD through SW3 and the drain of M2 through SW4. The input signal V in is applied to the input gate of neuMOS M1 through SW1. The source voltage of M1 is the output  $V_{\text{out}}$ . In order to reduce the substrate bias effect, the substrates of two MOS transistors M1 and M2 are both connected to their sources. In addition, in order to get good switch characteristics of the

<sup>\*</sup> Project supported by National Natural Science Foundation of China (No. 60276017)

Yang Yuan female, was born in 1974, PhD candidate. Her current research interests focus on the novel devices and their new application. Gao Yong male, was born in 1956, professor. His research interests are novel power semiconductor devices, ICs CAD and integrated opto-

switches, CMOS transmission gate is used as SW1 because its transmission signal is analog input signal. SW2 and SW3 are PMOS transmission gates for power voltage VDD is connected to them, and /SW2 and SW4 are NMOS transmission gates for lower voltage terminals are connected to them.

Fig. 1 Source follower circuit structure

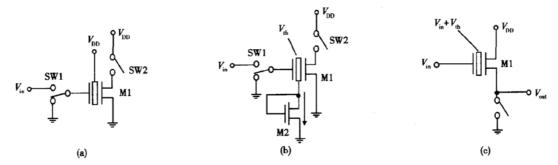

Figure 2 explains how the circuit works to finish the voltage follow function. The circuit operation consists of three phases: (1) reset phase (2) floating-gate pre-charge phase (3) source follow phase. During the reset phase, the floating gate of

the neuMOS M1 is connected to VDD with SW3 turned on. At the same time, the input gate and the source node of M1 are connected to ground with SW2 off and /SW2 on. The floating gate potential is set to V DD as shown in Fig. 2(a). Then, during the floating-gate pre-charge phase, the switch SW3 is turned off and SW4 is turned on. First, the transistor M2 operates in saturation region. The floating gate discharge through M2 until the floating gate voltage is equal to the threshold value of the transistor M2 when the transistor M2 is being turned off. So under the stable state of this phase, the floating gate potential of M2 & will be set at the threshold value of M2 Vth. Finally, during source follow phase, the switche SW2 is turned on, /SW2 is off and SW1 is turned to the input signal V<sub>in</sub>. The source follower is activated. If the capacitor of the parasitical capacitor between the floating gate and the substrate of neuMOS is ignored, the floating gate voltage of M 2 \$\phi\$ will be \$V\_{in}\$ +  $V_{th}$ , as a result, the output voltage  $V_{out}$  will be

.

$$V_{\text{out}} = \Phi_{\text{f}} - V_{\text{th}} \approx V_{\text{in}} + V_{\text{th}} - V_{\text{th}} = V_{\text{in}}$$

(1)

Fig. 2 Three phases of threshold circuit (a) Reset phase; (b) Floating gate precharge phase; (c) Source follow phase

That is to say, at the source follow phase, the output of source following circuit can follow the input very well even if the input is lower than the threshold of the transistor.

## 3 Circuit performance analysis

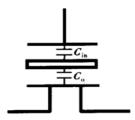

In order to evaluate the basic performance of the cell, the circuit is simulated with HSPICE. In this cell, the value of input capacitor of M 1  $C_{in}$  as shown in Fig. 3 is important to the performance of this circuit. On one hand, in order to speed up the discharge of the floating gate during the pre-charge phase, the value of  $C_{in}$  should be set smaller. On the other hand, if the value of  $C_{in}$  is too small, the parasitical capacitor of MOS transistor  $C_{0}$  as shown in Fig. 3 will affect the coupled voltage of the floating gate during the source follow phase. It is assumed that during the source follow phase, no charge injection occurs. So the charge of floating gate in the

Fig. 3 Parasitical capacitor model of neuMOS

pre-charge phase should be equal to that during the source follow phase. In the pre-charge phase, the charge of the floating gate is calculated as

$$Q_{\rm FI} = C_{\rm in}V_{\rm th} + C_0V_{\rm th} \tag{2}$$

In the source follow phase, the charge is

$$Q_{\rm F2} = C_{\rm in}(\Phi_{\rm F} - V_{\rm in}) + C_0\Phi_{\rm F} \tag{3}$$

Let  $Q_{F1}$  be equal to  $Q_{F2}$ , then the floating gate potential of the neuMOS should be

$$\Phi_{\rm F} = \frac{C_{\rm in} V_{\rm in}}{C_{\rm in} + C_0} + V_{\rm th} = YV_{\rm in} + V_{\rm th}$$

(4)

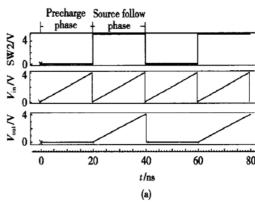

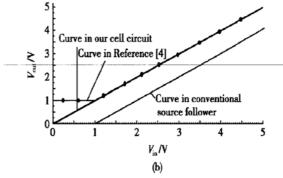

Generally, the efficient factor Y should be higher than 0.9. So it should be a trade-off between the speed and the floating gate couple efficiency. In addition, in order to improve the speed of the performance of the circuit, the W/L ratio of the transistor M2 can be set larger than normal. Figure 4 shows the HSPICE simulation result of the circuit. The operation frequency is set at 50MHz. The model parameters of the transistors are shown in Table 1. At first, the input and output signal as well as the control signal of SW2 are shown in Fig. 4(a). From the figure we can see that after operating at the floating gate pre-charge stage, the circuit enters the source follow phase—— the effective state when the switch SW2 is on. During the effective state, the source follower is activated and the output signal follows the input signal. Figure 4(b) shows the simulation curve of the Vout-Vin relationship in the source follow phase. At the same time, we give the curve of the conventional source follower and the neuMOS source follower with threshold canceling circuit in Ref. [4]. From that, we can see that in conventional source follower, there is always a threshold loss between the output and the input voltage, so when the input is lower

than the threshold of the source follower, the output will keep zero. In Ref. [4], a threshold voltage is compensated to the output, so the output voltage will follow the input voltage when the input signal is larger than the threshold of the source follower. But if the input voltage is lower than the threshold, the output keeps a constant voltage  $V_{\rm th}$ , thus voltage error still exists. In our circuit cell, the output voltage can follow the input with no threshold loss even if the input voltage is lower than the threshold of the source follower.

Fig. 4 Simulation result by HSPICE

Table 1 Model parameters of the trnsistors

| M 1                                           | $V_{\text{th}} = 1 \text{V}$ $C_{\text{in}} = 0.518 \text{pf}$ $W/L = 1.0 \mu \text{m}/0.5 \mu \text{m}$ |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|

| M 2                                           | $V_{\text{th}} = 1V  W/L = 10 \mu \text{m}/0.5 \mu \text{m}$                                             |

| Other switch<br>tansistor                     | $ V_{th}  = 1V  W/L = 1.0 \mu m/0.5 \mu m$                                                               |

| $T_{\text{ox}}(\text{gate}) = 10_{\text{nr}}$ | $T_{\text{ox}}(\text{poly}) = 30 \text{nm}$                                                              |

Generally, the source follower is used in the circuit system when analog signal calculation is needed such as neural network, matched filter and so on. The conventional source follower can be

used if the precision requirement is not high. A traditional way to settle the calculation precision of the analog signal is to apply amplifiers to the circuit, which will increase the circuit elements and area. Reference [4] presents a method to cancel the threshold error when the input signal is beyond the threshold through increasing two switches, a N channel MOS and a capacitor. But, when the input signal is lower than the threshold, there would be still voltage errors to be settled. While in our cell, the voltage error can be eliminated in the full range of the input voltage through by only increasing two switches and a N channel MOS. So our cell can implement higher operation precision with fewer elements than other neuMOS source follower can.

### 4 Experiment results

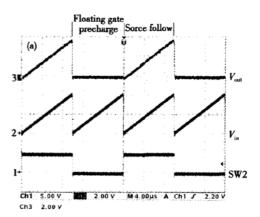

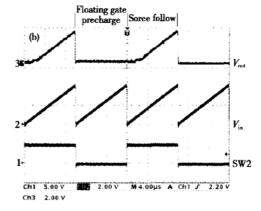

We fabricate the test circuit and get the test results as shown in Fig. 5(a). From bottom to top, the curves are the control signal of switch SW2, input voltage V<sub>in</sub> and the output voltage V<sub>out</sub>. From the test results, we can see that during the source follow phase (when the control signal of SW2 is high) the output voltage can follow the input voltage very well even if the input signal is lower than the threshold of the source follower. In order to compare the result of our cell to the conventional neuMOS source follower, we also give the test results of the conventional neuMOS source follower. Figure 5(b) is the test results of the conventional circuit without the threshold circuit (we test that with the switches SW3 and SW4 always off), compared with the test results of Fig. 5(a), this circuit have a threshold loss between the  $V_{\text{out}}$  and  $V_{\text{in}}$ .

### 5 Conclusion

A novel source follower circuit with high precise is presented and the operation principle of the circuit operation is analyzed in details. The comparison between other source followers and this circuit is carried out. The simulation result shows that our

Fig. 5 Measured result of the circuit (a) Cell with threshold circuit; (b) Cell without threshold circuit

cell has higher precision and fewer elements than other circuits. Finally, a test circuit is fabricated and the test result proves that the output voltage of this circuit can follow the input voltage very well even if the input voltage is lower than the threshold of the source follower.

#### References

- [1] Shibate T, Ohmi T. A functional MOS transistor featuring gate-level weighted sum and threshold operations. IEEE Trans Electron Devices, 1992, 39(6): 1444

- [2] Ishii H, Shibata T, Kosaka H, et al. Hard ware-learning neural network LSI using a highly functional transistor simulating neuron actions. Proc International Joint Conference on Neural Networks, 1993: 907

- [ 3 ] Yang Yuan, Yu Ningmei, Gao Yong. A novel matched filter structure with neuron MOS devices. Chinese Journal of Semiconductors, 2004, 25(1):1

- [4] Konda M, Shibata T, Ohmi T. Neuron-MOS correlator based

on manhattan distance computation for event recognition hardware. IEEE International Symposium on Circuit and Sys-

tem (ISCAS96), 1996, 4: 217

## 一种新型的高精度神经元 MOS 源极跟随单元电路\*

杨 媛 高 勇 余宁梅 刘梦新

(西安理工大学电子工程系, 西安 710048)

摘要:提出了一种新型的神经元 MOS 源极跟随电路结构,该电路即使在输入信号小于阈值电压的情况下也能够完成源极跟随的功能,因而具有较高的精度.仿真和实验结果表明它比传统的神经元 MOS 源极跟随电路具有更高的精度.

关键词: 神经元 MOS; 源极跟随电路; 阈值

**EEACC**: 2570D

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2004)09-1074-05

<sup>\*</sup> 国家自然科学基金资助项目(批准号:60276017)

杨 媛 女,1974年出生,博士研究生,主要研究方向为集成电路新型器件及其应用.

高 勇 男, 1956 年出生, 教授, 目前主要从事新型功率半导体器件及集成电路 CAD 和半导体光电集成的研究.

余宁梅 女,1963年出生,教授,研究领域为集成电路设计及工艺技术.