2004年11月

# Polarization-Insensitive Silica on Silicon Arrayed Waveguide Grating Design\*

An Junming<sup>1, 2</sup>, Li Jian<sup>1</sup>, Gao Dingshan<sup>1</sup>, Xia Junlei<sup>1</sup>, Li Jianguang<sup>1</sup>, Wang Hongjie<sup>1</sup> and Hu Xiongwei<sup>1</sup>

(1 R&D Center for Optoelectonics, Institute of Semiconductors, The Chinese Academy of Sciences, Beijing 100083, China) (2 Department of Physics, Inner Mongolia University, Hohhot 010021, China)

Abstract: A new technology for fabrication of silica on silicon arrayed waveguide grating (AWG) based on deep etching and thermal oxidation is presented. Using this method, a silicon layer is remained at the side of waveguide. The stress distribution and effective refractive index of waveguide fabricated by this approach are calculated using finite element and finite difference beam propagation method, respectively. The results of these studies indicate that the stress of silica on silicon optical waveguide can be matched in parallel and vertical direction and AWG polarization dependent wavelength (PDA) can be reduced effectively due to side-silicon layer.

**Key words**: silica on silicon; arrayed waveguide grating; stress; birefringence; polarization dependent wavelength; numerical analysis

EEACC: 4130; 6150C; 7320P

CLC number: TN814<sup>+</sup>.6 Document code: A

Article ID: 0253-4177(2004) 11-1360-04

# 1 Introduction

With the rapid increase of channel counts in dense wavelength division multiplexing (DWDM) systems, integrated arrayed waveguide grating (AWG) devices, especially low loss and high coupling efficiency silica on silicon AWGs, are attractive and essential components for various applications requiring wavelength multiplexing/demultiplexing functions. But a problem remains with its PD $\lambda$ . It is thought to result from the use of silicon substrate, which upon cooling after the sintering or annealing of the glass layer strains the glass layer because of its different expansion coefficient. This PD $\lambda$  must be reduced substantially before silica on silicon AWG is practically introduced. Several approaches have been reported for eliminating the

PDλ<sup>[1-4]</sup>. This paper describes a new method for fabricating low PDλ silica-based AWG. Stresses of silica waveguide with a side-silicon layer are examined using finite element method (FEM). At the same time, the effective refractive index are calculated using finite different beam propagation method(FD-BPM). After optimizing the width and depth of side-silicon layer, a polarization insensitive AWG is designed, and output spectra is simulated using single transmission function.

### 2 Methods for fabrication

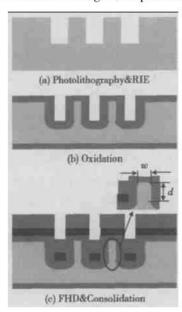

The process flow of fabrication for a buried silica on silicon AWG under study is shown in Fig. 1. The first step is to etch silicon wafer directly using reactive ion etching (RIE) to form AWG layout, where space of waveguide 22. 8µm in order

<sup>\*</sup> Project supported by State Key Development Program for Basic Research of China (No. G2000036602), National Hi-Tech Research and Development Program of China (No. 2002A A 312260), and National Natural Science Foundation of China (No. 69889701)

An Junming male, was born in 1969, PhD candidate. His research interest lies in silica AWG design and fabrication.

to get sidecladding with 15µm thickness using thermal oxidation and leave core with 6μm width, the gap between two waveguides and the depth are not less than  $36\mu m$  and  $30\mu m$ , respectively, furthermore, these values should be optimized. Following that the silicon wafer is oxidized for thirty days under the hydrosphere at mosphere at 1050°C. The obtained SiO<sub>2</sub> layer thickness is about 15µm, which is used as undercladding and sidecladding, and a silicon layer is left at the side of waveguide, here we name it as side-silicon layer. The third step is to deposit two successive glass particle layers using flame hydrolysis deposition (FHD) or PECVD which form the core with 6µm thickness and overcladding with 15µm thickness. Finally, the substrate with these two porous glass layers is heated to about 1000°C for consolidation or annealing. Using this new method, side-silicon layer with higher thermal expansive coefficient can be remained between two waveguides, which the width and depth are marked w and d in Fig. 1, respectively.

Fig. 1 Fabrication process of silica on silicon AWG

## 3 Calculation results and discussion

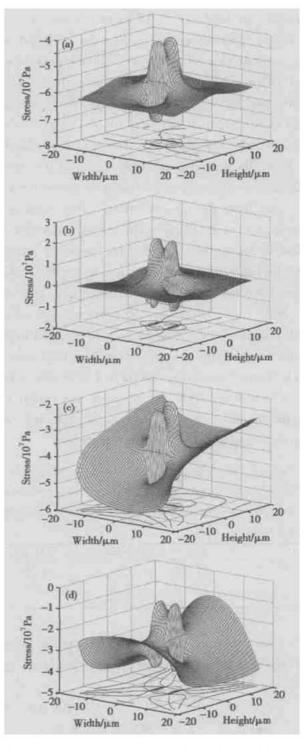

Figure 2 shows calculated stress distribution of one waveguide of AWG in parallel and perpendicular to the wafer surface using FEM<sup>[5]</sup>. The

Fig. 2 Stress distribution in parallel and perpendicular to the wafer surface (a) Parallel to the wafer surface with w=0; (b) Perpendicular to the wafer surface with w=0; (c) Parallel to the wafer surface with  $w=10\mu\text{m}$ ,  $d=36\mu\text{m}$ ; (d) Perpendicular to the wafer surface with  $w=10\mu\text{m}$ ,  $d=36\mu\text{m}$

thermal expansion coefficient, Poisson's ratio, and Young's modulus used in FEM are specified for all elements in Table 1<sup>[6,7]</sup>. All materials are assumed to be mechanically isotropic. Figures 2(a) and (b) are without side-silicon layer, while Figures 2(c) and (d) are with side-silicon layer with the width  $10\mu m$  and depth  $36\mu m$ , respectively. When without side-silicon layer, in parallel to the wafer surface one finds the expected compressive stress is resulted from the higher thermal expansion of the silicon substrate, while in perpendicular to the wafer surface one finds the core is suffered from expansive stress and the cladding is almost not so, which results in higher stress difference between parallel and perpendicular to the wafer. But compared to Figs. 2(a) and (b), Figures 2(c) and (d) show that not only in parallel, but also perpendicular to the wafer surface, the waveguide is also suffered significant compressive stress due to the existence of high thermal expansive coefficient side-silicon layer, which means that the stresses in parallel and perpendicular to the wafer can be matched each other, resulting in very low birefringence.

Table 1 Mechanical data used in the strain calculations: Young's modulus (E), Poisson's ratio  $(\nu)$ , and thermal expansion coefficient  $(\alpha)$  for Si, SiO<sub>2</sub> cladding and core

|                         | Si    | SiO <sub>2</sub> cladding | SiO <sub>2</sub> core |

|-------------------------|-------|---------------------------|-----------------------|

| $E/10^9$ Pa             | 131   | 65                        | 70                    |

| ν                       | 0. 28 | 0. 17                     | 0. 2                  |

| $\alpha/10^{-6} K^{-1}$ | 3.6   | 0. 5                      | 1.2                   |

Based on above calculated stress distribution, the changes in refractive index for triaxial stresses are

$$\Delta n_x = n_x - n = -B_2 \sigma_x - B_1 (\sigma_y + \sigma_z) \quad (1)$$

$$\Delta n_{y} = n_{y} - n = -B_{2}\sigma_{y} - B_{1}(\sigma_{x} + \sigma_{z}) \quad (2)$$

where the stress optical coefficients are  $B_1 = 4.2 \times 10^{-12} \text{Pa}$  and  $B_2 = 6.5 \times 10^{-13} \text{Pa}^{[8]}$ . Refractive index n = 1.444, refractive index difference between core and cladding is 0.75%. The propagation constant is calculated based on the refractive index output from stress analysis by full-vector alternating direction implicit (ADI) iterative method<sup>[9]</sup>. Then birefringence index B is deduced:  $B = (\beta_{\text{TM}})$

$-\beta_{\text{TE}})/k_0$ .

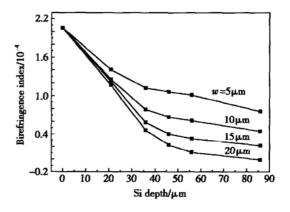

Birefringence index for different w and d of side-silicon layer is shown in Fig. 3. The results indicate that the waveguide birefringence depends on w and d. For given w, the birefringence index decreases sharper at  $d < 36 \mu \text{m}$  than at  $d > 36 \mu \text{m}$ . For given d, more width side-silicon layer helps to reduce the birefringence. The result means that by optimizing w and d, birefringence index can be lowered to  $1.0 \times 10^{-4}$ .

Fig. 3 Calculated birefringence as a function of w and d

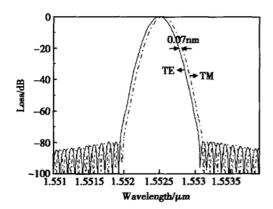

Based on above analysis, low PD $\lambda$  silica AWG is designed [10]. Considered the size of AWG device and difficulty in deep etching, w and d are specified as  $10\mu$ m and  $36\mu$ m, respectively, so the gap between two waveguides is  $46\mu$ m. The correspondent parameters for 16 channels AWG are given in Table 2. The total area is  $6\text{cm} \times 4.5\text{cm}$ , the output spectra simulated using single transmission function near center wavelength 1.  $5525\mu$ m for TE and TM mode is shown in Fig. 4. The result indicates that PD $\lambda$  is about 0. 07nm, which meets the demand of low PD $\lambda$  AWG.

Table 2 Parameters for designed 16 channels AWG

| $n_{\mathrm{s}}$ | $n_{\mathrm{c}}$               | $n_{\mathrm{g}}$ | m   | R/µm       | $\Delta L/\mu{ m m}$ | Na  |

|------------------|--------------------------------|------------------|-----|------------|----------------------|-----|

| 1. 452397        | 1. 450156(TE)<br>1. 450235(TM) | 1. 456263        | 120 | 24105. 104 | 128. 469             | 100 |

$n_s$ ,  $n_c$ ,  $n_g$ , m, R,  $\Delta L$ , and Na are effective refractive index of slab waveguide, effective refractive index of channel waveguide, group index for  $n_c$ , diffraction order, focal length of slab waveguide, length difference of adjacent arrayed waveguide, and number of arrayed waveguides, respectively.

Fig. 4 Output spectra at λ0 for designed AWG

### 4 Conclusion

We have presented a novel technology for fabricating buried silica AWG based on deep etching and thermal oxidation, which a silicon layer between waveguides is remained. Numerical analysis indicates that stresses of this kind of waveguide in parallel and perpendicular to wafer direction can be matched and low birefringence can be obtained by optimizing width and depth of side-silicon layer. Using this process, PDλ of designed AWG with 16 channels is only 0.07nm.

#### References

[1] Inoue Y, Takahashi H, Ando S, et al. Elimination of polariza-

- tion sensitivity in silica-based wavelength division multiplexer using a polyimide half waveplate. J Lightwave Technol, 1997, 15(10): 1974

- [2] Suzuki S, Sumida S, Inoue Y, et al. Polarisation insensitive arrayed-waveguide gratings using dopant rich silica-based glass with ghermal expansion adjusted to Si substrate. Electron Lett, 1997, 33(13): 1173

- [3] Takahashi H, Hibino Y, Ohmorin Y, et al. Polarisation-insensitive arrayed-waveguide wavelength multiplexer with birefringence compensation film. IEEE Photonics Technol Lett, 1993, 5(6): 707

- [4] Wildermuth E, Nadler C, Lanker M, et al. Penalty-free polarisation compensation of SiO<sub>2</sub>/Si arrayed waveguide grating wavelength multiplexers using stress release grooves. Electron Lett, 1998, 34(20): 1661

- [5] Ssitoh K, Koshiba M, Tsuji Y. Stress analysis method for elastically anisotropic material based optical waveguides and its application to strain-induced optical waveguides. J Lightwave Technol, 1999, 17(2): 255

- [6] Maissel L. Thermal expansion of silicon. J Appl Phys, 1960, 31(1):22

- [7] Wortman J J, Evans R A. Young's modulus, shear modulus and Poisson's ratio in silicon and germanium. J Appl Phys, 1965, 36(1):153

- [8] Scherer G W. Stress-induced index profile distortion in optical waveguides. Appl Opt, 1980, 19(12): 2000

- [9] Hadley G R, Smith R E. Full-vector waveguide modeling using an iterative finite-difference method with transparent boundary conditions. J Lightwave Technol, 1995, 13(3): 465

- [10] Smit M K, Cor V D. PHASAR -based WDM -divices: principles, design and applications. IEEE Sel Topics Quantum Electron, 1996, 2(2): 236

# 偏振不灵敏硅基二氧化硅阵列波导光栅设计

安俊明1.2 李 健1 郜定山1 夏君磊1 李建光1 王红杰1 胡雄伟1

(1中国科学院半导体研究所光电子研究发展中心,北京 100083) (2内蒙古大学物理系,呼和浩特 010021)

摘要: 以深刻蚀和热氧化工艺为基础, 提出了一种新的阵列波导光栅(AWG) 制备技术. 这一工艺可使 AWG 中的波导侧向留有一硅层. 采用有限元法和有限差分束传播法分别计算了存在这一硅层时的波导应力分布和有效折射率. 结果表明由于这一侧向硅层的存在, 使 AWG 中波导在水平和垂直方向的应力趋于一致, AWG 的偏振相关波长明显减小.

关键词: 硅基二氧化硅; 阵列波导光栅; 应力; 双折射; 偏振相关波长; 数值分析

EEACC: 4130; 6150C; 7320P

中图分类号: TN 814\*.6 文献标识码: A 文章编号: 0253-4177(2004)11-1360-04

<sup>\*</sup> 国家重点基础研究发展规划(批准号: G2000036602), 国家高技术研究发展计划(批准号: 2002AA312260) 和国家自然科学基金(批准号: 69889701) 资助项目

安俊明 男, 1969年出生, 博士研究生, 从事硅基二氧化硅阵列波导光栅的设计和制备.