# Optimization and Synthesis of RF CMOS Polyphase Filters with Layout Considerations

Zhang Zisan, Ma Xiangpeng, Kolnsberg Stephan and Kokozinski Rainer

(Wireless Chips & Systems Division, Fraunhof er-Institute of Microelectronics Circuits & Systems, Finkenstr. 61, Duisburg 47057, Germany)

**Abstract**: A novel software tool for optimization and synthesis of RF CMOS polyhase filters(PPFs), PPFOPTIMA, is developed. In the optimization engine, genetic algorithm is adopted to avoid local optima. Experiments on PPFOPTIMA demonstrate that it is an efficient design aid for design and optimization of RF CMOS PPFs.

Key words: RF CMOS; polyphase filters; quadrature signal generation; genetic algorithms; analog CAD

EEACC: 2520M; 2560J; 1350J

CLC number: T N 405 Document code: A Article ID: 0253-4177(2004) 12-1612-06

#### 1 Introduction

Quadrature signal generation is an important function block in modern wireless transceivers in which quadrature modulation and demodulation are widely applied. However, some quadrature signal generation techniques are not well suited for CMOS implementation because complicated tuning circuits are needed to overcome CMOS process tolerances. Polyphase filters (PPFs), originally developed for single-side band modulation in audio frequency [1], have been rediscovered as an efficient solution for high accuracy quadrature generation in radio frequency CMOS designs [2] because of its simple stagger-tuning mechanism and robustness to CMOS process tolerance.

Previous works were concentrated on analysis<sup>[3]</sup> and design of RF CMOS PPFs. Some design guidelines were presented by Behbahani<sup>[4]</sup>. However, they give too much freedom for the design, and it needs intensive trials and several design cycles to reach a good design. With layout considerations, optimization of RF CMOS PPFs can not be solved

by using analytical mathematics, because of multiple design objectives and constraints. PPFOPTI-MA, a novel software tool for optimization and synthesis of RF CMOS PPFs, has been developed. In the optimization engine, genetic algorithm (GA) is adopted to avoid local optima. Experiments on PPFOPTIMA demonstrate that it is an efficient design aid for design and optimization of RF CMOS PPFs.

## 2 Considerations in schematic design

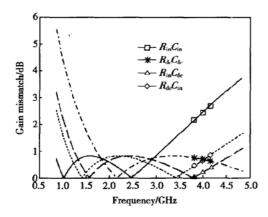

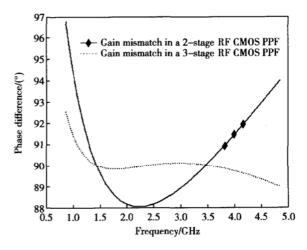

As is well known, CMOS process has severe process tolerances. In the design of RF CMOS PPFs, process tolerances can be overcome by using the concept of "folerance design". Specifically, by enlarging the bandwidth of the polyphase filters, the worst-case bandwidth of the polyphase filters can be guaranteed to be located in the operating band, which is the principle of stagger-tuning technique. In Fig. 1, gain mismatches (gain difference between I path and Q path) influenced by process tolerances in an RF CMOS PPF designed for a

bluetooth receiver are shown, from which we can see that, no matter how  $R_s$  and  $C_s$  vary (within process tolerance), the operating frequency band of bluetooth signal (2.4~ 2.48GHz) is always covered.

Fig. 1 Gain mismatch influenced by process tolerances in an RF CMOS PPF

#### 3 Considerations in physical layout

In physical layout, component mismatch and parasitic effects have significant influences on the performance of RF CMOS PPFs. Even though there are some layout techniques such as inter-digitized structure, common centroid structure to minimize component mismatch, it can not be totally eliminated. The most important specification for an RF CMOS PPF is image reject ratio (IRR), which is related to the sensitivity of a receiver. From Monte Carlo simulations [4] it has been found that:

$$IRR_{U} > - 20lg \sigma_{component}$$

(1)

where IRRu is the ultimately obtainable image reject ratio, and  $\sigma_{\text{component}}$  is the component mismatch. It is known from the experimental study<sup>[5]</sup> that the variance of adjacent on-chip resistors and capacitors is proportional to the inverse of their area, that is, neighboring components with larger area can be better matched. By using the latest resistor and capacitor mismatch models<sup>[5]</sup> as shown in Eqs. (2) and (3), the minimum area required by a given specification can be calculated.

$$\sigma_{\Delta R/R}^{2} = \sigma_{R_{\rm sh}}^{2} \times \left[ \frac{L}{LR_{\rm sh} + R_{\rm e}} \right]^{2} + \sigma_{R_{\rm e}}^{2} \times \left[ \frac{L}{LR_{\rm sh} + R_{\rm e}} \right]^{2} + \sigma_{\Delta W}^{2} \times \left[ \frac{L}{W + \Delta W} \right]^{2}$$

(2)

where  $\sigma_{R_{\rm sh}} = \frac{A_{R_{\rm sh}}}{(WL)^{1/2}}$ ,  $\sigma_{R_{\rm e}} = A_{R_{\rm e}}$ ,  $\sigma_{\Delta W} = \frac{A_{\Delta W}}{W^{1/-\sqrt{2}}}$ ,  $\sigma$  is the standard deviation, W and L are resistor width and length,  $R_{\rm sh}$  is the sheet resistance of the polysilicon resistor,  $R_{\rm e}$  is the end resistance coefficient,  $\Delta W$  is the resistor width offset.

$$\sigma_{\Delta C/C}^2 = \sigma_{\rm p}^2 + \sigma_{\rm a}^2 + \sigma_{\rm d}^2 \tag{3}$$

where  $\sigma_{\rm p}=\frac{f_{\rm p}}{C^{3/4}}, \sigma_{\rm a}=\frac{f_{\rm a}}{C^{1/2}}, \ {\rm and} \ \sigma_{\rm d}=f_{\rm d}d, f_{\rm p}, f_{\rm a}, f_{\rm d}$  are constants describing the influences of periphery, area and distance fluctuations.

Optimized for digital circuits, CMOS process has severe parasitic effects which are quite challenges for analog design. In the design of RF CMOS polyphase filters, there are two effects from parasitics:

- Signal loss caused by the lossy substrate in addition to the theoretical - 3dB/stage in passive filters;

- (2) Noise coupling caused by parasitic capacitance.

For a given CMOS process, there are two ways to minimize these effects. One is to minimize the chip area, the other is to use shieldings, namely N-wells and guard rings to protect noise sensitive analog circuits.

With considerations of parasitics, the maximum length of the resistor (MLR) allowed in a certain CMOS process can be derived as follows:

$$f_{\rm R} = \frac{1}{2\pi R C_{\rm p}} = \frac{1}{2\pi \times \frac{L}{W} \times LW \rho C_{\rm p}} = \frac{1}{2\pi L^2 \rho C_{\rm p}}$$

(4)

$$f_{\rm op} \leqslant f_{\rm R} = \frac{1}{2\pi L^2 \rho C_{\rm p}} \tag{5}$$

$$L \leqslant \frac{1}{\sqrt{2\pi f_{\text{op}}\rho C_{\text{p}}}} \tag{6}$$

where  $\rho$  is sheet resistance, L is the length of the resistor, and  $C_P$  is parasitic capacitance per unit area to the substrate. Before physical layout, the

MLR should be calculated.

## 4 Optimization problem formulation

In the design of RF CMOS PPFs, the design objectives are to:

- (1) Satisfy the specifications required by corresponding wireless communication standard and transceiver architecture;

- (2) Minimize chip area (thus parasitic capacitance between RF CMOS PPFs and the substrate can be minimized);

- (3) Maximize immunity to noise coupling;

- (4) Minimize additional signal loss.

Based on the design objectives, we can categorize previous design consideration as objective functions A and constraints B.

(A) Objective functions are IRR and chip area (Please note that an accurate IRR equation is used here).

IRR = -

$$20 \lg \left[ \frac{\Delta A^2}{16(A_1 + A_0)^2} + \frac{\Delta \mathcal{B}}{4} \right]$$

(7)

where  $\Delta A = |A_1 - A_0|$ ,  $\Delta \Phi = |\Phi - \Phi_0|$ ,  $A_1$ ,  $A_0$ ,  $\Phi$ ,  $\Phi_0$  are amplitudes and phases of I paths and Q paths respectively. They can be calculated by using transfer functions of PPFs<sup>[4]</sup>.

Chip area (including dummies):

$$S = \sum_{i=1}^{n} (6S_{R_i} + 16S_{C_i})$$

(8)

where  $S_{R_i} = L_{R_i} \times W_{R_i}$ ,  $S_{C_i} = \frac{C}{C_{\text{unit}}}$ ,  $i = 1, 2, \dots, n$ ,  $L_{R_i}$ ,  $W_{R_i}$  are the length and width of resistors in the *i*th stage respectively,  $C_{\text{unit}}$  is the unit capacitance of the capacitors.

(B) Design constraints: Even though chip area is to be minimized, for a given specification of IRR, there are minimum areas of resistors and capacitors to avoid intolerable component mismatch, they can be calculated by using Eqs. (9) and (10).

$$\sigma_{\Delta R/R} \geqslant 10^{-1RR/20}$$

(9)

$$\sigma_{\Delta C/C} \geqslant 10^{-1RR/20} \tag{10}$$

Another constraint in practice is that the length of resistors should be less than the maximum resistor length calculated by Eq. (6).

The optimization problem formulated above has multiple objectives, and furthermore the main objective function, IRR, was found to have multiple peaks. Traditional optimizations methodologies like calculus-based optimization, gradient descend are no longer suitable for this application, because they are subject to local optima. Under this situation, genetic algorithm has advantages over any other conventional optimization techniques for its capability in escaping from local optima, thus it is adopted in the optimization engine of PPFOPTI-MA.

#### 5 System implementation

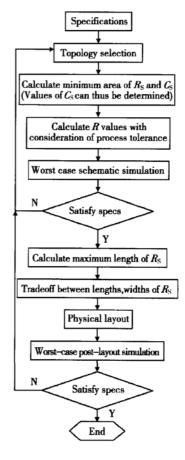

Based on aforementioned design considerations in schematic and layout, a design flow for synthesis of RF CMOS PPFs has been proposed as shown in Fig. 2.

Fig. 2 A design flow for synthesis of RF CMOS PPFs

Different from other traditional optimization methods, the first step in using GA is to construct a fitness function, which is the criterion for selecting suitable population in the next generation. In PPFOPTIMA, the fitness function is a sum of IRR, chip area (S), and component mismatch property of resistors and capacitors with different weights as shown in Eq. (11).

$F = w_1S + w_2(CM_R + CM_C) + w_3IRR$  (11) where  $w_1$ ,  $w_2$ , and  $w_3$  are the weights for chip area, component mismatch of resistors and capacitors, and IRR, respectively. In PPFOPTIM A, as S,  $CM_R$ ,  $CM_C$  are in the order of  $10^{-3}$ ,  $w_1$  and  $w_2$  values are given in the order of  $10^4$  to differentiate good population from poor ones.

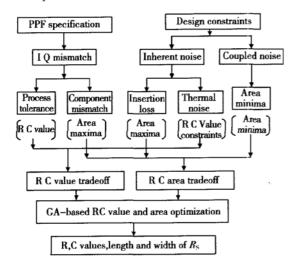

The framework of PPFOPTIMA is shown in Fig. 3, from which we can see that considerations in both schematic design and physical layout are incorporated into this software tool. Inputs needed from the user are the operating frequency and process related information, thus it is very convenient and efficient for novice designers under time-to-market pressures.

Fig. 3 Framework of PPFOPTIMA

## 6 Experiments on PPFOPTIMA

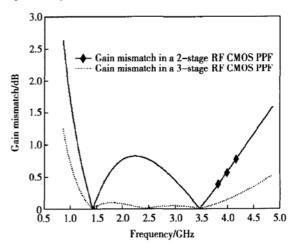

In order to design an RF CMOS PPF for a low-IF CMOS single-chip bluetooth receiver in Fraunhofer-IMS CMOS technology, a 2-stage and a

3-stage RF CMOS PPFs were synthesized by using PPFOPTIMA, and the synthesis results were compared and analyzed. The specifications derived from the bluetooth standard and the low-IF receiver architecture are following: gain mismatch (GM)  $\leq$  0.6dB, phase mismatch (PM)  $\leq$  5°. GM and phase difference (PD, please note that PM = PD-90°) in RF CMOS PPFs synthesized are shown in Figs. 4 and 5 by using their transfer functions. From these figures, we can see that 3-stage RF CMOS PPFs has better quadrature accuracy (less GM and PM) than that 2-stage PPF has. Final design parameters and simulation results are shown in Tables 1 and 2 respectively (W stands for the widths of resistors

Fig. 4 Transfer function of multiple stages RF CMOS PPFs showing gain mismatch

Fig. 5 Transfer function of multiple stages RF CMOS PPFs showing phase difference

in these tables). From Tables 1 and 2, we can see that, 3-stage PPF has better quadrature accuracy, but it has larger chip area and more insertion loss (IL) than that 2-stage PPF has. As both of them

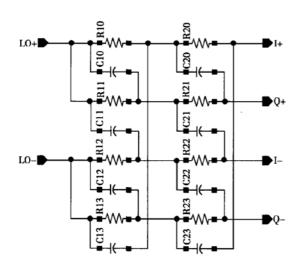

satisfy targeting specifications, 2-stage RF PPF was chosen by PPFOPTIMA. The schematic of the 2-stage RF CMOS PPF is shown in Fig. 6.

| Table 1 | Synthesis | results of a | 3-stage RF | CMOS PPF | by | PPFOPT IM A |

|---------|-----------|--------------|------------|----------|----|-------------|

|         |           |              |            |          |    |             |

| Component value |                |        | Simulation result |              |       |              | Chip area∕µm² |          |

|-----------------|----------------|--------|-------------------|--------------|-------|--------------|---------------|----------|

|                 | Resistor/Ω     |        |                   | Capacitor/fF | GM/dB | PM/(°) IL/dB |               |          |

| $R_1$           | R <sub>2</sub> | $R_3$  | $W/\mu\mathrm{m}$ | 229. 4       | 0. 07 | 0. 26        | - 9.2         | 53912. 8 |

| 271. 6          | 283.6          | 347. 6 | 3                 |              |       |              |               |          |

Table 2 Synthesis results of a 2-stage RF CMOS PPF by PPFOPTIMA

| Component value |                |                    |              | Simulation result |       |        | Chip area/µm² |         |  |

|-----------------|----------------|--------------------|--------------|-------------------|-------|--------|---------------|---------|--|

| Resis           | Resistor/Ω     |                    | Capacitor/fF |                   | GM/dB | PM/(°) | IL/dB         |         |  |

| $R_1$           | R <sub>2</sub> | $W/\mu \mathrm{m}$ | $C_1$        | C2                | 0. 18 | 0.45   | - 6. 1        | 37525.6 |  |

| 223.5           | 256. 6         | 3                  | 238.9        | 312. 9            |       |        |               |         |  |

Fig. 6 Schematic of a 2-stage RF CMOS polyphase filter

#### 7 Conclusion

In this paper, based on the design heuristics in schematic design and physical layout, PPFOPTI-MA, an optimization and synthesis tool for RF CMOS polyphase filters, has been developed. Gentic algorithm was adopted in the optimization engine to avoid local optima. Experiments on PPFOPTIMA demonstrate that this software tool is efficient in design aid and optimization of RF CMOS PPFs.

#### References

- [1] Gingell M J. Single sideband modulation using sequence asymmetric polyphase networks'. Electrical Communication Magazine, 1973, 48(1/2): 21

- [2] Crols J, Steyaert M. An analog integrated polyphase filter for a high performance low-IF receiver. IEEE Symposium on VL-SI Circuits, 1995: 87

- [3] Galal S H, Ragaie H F, Tawfik M S. RC sequence asymmetric polyphase networks for RF integrated transceivers. IEEE Trans Circuits Syst II, 2000, 47(1):18

- [4] Behbahani F, Kishigami Y, Leete J, et al. CMOS mixers and polyphase filters for large image rejection VCO. IEEE J Solid-State Circuits, 2001, 36(6): 873

- [5] Ytterdal T, Cheng Y, Fjeldly T A. Device modeling for analog and RF CMOS circuit design. John Wiley & Sons Inc, 2003

## 考虑布局因素的射频 CMOS 多相位滤波器的优化与合成

张子三 马向鹏 Kolnsberg Stephan Kokozinski Rainer

(德国弗劳恩霍夫微电子电路与系统研究所 无线芯片与系统部, 杜伊斯堡市 47057, 德国)

摘要: 开发了一个新颖的考虑布局因素的用于射频 CMOS 多相位滤波器的优化和合成工具——PPFOPTIM A. 在优化引擎中使用了遗传算法用来避免局部的优化解. 实验结果证明 PPFOPTIM A 是射频 CMOS 多相位滤波器设计和优化中有效的计算机辅助设计工具.

关键词: 射频 CM OS; 多相位滤波器; 正交信号发生; 遗传算法; 模拟电路计算机辅助设计

EEACC: 2520M; 2560J; 1350J

中图分类号: TN405 文献标识码: A 文章编号: 0253-4177(2004)12-1612-06