2001年3月

# Fabrication of 4H-SiC Merged PN-Schottky Diodes

ZHANG Yu-ming<sup>1</sup>, ZHANG Yi-men<sup>1</sup>, P. Alexandrov<sup>2</sup> and J. H. Zhao<sup>2</sup>

(1 Institute of Microelectronics, Xidian University, Xi'an 710071, China)

(2 Department of Electrical and Computer Engineering, The State University of

New Jersey, NJ 08854-8058, USA)

Abstract: The design, fabrication and characteristics of 4H-SiC merged PN-Schottky (MPS) diodes with Ni Schottky contact and junction termination extension (JTE) edge termination are reported. A multiple-energy implantation Al in the surface of the  $n^-$  drift region below the face-to-face Schottky metal formed pn junctions, which screen the Schottky contact from high electrical, post implantation annealing has been done at 1500°C for 30min in the ultra-high purity Ar ambient. The devices can block more than 600V reverse voltage and the lowest leakage current at - 600V is  $1 \times 10^{-3}$  A/cm², while the forward current density at 3V is more than 200 A/cm² for  $1000\mu$ m devices, 1000 A/cm² at 3.5V for  $300\mu$ m devices.

Key words: power devices: SiC: semiconductor diode: MPS

**EEACC**: 2560H; 2550; 2520M **PACC**: 7340L **CLC number**: TN311<sup>+</sup>.7 **Document code**: A

Article ID: 0253-4177(2001)03-0265-06

### 1 Introduction

Silicon carbide(SiC) is a possible candidate to replace the silicon-based devices in the market of high power devices. The potentials of SiC power devices were clearly demonstrated several years ago<sup>[1]</sup>. The state-of-the-art high voltage power devices have been reviewed in Reference [2]. The highest reverse blocking voltage for a 4H-SiC rectifier reported is about 5000V so far. SiC MOSFETs have been demonstrated lower in the on-resistance than that of the silicon device. At room temperature, the 5000V IGBT and GTO have a lower forward drop than the power MOSFET when the current densities exceed 100A/cm<sup>2</sup>. However. at a

higher temperature, both the GTO and the IGBT are superior. Experimentally, both n- and p-channel IGBT's have been demonstrated in either 6H- or 4H-SiC up to 800V, but the forward drop is still far from the optimal one. The symmetric and asymmetric 4H-SiC gate-controlled thyristors reported have the breakdown voltage up to 1000V and current-handling capabilities up to 6A.

Both two- and three- terminal devices are needed to construct the basic power circuit units, such as a half-bridge circuit. The most common two-terminal devices are Schottky and PIN rectifiers. The main advantage of a PIN diode is its lower leakage current under the reverse biases, while its disadvantage is that its forward turn-on voltage is inherently higher than that of a Schottky

ZHANG Yu-ming Ph. D, associate professor, was born in 1965. His work includes in novel semiconductor devices, TCAD and VLSI CAD. In particular, his current research interests focus on modeling and simulation, process technologies and devices physics for SiC-based devices.

ZHANG Yi-men male, professor, Ph.D's advisor, was born in 1941. He achieves great attainments in the field of device modeling and simulation in VLSI, VLSI CAD, quantum well devices, IC and high temperature microelectronics in wide band gap semiconductor.

diode, as is especially true for a wide-bandgap semiconductor SiC. Another problem of the PIN diode is the carrier storage during the on-state, which results in a switching delay when it is driven from the forward conduction to the reverse blocking. On the other hand, a Schottky diode has the advantages of a low turn-on voltage and fast transient recovery. However, due to the Schottky barrier height, the Schottky diode can never achieve the low leakage current of the PIN diode. The well-known Schottky barrier lowering with the image force, which results in an exponential increase of reverse current with the square root of the field strength  $(J_R \sim \exp(\sqrt{E}))$ , is more crucial in SiC due to its extreme high critical electrical field strength (3MV/cm). The increased leakage through the Schottky barrier contact is fairly pronounced at high temperatures, during which the SiC devices are expected to be used.

To combine the best features of these two rectifiers, merged PN-Schottky (MPS) diode with the hybrid rectifier structure has been proposed by Wilamowski<sup>[3]</sup> for Si and demonstrated by Held *et al.* for SiC<sup>[4]</sup>. It combines the forward characteristics of the Schottky diode with the reverse property of the PN diode, and the tradeoff in it between the device reverse leakage current and the forward voltage drop can be overcome because the device reverse characteristics are determined by PN junctions of the device instead of the Schottky barrier height. Hence, it is possible to reduce the MPS forword voltage drop by using a tower-barrier contact metal, without increasing the reverse leakage currents.

The principle of MPS has been experimentally demonstrated in SiC<sup>[4,5]</sup>. However, the fabricated devices have not been optimized with respect to the tradeoff between forward conduction and reverse blocking. Geometrical shapes and junction qualities can be adjusted to fully optimize the device. Advanced termination techniques apply to those devices with the maximum blocking capabilities obtained. So, further study in this problem is de-

sired.

Some papers on SiC material characteristics<sup>[5-9]</sup> have been reported in China, while few on SiC devices<sup>[10-14]</sup> have been done. In this paper, the design, fabrication and characterization of 4H-SiC MPS diodes are reported.

## 2 Design and Fabrication

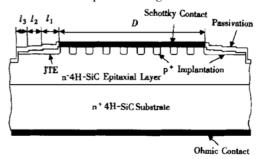

Figure 1 shows the conceptual illustration of the SiC MPS diode to be investigated in this paper. In this device, the n<sup>-</sup> 4H-SiC epitaxial layer is grown on the n<sup>+</sup> 4H-SiC substrate. On the surface of the main device area, p<sup>+</sup> implanted regions alternate with the unimplanted one with spacing of several microns. A Schottky contact is designed to cover both the implanted regions and the unim-

FIG. 1 Schematic Cross-Sectional View of SiC MPS Diode

planted ones. The substrate ohmic contact being under a positive applied bias, the depletion region will spread from the Schottky interface made by the Schottky contact and the unimplanted region. At the same time, they will also spread from p-n interfaces made by the n- epitaxial layer and the p+ implanted regions. At a certain high bias, the depletion regions from the p-n junctions touch each other, as shields the Schottky interfaces from the higher electric fields. Thus, the leakage currents through the Schottky interface are effectively suppressed. When a forward bias is applied, the Schottky interfaces turn on and start to conduct currents at a relatively low bias, which is determined by the Schottky barrier height. Only the ig-

norable low current flows through the p-n junctions because they will not turn on until a much larger bias is applied. Therefore, the carrier injection from the p<sup>+</sup> regions to the n<sup>-</sup> epitaxial layer is kept minimum, assuring the fast reverse transient recovery.

Besides the design of the MPS in the main device area, it is necessary to design the junction termination properly at the periphery of the device to make the reverse blocking voltage close to the breakdown voltage of the planar structure and to suppress the leakage currents along the periphery. In this paper, a new junction-termination-extension (JTE) structure is employed. As shown in Fig. 1, the structure is made by using the same p implantation in the MPS and the subsequent stepwise etchings. Owing to the gradual thinning of the p implantation extension, the reverse bias gradually terminates near the periphery, suppressing the appearance of the very high electric field. In addition, the outmost deeper etching proves the complete termination of the implanted surface. For these devices, a new structure with improved JTE parameters, namely three-step JTE structure, has been used.

Different types of devices were implemented in the mask set. The contact diameter of all types of diodes is either  $1000\mu m$  or  $300\mu m$ . The implantation width d is 1.  $5\mu m$ , and the spacing s varies from  $2\mu m$  to  $3\mu m$ . For JTE, the widths  $l_1$ ,  $l_2$  and  $l_3$  are 75, 75 and  $50\mu m$ , respectively.

Detailed fabrication steps:  $n^-/n^+$  4H-SiC epitaxial wafers used in the fabrication are purchased from Cree Research, Inc. The thickness and doping concentration of the epitaxial layer are  $6\mu$ m and  $2.3 \times 10^{16}$  cm<sup>-3</sup>, respectively. The thickness and resistivity of the substrate are 35.56 $\mu$ m and  $0.018-0.019\Omega$  cm, respectively. The wafers are of the production grade with low micropipe density of 21cm<sup>-2</sup>. The wafers were divided into smaller pieces, and cleaned in the following sequence: acetone with ultrasonic; oxygen plasma cleaning in the ICP chamber; HF 49% for 10min with ultra-

sonic;  $H_2SO_4 + H_2O_2(4:1)$  at 90°C for 20min.

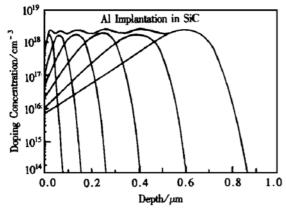

A multiple-energy implantation Al has been done at room temperature with thick photoresist mask. The implantation conditions are summarized in Table 1. The implantation profile, as simulated by ProfileCode<sup>TM</sup> (Implant Sciences Corp.), is shown in Fig. 2. The average concentration of the box profile is about  $2 \times 10^{18} \, \mathrm{cm}^{-3}$ , with a depth of 0. 65 $\mu$ m about. The p-n junction depth, which corresponds to the point where the implanted concentration equals the background doping of  $10^{16} \, \mathrm{cm}^{3}$ , is about 0.  $8\mu$ m. The actual profile, after the postimplantation annealing is expected to be as deep as 1.  $0\mu$ m.

Table 1 Aluminum Implantation Conditions

|   | Ion      | Energy/keV | Dose/cm <sup>-2</sup> |

|---|----------|------------|-----------------------|

| 1 | Aluminum | 600        | $5.2 \times 10^{13}$  |

| 2 | Aluminum | 380        | $3.2 \times 10^{13}$  |

| 3 | Aluminum | 235        | 2. $5 \times 10^{13}$ |

| 4 | Aluminum | 135        | 1. $6 \times 10^{13}$ |

| 5 | Aluminum | 70         | 9. $0 \times 10^{12}$ |

| 6 | Aluminum | 30         | 5. $0 \times 10^{12}$ |

Post implantation annealing to activate the implanted Al dopant was done in an ultra-high purity Ar ambient in a conventional furnace at 1500°C for 30min, during which, the samples were aspectant with the dummy SiC wafers to protect the sample surface. After the annealing, the samples were cleaned by the following procedures in turn: acetone with ultrasonic; oxygen plasma cleaning in the ICP chamber; HF 49% for 10min with ultrasonic; H<sub>2</sub>SO<sub>4</sub>+ H<sub>2</sub>O<sub>2</sub>(4:1) at 90°C for 20min; standard RCA cleaning procedure.

After the implantation and annealing, the edge termination was done on the samples. Firstly, the mesa termination is formed by ICP etching with a 350nm Al etching mask. The etched depth was 3.0 $\mu$ m, and the first, second and third JTE etched depth was 0.29, 0.03, and 0.03 $\mu$ m, respectively. Surface passivation was formed by the thermal oxidation of an oxidized layer of 50nm in thickness and then covered by 1.0 $\mu$ m LPCVD SiO<sub>2</sub> layer. 350nm Ni layer was deposited by sputtering

on the backside and annealed at 1050°C for 5min in the forming gas (H₂: Ar= 5%: 95%) to form an ohmic contact. Then the top-side Schottky contact was formed. Ni(100µm) and Al(300nm) were deposited by sputtering and patterned by lift-off in acetone. During that, Ni served as a Schottky contact while Al as an overlay metal.

FIG. 2 Simulation Results of Al Implantation in Device Fabrication

#### 3 Device Characterization

For the first time, the fabricated MPS diodes were visually inspected through an optical microscope. Bad devices with defects, such as defects in the original epitaxial wafer and the imperfections of photolithography were rejected, while the rest would be further tested electrically. With devices immersed in Fluorinert™ electronic liquid, the reverse leakage current and the blocking voltage were tested by using a computer controlled test setup, which consisted of a Keithley 248 high voltage source and Keithley 6517A digital electrometer. The forward characteristics were tested with an HP4145B semiconductor parameter analyzer and Tektronix 371A curve tracer when the devices are exposed to open air. All tests were performed at room temperature.

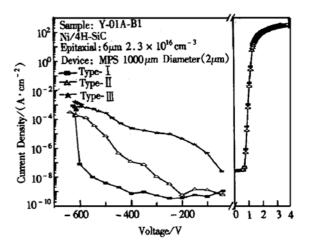

Figure 3 shows three typical I–V curves for 4H–SiC MPS diodes with diameter  $1000\mu m$  and Ni Schottky contact ring width being  $2\mu m$ . It is shown that the leakage current density at -600V

FIG. 3 *I-V* Characteristics of MPS Diode with 1000μm Diameter and Ni Contact

is less than  $10^{-3}$  A/cm<sup>2</sup>. The forward current density at 3V is more than 200 A/cm<sup>2</sup>. From the reverse characteristics, we can see that the Type-I reverse leakage current is similar to the current of PN diode; type-III is more like the Schottky diode, especially when the reverse bias is below 200V; type-II is a typical MPS curves as we expected. The reason the leakage currents are different is that the thick photoresists masks for p ring implantation are not uniform and the implantation widths d are various. In any case, the reverse characteristics are determined by the screening effect of the p-n junctions. The Schottky barrier height is not an important factor for the reverse leakage current if the reverse bias is very large. The breakdown voltage of the MPS is about 600V. More than 70% of the parallel plane junction voltage have been achieved, as proves the junction-termination-extension (JTE) structure effective. Many of the big diodes (having a diameter of  $1000\mu m$ ) will break down when the reverse bias is below 50V and the yield is less than 10%, because there are many micropipes in the wafer as well as some defects induced in the process of etching, etc. However, as for the small devices (having a diameter of  $300\mu m$ ), the yield is more than 80%, though the leakage current and the breakdown voltage are almost the same, as is shown in Fig. 4 (a).

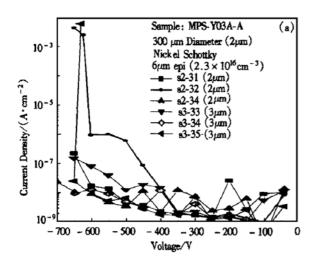

FIG. 4(a) Reverse Characteristics of MPS Diode with 300µm Diameter and Ni Contact

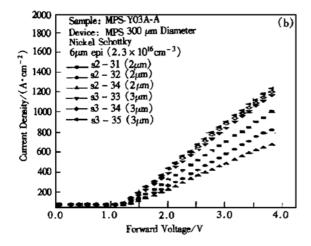

FIg. 4(b) Forward Characteristics of MPS Diode with 300µm Diameter and Ni Contact

From the forward I—V characteristics, the turn-on voltage of the 4H-SiC MPS diodes with Ni contact can be seen about 1.25V. The level-off of the forward current at a high forward bias is caused by the series resistance of diodes. The forward current density of MPS diode is a little higher if the reverse leakage current density is higher. Figure 4(b) shows the forward I—V characteristics of some 4H-SiC MPS devices with diameter of  $300\mu m$  and different Schottky contact ring width (ranging between  $2\mu m$  and  $3\mu m$ ). Obviously, higher forward current density can be obtained with a smaller width of the junction implantation

window. The dead space below the junction is minimized at the place where the current does not flow. For  $3\mu$ m devices, the forward current density is higher than  $1000\text{A/cm}^2$  at 3.5V (on-state resistance  $R_{\text{on}} = 3.5\text{m}\Omega \cdot \text{cm}^2$ ) while it is higher than  $600\text{A/cm}^2$  for  $2\mu$ m devices. Why small devices have high forward current density is not clear at this moment.

## 4 Summary and Conclusion

4H-SiC MPS diodes with Ni Schottky contact and junction termination extension (JTE) edge termination have been successfully designed, fabricated and characterized. The devices can block more than 600V reverse voltage, which is about 70% of the parallel plane junction breakdown voltage, and the lowest leakage current at -600V is  $1\times10^{-3}\text{A}$ cm<sup>2</sup>, while the forward current density at 3V is more than 200 A/cm<sup>2</sup> for 1000µm devices, 1000A/ cm<sup>2</sup> at 3.5V for 300µm devices. It shows that the reverse characteristics of the reverse leakage current are determined by the screening effect of the p-n junctions. It demonstrates that lower barrier Schottky metal can be used for MPS diode fabrication, with which, lower turn-on voltage can be obtained, while our keeping the low reverse leakage current. Further efforts are needed to optimize the fabrication in order to get a lower reverse leakage and higher forward conduction.

#### References

- [1] ZHANG Yuming and ZHANG Yimen, SiC Power Devices. Electronic Science and Technology Letter, 1996, **29**(11): 24—29 (in Chinese)[张玉明,张义门,SiC 功率器件,电子科技导报,1996, **29**(11): 24—291.

- [2] T.P.Chow, Materials Science Forum, 2000, 338—342: 1155—1160.

- [ 3 ] B. M. Wilamowski, Solid-State Electronics, 1983, 26: 491—495.

- [4] R. Held, N. Kaminski and E. Niemannn, Materials Science Forum, 1998, 264—268: 1057—1660.

- [5] F. Dalquist, C.-M. Zetterlink, M. Ostling and K. Rottner, Materials Science forum, 1998, 264—268: 1061—1064.

- [6] YU Ming-bin, MA Jian-ping, LUO Jia-jun and CHEN Zhiming, Nanocrystalline SiC Films Grown Si by HFCVD Method and its Photoluminescence, Chinese Journal of Semiconductors, 2000, 21: 673—676(in Chinese) [余明斌, 马剑平, 罗家骏, 陈治明, 在硅衬底上用 HFCVD 法生长的纳米薄膜及其室温光致发光, 半导体学报, 2000, 21(7): 673—676].

- [7] WANG Yinshu, LI Jinmin, ZHANG Fangfang and LIN Lanying, Growth of 3C-SiC on Si(100), Chinese Journal of Semiconductors, 1999, 20: 630—633(in Chinese)[王引书,李晋闽,张方方,林兰英,Si(100)面 3C-SiC 上的生长,半导体学报,1999, 20(7): 630—633].

- [8] LI Ningsheng, BAO Ximao, LIAO Liangsheng *et al.*, Preparation of Si-Based Nanocrystalline SiC and its Microstructure Analyses, Chinese Journal of Semiconductors, 1997, **18**: 731—733(in Chinese)[李宁生,鲍希茂,廖良生,等, 硅基纳米 SiC 的制备及其微结构分析,半导体学报, 1997, **18** (10): 731—733].

- [9] WANG Huiyao, Wang Yinyue, SONG Qing et al., Effect of Argon Ion Bombardment on Formation of 6H-SiC Prepared by Annealing of RF Sputtering α-SiC: H Film, Chinese Journal of Semiconductors, 1998, 19(8): 569—573(in Chinese) [王辉耀, 王印月, 宋青, 等, 氩离子轰击对射频溅射法制备的α-SiC: H 胰退化形成 6H-SiC 的影响, 半导体学报, 1998, 19(8): 569—573].

- [10] ZHANG Yuming, Luo Jinsheng and ZHANG Yimen, Au/

- NiCr Ohmic Contacts on n-type 6H-Silicon Carbide, Chinese Journal of Semiconductors, 1997, **18**(9): 718—720(in Chinese)[张玉明,张义门,罗晋生,n型6H-SiC 体材料欧姆接触的制备,半导体学报,1997, **18**(9): 718—720].

- [11] ZHANG Yuming, ZHANG Yimen and LUO Jinsheng, Pt Schottky Barrier Diodes on n-type 6H-Silicon Carbide, Chinese Journal of Semiconductors, 1999, **20**(11): 1040—1043 (in Chinese)[张玉明,张义门,罗晋生,SiC 肖特基势垒二极管的研制,半导体学报,1999, **20**(11): 1040—1043].

- [12] ZHANG Yuming, ZHANG Yimen and LUO Jinsheng, Study of 6H-SiC MOSFET, Research & Progress of Solid State Electronics, 2000, **20**(1): 1—6(in Chinese) [ 张玉明,张义门,罗晋生,6H-SiC MOS 场效应晶体管的研制,固体电子学研究与进展, 2000, **20**(1): 1—6].

- [13] Yuming Zhang and Yimen Zhang, High-Field and High-Temperature Transport in n-type 3C-SiC, The 2nd International Conference on Modeling and Simulation of Microsystem, Semiconductor, Sensors and Actuators, San Juan, Puerto Rico, USA, April 19, 1999.

- [14] WANG Shu-rui, LIU Zhong-li, XU Ping et al., 6H-SiC High Voltage Schottky Barrier Diodes, Chinese Journal of Semiconductors, to be published (in Chinese) [王姝睿, 刘忠立,徐萍,等, 6H-SiC 高压肖特基势全二极管,半导体学报,特发表].

## 4H-SiC 混合 PN/Schottky 二极管的研制

张玉明<sup>1</sup> 张义门<sup>1</sup> P. Alexandrov<sup>2</sup> J. H. Zhao<sup>2</sup>

(1 西安电子科技大学微电子所,西安 710071,中国)

(2 Department of Electrical and Computer Engineering, The State University of New Jersey, NJ 08854-8058, USA)

**摘要**:报道了 4H-SiC 混合 PN/Schottky 二极管的设计、制备和特性.该器件用镍作为肖特基接触金属,使用了结终端扩展 (JTE) 技术.在肖特基接触下的 n 型漂移区采用多能量注入的方法形成 P 区而组成面对面的 PN 结,这些 PN 结将肖特基接触屏蔽在高场之外,离子注入的退化是在 1500℃下进行了 30min.器件可耐压 600V,在 600V时的最小反向漏电流为  $1\times10^{-3}$  A/cm².  $1000\mu$ m 的大器件在正向电压为 3V 时电流密度为 200 A/cm², 而  $300\mu$ m 的小尺寸器件在正向电压为 3.5V 电流密度可达 1000 A/cm².

关键词: 功率器件; 碳化硅; 半导体二极管; MPS

EEACC: 2560H: 2550: 2520M PACC: 7340L

中图分类号: TN311+.7 文献标识码: A 文章编号: 0253-4177(2001)03-0265-06

张玉明 男, 1965 年出生, 博士, 副教授, 从事新型半导体器件、TCAD 和 VLSI CAD 的教学和科研工作. 目前主要研究碳化硅器件的器件物理、丁艺、模型和模拟.

张义门 男, 1941 年出生, 教授, 博士导师, 主要从事 VLSI 中器件的模型和模拟、VLSI CAD、量子阱器件和宽禁带高温微电子学.