# Schottky Barrier Characteristics of Polycrystalline and Epitaxial CoSi<sub>2</sub>/n-Si(111) Contacts Formed by Solid State Reaction\*

ZHU Shi-yang, RU Guo-ping, QU Xin-ping and LI Bing-zong

(Department of Electronic Engineering, Fudan University, Shanghai 200433, China)

Abstract: Polycrystalline and epitaxial CoSi<sub>2</sub> films are formed on the n-Si (111) substrates by solid state reaction of the as-deposited Co single-layer and Co/Ti bilayer with Si, respectively at different annealing phase. The CoSi<sub>2</sub>/Si Schottky contacts are measured with the current-voltage and capacitance-voltage (I-V/C-V) techniques within the range of temperature from 90K to room temperature. The measured I-V characteristics have been analyzed with a model based on the inhomogeneity in Schottky barrier height, i. e., at high temperatures ( $\geq \sim 200$ K) or low temperatures but with a large bias, the I-V curves can be described by using the thermionic emission theory with a Gaussian distributed barrier height over the whole junction, while at low temperatures and with a small bias, the current is dominated by some small patches with low barrier height. It results in a plateau-like section in the low temperature I-V curves around  $10^{-7}$ A. At room temperature, the barrier height of polycrystalline CoSi<sub>2</sub>/Si deduced from the I-V curve is about 0.57eV. For epitaxial CoSi<sub>2</sub>, the barrier height depends on its final annealing temperature and increases from 0.54eV to 0.60eV with the annealing temperature increasing from 700°C to 900°C.

**Key words:** Schottky barrier; silicide; I-V/C-V; inhomogeneity

PACC: 7330; 7340N; 0780; 0750

CLC number: T N 304. 055 Document code: A Article ID: 0253-4177(2001) 06-0689-06

#### 1 Introduction

Cobalt silicide (CoSi<sub>2</sub>) is an important candidate of contacts and interconnects in modern very large scale integration (VLSI) technology due to its low resistivity, high thermal stability and no nucleation problems in narrow lines<sup>[1]</sup>. CoSi<sub>2</sub> has the same structure as CaF<sub>2</sub> with a small lattice mismatch with respect to Si, which makes the epitaxial growth of CoSi<sub>2</sub> on Si relatively easy. It is well known that appropriate heat treatment of Co/

Ti bilayer on both (111) and (100) oriented Si results in an epitaxial CoSi2 film (TIME: Ti-interlayer mediated epitaxial) [2], while the ex-situ annealing of a single Co layer on Si results in a polycrystalline silicide. Much research has been done on their formation mechanisms as well as the structural and electrical properties [2-6]. The Schottky barrier properties of a metal-semiconductor (M-S) contact are usually studied with current-and capacitance-voltage (I-V/C-V), photoemission spectroscopy and ballistics electron emission microscopy (BEEM). It is known that the

<sup>\*</sup> Project Supported by a Bilateral Cooperation Program (Bil 96/74/B17) from the Flemish Ministry of Science and Technology and the Ministry of Science and Technology of China, and by the Science and Technology Development Foundation of Shanghai Under Grant No. 981C 14004

ZHU Shi-yang Ph. D, associate professor, his current research interests are in silicides, and Schottky barrier properties of metal-semiconductor contacts.

LI Bing-zong professor, his work focuses on silicides and other thin solid films.

Schottky barrier height (SBH) of a CoSi2/Si contact depends on its formation parameters, such as growth type (solid state reaction, molecular epitaxy, ion implantation synthesis), procedure, annealing orientation, concentration, etc<sup>[5-10]</sup>. The electrical properties of CoSi2 films formed on the (100) oriented n-Si substrates by solid state reaction have been reported<sup>[7,8]</sup>. The epitaxial CoSi<sub>2</sub>/Si(100) contacts have slightly lower SBH than the polycrystalline ones due to the Ti incorporation in the M-S interface, which also influences the barrier height distribution and the temperature coefficient. Both I-V/C-V and BEEM measurements have shown that MBE-grown CoSi2(111)/Si(111) has a lower barrier height than CoSi<sub>2</sub>(100)/Si(100)<sup>[9,10]</sup>. In this paper, the SBH properties of CoSi2/Si (111) contacts formed by solid state reaction are studied by I-V/C-V from 90K to room temperature.

However, the charge carrier transport through a M-S junction is still to be defined. The forward I-V characteristics are commonly analyzed by using the thermionic emission (TE) theory with a uniform barrier height over the whole junction[11], however, which fails to describe the observed I-V results. Recently, the assumption that the barrier height is inhomogenous [12-14] has been confirmed by BEEM measurements [15]. By using a modified TE model with a Gaussian distributed barrier height over the whole junction, all the phenomena can be explained, including the different SBH deduced from different methods, non-linearity of the Richardson plot, strong dependence of both the apparent SBH and the ideality factor. However, it cannot explain the double threshold phenomenon that is sometimes observed in low-temperature I-V curves in the middle bias region and is attributed to the small patches of low barrier height. The I-V curves are well described over the whole temperature region with the combinative model of the Gaussian distribution model and the pinch-off one.

## 2 Experiment

The substrates used in this work were n<sup>-</sup>/n<sup>+</sup> epitaxial Si (111) wafers (phosphor doped). The doping level of the epitaxial layer was about 8× 10<sup>15</sup>cm<sup>-3</sup> and the resistivity of the n<sup>+</sup> substrate was about 0.01Ω • cm. After the thermal oxide layer of 300nm had been grown, the square windows in different sizes were opened with the standard lithography and wet etching procedures. Immediately after the standard RCA cleaning and dipping in a diluted HF solution to remove the native oxide on the active area, the wafers were loaded in a chamber of Oxford sputtering system with a base pressure of about 1×10<sup>-4</sup>Pa. Titanium and cobalt were sequentially deposited without breaking the vacuum. The CoSi2 silicidation was formed after a two-step ex-situ RTA (rapid thermal annealing) in the N2 ambient with an interval of selective etching: first annealing at 600°C for 1 min, then etching in a boiling solution of H<sub>2</sub>SO<sub>4</sub>: H<sub>2</sub>O<sub>2</sub>= 3:1 for 5min and in a boiling solution of NH<sub>4</sub>OH:  $H_2O_2: H_2O = 1:2:5$  for 2min, finally annealing for 1 min at different temperatures (700, 800 or 900°C). An In-Ga alloy (liquid) was used as a backside ohmic contact.

The I-V/C-V measurements were carried out automatically with a computer controlled system composed of a Keithley 619 electrometer and a multi-frequency LCR HP 4274A meter. The diode was cooled down by liquid N<sub>2</sub> and the variation in the temperature is less than  $\pm 4$ K during the one-temperature-point measurements.

#### 3 Results and Discussion

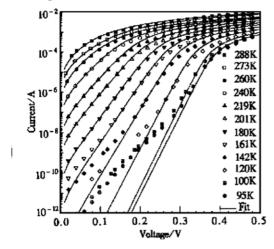

Forward *I-V* characteristics of an epitaxial CoSi<sub>2</sub>/Si(111) at the temperature between 95K and 288K are displayed in Fig. 1. The CoSi<sub>2</sub> film is formed of Co(5nm)/Ti(3nm)/Si after the final annealing at 700°C and the diode area is about 0.008cm<sup>2</sup>. Sheet resistance and XRD (X-ray

diffraction) measurements show that the epitaxial cobalt disilicide with low resistivity has been formed after annealing at 700°C for 1min. With Rutherfold backscatting spectroscopy, the channeling minimum is obtained about 10% [2].

FIG. 1 Forward *I-V* Characteristics of Epitaxial CoSi<sub>2</sub> (111)/Si (111) Diode at Different Temperatures and Their Theoretical Fitting Curves Based on Modified TE Model

The forward I—V curves in Fig. 1 are analyzed with the expression based on the TE model<sup>[13]</sup>:

$$I = AA^{**}T^{2}\exp(-q\Phi^{I-V}/(kT))$$

$$\times \{\exp[q(V - IR_{s})/(nkT)] - 1\} (1)$$

where A is the diode area,  $A^{**}$  is the Richardson constant (for n-Si,  $A^{**} = 112A \cdot cm^{-2} \cdot K^{-2}$ ),  $\Phi^{l+l}$ and n are the apparent barrier height and the apparent ideality factor obtained from the forward I-V characteristics,  $R_s$  is the series resistance. The least square fitting is made with  $\Phi^{I-V}$ , n and  $R_s$  as adjustable parameters. The fitting curves are also shown in Fig. 1. At high temperatures or at low temperatures but with large bias, the fitting curves match the experimental data quite well. However, the deduced values of  $\Phi^{\prime-\nu}$  and n are temperature dependent, especially at low temperatures. The phenomenon has been explained by using the barrier height distribution model<sup>[12, 13]</sup>. Assuming the barrier height over the whole junction is a Gaussian distribution, and the carrier transport through the different barrier height independently

(parallel conductor model), the total current is given by an expression similar to Eq. 1 but with both  $\Phi^{l^{-l}}$  and n temperature-dependent<sup>[13]</sup>:

$$\Phi^{I-V} = \overline{\Phi} - \sigma_{\Phi}^2 q / (2kT) \tag{2}$$

$$1/n = (1 - \rho_1) + q\sigma_{\Phi}\rho_2/(kT)$$

(3)

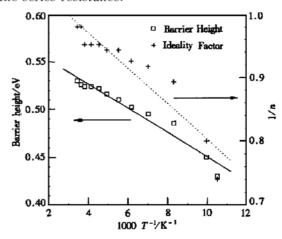

where  $\Phi$  is the average barrier height and  $\sigma_{\Phi}$  is the standard deviation.  $\rho_1$  and  $\rho_2$  are the bias coefficients of  $\Phi$  and  $\sigma_{\Phi}$ , respectively. It implies that both plots of  $\Phi^{I^{-V}}$ –I/T and 1/n–1/T gives a straight line, which are shown in Fig. 2. The values obtained from the least square linear fitting of the experimental data are:  $\Phi$ = 0.58eV,  $\sigma_{\Phi}$ = 0.047eV,  $\rho_1$ = -0.08 and  $\rho_2$ = -0.05, in agreement with the values reported [7,13]. However, the linearity of both plots is not very good, which is attributed to the temperature dependence of both  $\Phi$  and  $\sigma_{\Phi}$ , and the relatively large error of  $\Phi^{I^{-V}}$  and n due to the effect of the series resistance.

FIG. 2 Apparent Barrier Heights and Ideality Factors as a Function of Reciprocal Temperature and Their Linear Fittings

Figure 1 shows that there is a plateau-like section in the low temperature I-V curves around  $10^{-7}$ A. Such double threshold behavior is attributed to the small patches with low barrier height. According to the pinch-off model, the current through the small patch can be expressed by  $V^{14}$ :

$$I_{p} = A_{eff}A^{**}T^{2}\exp(-q\Phi_{eff}/(kT))$$

$$\times \{\exp[q(V - I_{p}R_{sr})/(kT)] - 1\}$$

(4)

where  $\Phi$  and A are the effective barrier height and the effective area of the patch, respectively. Both of them depend on the patch's parameter  $\mathcal{Y}$ :

$$Y = 3(\Delta R_0^2/4)^{1/3} \tag{5}$$

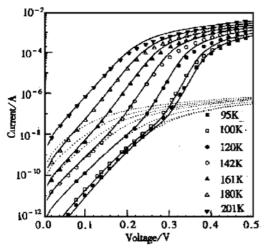

where  $R_0$  is the patch radius and  $\Delta$  is the barrier height reduction at the M-S interface. Rsr is the series resistance of the patch, whose value is much larger than  $R_s$  due to the pinch-off effect around the patch. The total current is the sum of  $I_P$  and the current obtained from Eq. 1. Figure 3 shows the fitting curves with the parameters that  $Y = 4.4 \times$  $10^{-4} \text{ cm}^{2/3} \text{ V}^{1/3}$  and  $R_{\text{sr}} = 5 \times 10^{5} \Omega$ . In the high bias region, the patch current is smaller than the current through the whole junction due to the large local series resistance of the patch. There exists a critical bias, at which the patch current equals to the whole junction current. With the temperature increasing, the critical bias decreases. Above 180K, the patch current is negligible, and the I-V curves at the whole bias can be described by Eq. 1 alone.

FIG. 3 Experimental and Theoretical *I-V* characteristics at Low Temperatures for Above Epitaxial CoSi (111)/Si (111) Diode The dotted curves show a patch current and the solid curves are the total current.

The diode has also been measured by C–V at the frequency of 100kHz and 500kHz. However, the plot of  $1/C^2$ – $V_r$  deviates from the linearity significantly in the large reverse bias ( $V_r$ ) region.

The barrier height can only be deduced from the small reverse bias region, thus the deduced values of  $\Phi^{C-V}$ , from 0.57 to 0.64eV, have a relatively Taking error. the barrier inhomogeneity into account, the results are in agreement with  $_{

m those}$ deduced characteristics [12]. Moreover, the barrier height deduced from C-V increases slightly with the temperature decreasing. However, the relatively large experimental error of  $\Phi^{C-V}$  makes it impossible to obtain a significative temperature coefficient of  $\Phi^{C-V}$ .

The other two epitaxial CoSi<sub>2</sub>/n-Si (111) diodes, formed by annealing for 1min at 800°C and 900°C respectively, have also been studied, with similar I-V and C-V characteristics obtained. The barrier height deduced from the room temperature I-V curve is about 0.54eV for the sample annealed at 800°C and 0.60eV for the one annealed at 900°C. The C-V results also show the slight increase in the barrier height with the increase of the annealing temperature.

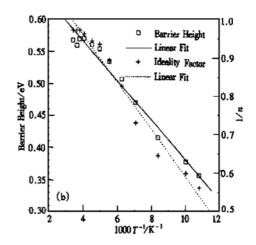

On the other hand, the barrier height of a polycrystalline CoSi<sub>2</sub>/n-Si (111) independent on its annealing temperature. The barrier height deduced from the room temperature I-V curve is about 0.57eV for both samples annealed at 800°C and 900°C respectively. The polycrystalline CoSi<sub>2</sub>/Si diode of 0.008cm<sup>2</sup> in size will be analyzed in details below, which is formed by Co(20nm)/Si(111) with the final annealing at 800°C. Figure 4 (a) displays its forward I-V characteristics at temperatures from 92K to 291K. The theoretical fitting curves are the sum of two components:  $I_{\text{total}} = I_{\text{th}} + I_{\text{patch}}$ , where  $I_{\text{th}}$  is the current through the whole junction with a Gaussian distributed barrier height and I patch is a patch current. Similar to the epitaxial CoSi2/Si (111) diodes mentioned above, the experimental I-V characteristics at the whole bias can be fitted over the whole temperature region. In the small bias region and at low temperatures, the patch current dominates. The patch parameter deduced

from the fitting is:  $Y = 4.05 \times 10^{-4} \text{ cm}^{2/3} \text{ V}^{1/3}$ . At high temperatures or in the large bias region but at low temperatures, the current through the whole junction dominates. The apparent barrier height and the apparent ideality factor are displayed in Fig. 4 (b) as a function of the reciprocal

temperature. From the least square linear fitting of both plots of  $\Phi^{-1}$ -1/T and 1/n-1/T, the mean of barrier height, the standard deviation and their bias coefficients are obtained as:  $\Phi = 0.69 eV$ ,  $\sigma_{\Phi} =$ 0. 07eV,  $\rho_{1} = -0.2$  and  $\rho_{2} = -0.06$ , respectively.

Results of Polycrystalline CoSi<sub>2</sub>/Si(111) Diode Reciprocal Temperature and Their Linear Fittings

(a) Forward Experimental I-V Characteristics (Symbols) and Calculated Ones (Solid Curves); (b) Apparent Barrier Heights and Ideality Factors as a Function of

The barrier height of the epitaxial CoSi2/Si (111) diodes is slightly lower than that of the polycrystalline ones. Similar phenomenon is also observed for the CoSi2/Si(100) diodes. It can been attributed to the Ti incorporation in the CoSi2-Si contact during the TIME process<sup>[7]</sup>. It is known that Ti/Si or TiSi2/Si contact has a lower barrier height than CoSi2/Si contact [16]. With the annealing temperature of the Co/Ti/Si system increasing, the Ti concentration in the CoSi2/Si interface is reduced, thus the barrier height increases slightly. Compared with our previous study on CoSi2/Si (100) diodes<sup>[7,8]</sup>, the barrier height of CoSi<sub>2</sub>/Si (111) is lower than that of CoSi2/Si(100) diodes. It reveals that the barrier height depends on the orientation of the CoSi2 structure, which is in agreement with the *I*-*V* measurements on the MBE growth CoSi2/Si diodes reported by Jimenez et al. [9] and the BEEM measurements reported by Sirringhaus et al. [10].

### Conclusion

The forward I - V characteristics of both polycrystalline and epitaxial CoSi2/Si(111) diodes are analyzed by using the combined model of the Gaussian distribution model with the barrier heights over the whole junction and the pinch-off model with the low barrier height patch. The epitaxial CoSi<sub>2</sub>(111)/Si(111) has a lower barrier height than the polycrystalline ones. It is attributed to the Ti incorporation into the CoSi2-Si interface during the solid state reaction of the Co/Ti/Si system as well as the dependence of the barrier height on the orientation of the CoSi2 layer. The CoSi2 (111)/Si(111) contact has a lower barrier height than other orientations on Si substrate.

Acknowledgements The authors would like to thank Prof. Cardon, Prof. Van Meirhaeghe and Dr. Detavernier in the University of Ghent, Belgium for 694 半 导 体 学 报 22 卷

their useful discussions.

#### References

- [1] K. Maex, A. Lauwers, P. Besser, E. Kondoh, M. De Potter and A. Steegen, IEEE Trans. Electron Devices, 1999, 46 (7): 1545—1550.

- [2] Bing-Zong Li, Wei-Jun Wu, Kai Shao, Zhi-Guang Gu et al., Advanced Metallization for Devices and Circuits-Sciences, Technology and Manufacturability, Ed. by S. P. Murarka et al., MRS'1994, 337: 449.

- [3] C. Detavernier, R. L. van Meirhaeghe, F. Cardon, K. Maex, H. Bender and Shiyang Zhu, J. Appl. Phys., 2000, 88 (1): 133—140.

- [4] A. Vantomme, M. A. Nicolet and N. D. Theodore, J. Appl. Phys., 1994, 75(8): 3882—3891.

- [5] A. Lauwers, K. K. Larsen, M. Van Hove et al., J. Appl. Phys., 1995, 77(6): 2525—2536.

- [6] S. Hatzikonstantinidous, P. Wikman, S. L. Zhang and C. S.

- Petersson, J. Appl. Phys., 1996, 80(2): 952-961.

- [7] S. Y. Zhu, C. Detavernier, R. L. Van Meirhaeghe, X. P. Qu, G. P. Ru et al., Semicond. Sci. Tech., 2000, 15(4): 349—615.

- [8] S. Y. Zhu, R. L. Van Meirhaeghe, C. Detavernier, F. Cardon et al., Solid State Electronics, 2000, 44(4): 663—671.

- [9] J. R. Jimenez, L. J. Schowalter, L. M. Hsiung et al., J. Vac. Sci. Technol. A, 1990, 8(3): 3014—3018.

- [ 10] H. Sirringhaus, E. Y. Lee, U. Kafader and H. Van Känel, J. Vac. Sci. Technol. B, 1995, 13(4): 1848—1852.

- [11] E. H. Rhoderick and R. H. Williams, Metal-Semiconductor Contacts, 2nd ed., Oxford: Clarendon, 1988.

- [12] Y. P. Song, R. L. Van Meirhaeghe, W. H. Laflere and F. Cardon, Solid State Electronics, 1986, 29(6): 633—638.

- [13] J. H. Werner and H. H. Guttle, J. Appl. Phys., 1991, 69(3): 1522—1533.

- [14] R. T. Tung, Phys. Rev., B, 1992, 45(23): 13509—13523.

- [15] H. Palm, M. Arbes and M. Schulz, Phys. Rev. Lett., 1993, 71 (14): 2224—2227.

- [16] M. O. Aboelfotoh, J. Appl. Phys., 1988, 64(8): 4046-4055.

## 固相反应制备的多晶和外延 CoSi2/n-Si(111) 接触的肖特基特性\*

竺士炀 茹国平 屈新萍 李炳宗

(复旦大学电子工程系, 上海 200433)

摘要:通过硅 (111) 衬底淀积的单层 Co 或 Co/Ti 双金属层在不同退火温度的固相反应,在硅上形成制备了多晶和外延 CoSi<sub>2</sub> 薄膜. 用电流-电压和电容-电压 (I-V/C-V) 技术在 90K 到室温的温度范围内测量了 CoSi<sub>2</sub>/Si 肖特基接触特性。用肖特基势垒不均匀模型分析了所测得的 I-V 特性,在较高温度下 ( $\geq \sim 200$ K) 或较低温度的较大偏压区域,I-V 曲线能用热激发和在整个结面积上势垒高度的高斯分布模型描述. 而在较低温度的较小偏压区域,电流由流过一些小势垒高度微区的电流决定,从而在低温 I-V 曲线上在约  $10^{-7}$  A 处有一个"曲折". 在室温下,从 I-V 曲线得到的多晶 CoSi<sub>2</sub>/Si 的势垒高度为约 0. 57eV. 对外延 CoSi<sub>2</sub>,势垒高度依赖于最后退火温度,当退火温度从 700 个升到 900 个,势垒高度从 0. 54eV 升高到 0. 60eV.

关键词: 肖特基势垒; 硅化物; I-V/C-V; 不均匀性

PACC: 7330; 7340N; 0780; 0750

中图分类号: TN 304.055 文献标识码: A 文章编号: 0253-4177(2001)06-0689-06

<sup>\*</sup> 中-比双边合作和上海市科委资助项目.

竺士炀 博士,副教授,从事硅化物和金属-半导体接触肖特基势垒特性研究.

李炳宗 教授,从事固体薄膜和硅化物研究.