# Analytical Model of Surface Field Distribution and Breakdown Voltage for RESURF LDMOS Transistor<sup>\*</sup>

### HE Jin and ZHANG Xing

(Institute of Microelectronics, Peking University, Beijing 100871, China)

Abstract: An analytical model of the surface field distribution and breakdown voltage of the reduced surface field lateral double diffusion MOS transistor is proposed. Based on the 2-D Poisson's equation solution, the derived model gives the closed form solutions of the surface potential and electrical field distributions as a function of the structure parameters and drain bias. A criterion for obtaining the optimal trade-off between the breakdown voltage and on-resistance is also presented to serve to quantify the maximum breakdown voltage and optimal relations of all design parameters. Analytical results are shown in good agreement with the numerical analysis obtained by the semiconductor device simulator MEDICI and previous reported experimental data.

Key words: RESURF principle; LDM OS power transistor; breakdown voltage; surface field; on-resistance; opti-

mum design

EEACC: 2150R; 2560B

CLC number: TN386 Article ID: 0253-4177(2001)09-1102-05 Document code: A

#### 1 Introduction

In recent years, Reduced Surface Field (RESURF) technology has been widely used in high-voltage, low on-resistance lateral power devices such as Lateral Double Diffusion Metal-Oxide-Semiconductor transistor (LDMOS), Lateral Insulated Gate Bipolar Transistor (LIGBT), Junction Field Effect Transistor (JFET) and dielectrically isolated devices for implement of the High-Voltage-Integration Circuits (HVIC's) and Smart Power Integration Circuits (SPIC's). Previous many numerical analysis works have fairly well discussed the influence of various parameters on the breakdown voltage and on-resistance, and sev-

eral models have been proposed for determination of optimal epilayer thickness and doping concentration, drift region length and substrate doping concentrations [1-4].

However, the previous numerical analysis were just completed for some especial structures and all developed analytical models were also based on the approximate 1D Poisson equation solution or some especial assumptions<sup>[5-7]</sup>. Because of the two-dimensional distribution characteristics of the electrical field in the drift region, any 1D analysis could only figure out an approximate contour of the breakdown characteristics of the RESURF devices. Therefore, the correction and accuracy of those approximations and assumptions need to be further proven for the general case. To our knowledge, there has been no any 2D analytical solution for the

<sup>\*</sup> Project Supported by Special Funds for Major State Basic Research Project (G20000365).

HE Jin post-doctoral researcher. His current research interests focus on the deep sub-micron SOI device optimum and characterization and new MOS-based power devices.

surface field of RESURF structure LDMOS so far.

This work is to develop a 2D analytical model for calculating the surface field distribution and breakdown voltage of the RESURF LDMOS transistor, based on the Poisson's solution. From this analysis, the surface field and potential distributions have been expressed in terms of the drift region length, epilayer layer doping concentration and thickness and substrate doping concentration. The quantified optimum criterion for the maximum breakdown voltage and lower on-resistance has also been obtained. Analytical results show in good agreement with the numerical analysis and previous reported data.

## 2 Analytical Model

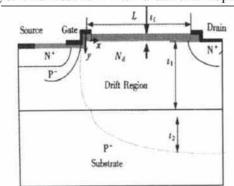

In present analysis, the simplified investigated structure is shown in Fig. 1. As shown in this figure, the drift region length of the RESURF LD-MOS transistor is defined as the n type region length L between the  $\mathbf{n}^+$  drain and  $\mathbf{p}^+$  well. The epilayer thickness is  $t_1$  with a uniform doping con-

FIG. 1 Cross-Section of RESURF LDMOS Transistor

centration  $N_{\rm d}$ . Assuming the substrate is too thick enough to deplete the substrate charge, the substrate depletion layer thickness is  $t_2$ , with doping concentration  $N_{\rm sub}$ .  $t_{\rm f}$  is the thickness of the field oxide layer with the dielectric constant of  $\epsilon_{\rm ox}$ . x and y measure the horizontal and vertical positions relative to silicon surface, respectively. The device is biased in the off-state configuration; substrate,

source and gate are grounded while the drain is biased to a positive voltage  $V_d$ .

The potential function  $\Phi(x, y)$  in the silicon film must be satisfied by Poisson equation, yielding:

$$\frac{\mathrm{d}^2 \Phi(x, y)}{\mathrm{d}x^2} + \frac{\mathrm{d}^2 \Phi(x, y)}{\mathrm{d}y^2} = -\frac{qN_{\mathrm{d}}}{\epsilon_{\mathrm{Si}}} \tag{1}$$

The region under investigation is the box drift region. It is possible to derive from the 2D Poisson equation a 1D equation describing the surface potential in the lateral coordinate (x). In this work, a more general analysis based on the theory of Reference [8] integrates the Poisson equation over the y-direction in the drift region.

$$\int_0^{\epsilon} \frac{\partial^2 \Phi(x,y)}{\partial x^2} dy + E_y(x,0) - E_y(x,t_1) = -\frac{qN_d}{\epsilon_{si}} t_1$$

(2)

where for the purpose of analytical investigation, the effect of the junction depth is neglected.

Under the assumption of a 1D electrical field in the SiO<sub>2</sub> material, the continuity of electric flux along the front-Si/SiO<sub>2</sub> interface makes the boundary conditions for (2) satisfy

$$E_{y}(x,0) = -\frac{\epsilon_{\text{ox}}}{\epsilon_{\text{Si}}} \times \frac{\Phi(x) - V_{\text{gs}}'}{t_{\text{f}}}$$

(3)

where  $\Phi(x) \equiv \Phi(x, 0)$ , is the potential function along the front Si/SiO<sub>2</sub> interface.  $V_{gs}^{'} = V_{gs} - V_{FB,f}$ , is the effective gate-to-source bias voltage, here  $V_{FB,f}$  is the channel flat-band voltage.

Because the gate oxide layer and substrate bias equal zero, neglecting the influence of the work function difference between the metal and semiconductor on the electrical field, the electric field at the Si/SiO<sub>2</sub> interface can be expressed by

$$E_{y}(x,0) = -\frac{\epsilon_{ox}}{\epsilon_{Si}} \times \frac{\Phi(x)}{t_{f}}$$

(4)

From (2) to (4), one obtains

$$\int_{0}^{t} \frac{\partial^{2} \Phi(x, y)}{\partial x^{2}} dy - \frac{\epsilon_{ox}}{\epsilon_{Si}} \times \frac{\Phi(x)}{t_{f}} - E_{y}(x, t_{1}) = -\frac{qN_{d}}{\epsilon_{Si}} t_{1}$$

(5)

The relation between  $\Phi(x)$  and  $\Phi(x)$  is derived by solving the continuity equation of the electric flux in the vertical direction

$$\frac{2(\Phi - \Phi_0)}{t_1} = \frac{2\Phi_0}{t_2} = E_y(x, t_1)$$

(6)

where  $\Phi(x) \equiv \Phi(x, t_1)$ , is defined as the electrostatic potential at the metallurgical junction of the vertical  $\mathbf{n}^-/\mathbf{p}^-$  junction. From equation (6), we can directly express  $E_{\mathcal{I}}(x, t_1)$  as a function of the surface potential and depletion layer thickness.

According to the RESURF principle, the epilayer should be completely depleted and the depletion approximation is suitable for the drift region. At the first-order approximation, we can assume  $\frac{\partial \Phi(x,y)}{\partial x^2} \approx \frac{\partial^2 \Phi(x)}{\partial x^2}$ . Putting everything into (2)

and making further mathematics simplification, (2) transforms into the 1D differential equation:

$$\frac{\mathrm{d}^2 \Phi(x)}{\mathrm{d}x^2} - \alpha_f \Phi(x) = \beta_f \tag{7}$$

with

$$a_{\ell} = \frac{2\epsilon_{\text{ox}}}{t_1 t_{\ell} \epsilon_{\text{Si}}} + \frac{2}{t_1 (t_1 + t_2)}$$

and  $\beta_{\ell} = -\frac{q N_{\text{d}}}{\epsilon_{\text{Si}}}$ .

In order to determine depletion layer thickness in the substrate side, one must solve Poisson equation of the double-sided pn junction along the vertical direction. Due to the little non-uniformity of the substrate depletion thickness along the drift region length direction, we can assume a uniform depletion thickness at first-order approximation. In this case, the depletion thickness within the substrate can be evaluated by using one dimension Poisson equation for the vertical direction drain voltage at the drain region edge. Similar to equation (6), neglecting the influence of the junction depth of the drain region,  $t_2$  can be included in the following form based on the general formulae for the double-sided junction

$$E_{y(x,t_1)_{\text{max}}} = \frac{2(V_d - \Phi_b)}{t_1} = \frac{qN_{\text{sub}}t_2}{\epsilon_{\text{Si}}}$$

(8)

Based on the basic theory of the pn junction,  $\mathcal{P}(x)$  can be simplified expressed into

$$\Phi_{b}(x) = \frac{qN_{\text{sub}}}{2\epsilon_{\text{Si}}}t_{2}^{2}$$

(9)

Combination (8) with (9), a quadric equation gives

$$\frac{t_2}{t_1} = \frac{1}{2} \left( \sqrt{1 + \frac{8\epsilon_{\rm si}V_{\rm d}}{qN_{\rm sub}t_1^2}} - 1 \right)$$

(10)

It is evident that  $t_2$  tends to zero when the substrate doping concentration  $N_{\text{sub}}$  tends to a very high value such as infinity. The above form is applicable only when the drain voltage makes the depletion width larger than  $t_1$ . In general, the high drain voltage at the off state makes the epilayer to be depleted enough. Therefore, the above analysis always exists well.

Solving (7) with boundary conditions  $\Phi(0) = 0$  and  $\Phi(L) = V_d$  and defining  $\Theta_f = -\frac{\beta_f}{\alpha_f}$  and  $\tau_f \equiv (1/a_f)^{1/2}$  gives

$$\Phi(x) = \Theta_{f} + \frac{(V_{d} - \Theta_{f}) \sinh\left[\frac{x}{\tau_{f}}\right] - \Theta_{f} \sinh\left[\frac{L - x}{\tau_{f}}\right]}{\sinh\left[\frac{L}{\tau_{f}}\right]}$$

(11)

The surface field distribution along the semiconductor surface is obtained by differentiating (11)

$$E(x,0) = -\frac{\mathrm{d}\Phi}{\mathrm{d}x} = -\frac{(V_{\mathrm{d}} - \theta_{\mathrm{f}})\cosh\left[\frac{x}{\tau_{\mathrm{f}}}\right] + \theta_{\mathrm{f}}\cosh\left[\frac{L - x}{\tau_{\mathrm{f}}}\right]}{\tau_{\mathrm{f}}\sinh\left[\frac{L}{\tau_{\mathrm{f}}}\right]}$$

(12)

#### 3 Results and Discussion

Based on the above analysis, the potential and electric field distributions along the semiconductor surface can be readily demonstrated. And the effect of the field oxide layer and silicon film structure on the potential and field can also be analyzed. In order to verify the proposed model, the 2D device simulation is performed using MEDICI for the same structure<sup>[9]</sup>.

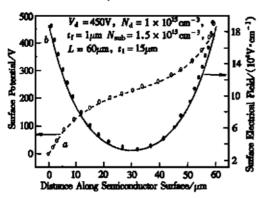

Figure 2 shows the analytical results of the surface potential and field distributions obtained from equations (11) and (12) for one RESURF LDMOS transistor together with the simulation results. In the figure, the curves denote the analytical results and the black points represent the numerical results, respectively. A fairly accordance between the analytical and numerical simulation results may be found in general. The discrepancies

between both are due to the penetration of the space charge region into  $p^+$  base region and  $n^+$  drain diffusion region as can be seen from the surface potential and field at x=0 and x=L. However, this kind of discrepancies has a little effect on the breakdown voltage analysis.

Curve *a* in Fig. 2 indicates that the potential distribution along the silicon surface is similar to the combination of the p<sup>+</sup> n<sup>-</sup> and n<sup>+</sup> n<sup>-</sup> abrupt junctions. The total potential drop at the both junctions coincides with the applied voltage.

Curve b in Fig. 2 shows the electrical field distribution along silicon film surface. It is evident that there are two edge electric field peaks along the silicon surface, one appears at the  $p^+$   $n^-$  junction interface and the other at the  $n^+$   $n^-$  junction interface. This coincides with the present and previous numerical analysis results<sup>[1,2]</sup>. Meanwhile, it can be found that the relative magnitude of the two edge peak fields is equal each other. This is because the all structure parameters satisfy the optimal condition, as shown by Colak´ results<sup>[3]</sup>.

FIG. 2 Surface Potential and Electrical Field Distribution Along Semiconductor Surface

In the design of RESURF LDMOS devices, the epilayer thickness, doping concentration in the drift region, drift region length and field oxide layer thickness are of very importance which determine the off-state breakdown voltage and forward conduction characteristics of the devices. The following discussion will give which optimum relationship.

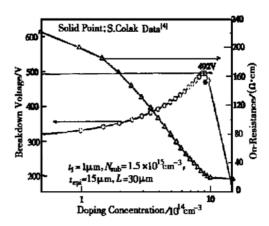

Based on the expression of the surface electrical field given by (12), utilizing the critical breakdown electrical field concept  $E_{\text{max}}(x) = E_{c} = 2 \times$ 10<sup>5</sup>V/cm can directly evaluate the breakdown voltage for the different drift region doping concentrations. Meanwhile, the drift region on-resistance perunit width is also evaluated from the expression obtained by Cloak [3,4]. One can observe there exists an optimal epilayer doping concentration at which the maximum breakdown voltage happens and the lower on-resistance is obtained, as shown in Fig. 3. The characteristics of the breakdown voltage versus epi-layer doping concentration curve are similar to the results given by Apples [2]. Moreover, the analytical results show in good agreement with the experimental results obtained by Cloak<sup>[3]</sup>, as shown by the solid point. The quite similar phenomena can also be found for the different epilayer thicknesses, substrate doping concentrations and field oxide layer thicknesses based on our analytical model.

FIG. 3 Trade-off Between Breakdown Voltage and On-Resistance as Function of Drift Region Doping Concentration

The careful examination for the optimal condition of the maximum breakdown voltage and lower on-resistance finds an optimal point where the all parameters make the two surface peak fields equal to each other. Thus, utilizing this analysis, the optimal relationship between the silicon film structure

parameters such as the critical doping concentration and silicon film thickness and the field oxide layer thickness for the optimum design can be obtained and some useful conclusions can be drawn.

#### 4 Conclusion

In this paper, the surface field distribution and breakdown voltage of the RESURF LDMOS devices have been studied analytically. The optimum designed condition, at which the ideal electrical field distribution for the maximum breakdown voltage has also been examined. The analytical calculation results are in good agreement with the numerical simulations and experimental data reported, showing the validity of the analytical expression presented here.

#### References

[1] Jose G. Mena and C. A. T. Salama, High-Voltage Multiple-

- Resistivity Drift-Region LDMOS, Solid-State Electronics, 1986, 29: 645.

- [2] J. A. Apples and H. M. J. Vaes, High Voltage Thin Layer Devices, in IEDM Tech. Dig., 1979, 238.

- [3] S. Colak, Effects of Drift Region Parameters on the Static Properties of Power LDMOST, IEEE Trans. Electron Devices, 1981, ED-28: 1455.

- [4] S. Colak, B. Singer and E. H. Stupp, Lateral DMOS Power Transistor Design, IEEE Electron Device Lett., 1980, EDL-1: 51.

- [5] D. Krizaj, G. Charita and S. Amon, A New Analytical Model for Determination of Breakdown Voltage of RESURF Structure, Solid-State Electronics, 1996, 39: 1353.

- [6] Han Seung-Youp, Na Jong-Min, Shin Jin-Cheol et al., An Analytical Model of the Breakdown Voltage and Minimum Epilayer Length for RESURF Diode, Solid-State Electronics, 1996, 39: 1247.

- [7] He Jin, Zhang Xing, Huang Ru and Wang Yanyuan, A Novel Analytical Model for Surface Field Distribution and Optimization of TF SOI RESURF LDMOS Devices, Chinese Journal of Semicoductors, 2001, 22: 402.

- [8] D. Porter and D. S. G. Stirling, Integral Equations, Cambridge University Press, 1990.

- [9] MEDICI. 2.0., Technology Modeling Associations, Inc., 1997.

# RESURF LDMOS 功率器件表面场分布和击穿电压的解析模型\*

#### 何 进 张 兴

(北京大学微电子学研究所,北京 100871)

摘要:提出了RESURF LDMOS 功率器件的表面电场分布和击穿电压的解析模型.根据二维泊松方程的求解,得到了与器件参数和偏压相关的表面电场和电势分布解析表达式.在此基础上,推出了为获得击穿电压和比导通电阻最好折中的优化条件.该解析结果与半导体器件数值分析工具MEDICI得到的数值分析结果和先前的实验数据基本一致,证明了解析模型的适用性.

关键词: RESURF 原理; LDMOS 功率器件; 表面场分布; 击穿电压; 比导通电阻; 优化设计

EEACC: 21560R; 2560B

中图分类号: TN 386 文献标识码: A 文章编号: 0253-4177(2001)09-1102-05

<sup>\*</sup> 国家基础研究资助项目(合同号: G2000365).

何 进 男,博士后,目前研究方向为深亚微米 MOS 器件、功率 MOS 器件、深亚微米 MOS 新结构的设计和表征等.

张 兴 男, 教授, 博士生导师. 研究方向为深亚微米 MOS 器件、工艺和 ASIC 设计.