Vol 19,No. 3 Mar, 1998

#

裴素华 薛成山

赵善麒

(山东师范大学 济南 250014)

(北京电子新技术研究开发中心 北京 100088)

摘要 本文对镓 镓-硼两种基区的 3DD 202 型晶体管负阻摆幅现象进行了比较和理论分析,证明了基区表面杂质浓度分布对器件发射极-集电极电压负阻特性有较大影响 找到了改善晶体管击穿特性的具体措施

EEACC: 2550B, 2560J

## 1 引言

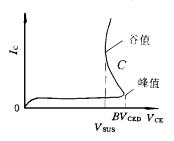

在测试硅大功率晶体管发射结与集电结之间击穿电压BV CEO 时,经常见到有负阻击穿现象发生,如图 1 所示 电压V SUS 称为谷值电压,BV CEO 与 V SUS 之差称为负阻摆幅,用  $\Delta V$  表示 在晶体管的制造中,如何在提高反向击穿电压 BV CEO 的同时,又能使负阻摆幅减到最小,

是长期以来期待解决的问题 本文分别以单质镓和双质镓-硼进行基区扩散,制造出 3DD 202 型的镓管和镓硼管,通过对其负阻特性的测试和理论分析,证明晶体管负阻摆幅的大小主要与基区表面杂质浓度有关,据此也找到了改善晶体管负阻特性的措施

# 2 实验与结果

图 1 晶体管负阻特性

选用电阻率为 40~ 60Ω·cm 的N 型硅单晶作衬底, 在

高浓度磷扩散并减薄抛光后,按下述方法制造两种不同的的基区:采用开管镓扩散技术<sup>[1]</sup>,经过低浓度镓扩散,结深推移,高浓度镓扩散三个阶段形成镓基区; 另经低浓度的镓扩散,结深推移和硼扩散三个阶段形成镓-硼基区 然后,在同一环境下用常规工艺制作出 3DD 202型的镓管和镓-硼管 测试结果表明,镓管的负阻摆幅 Δν 值在 300~500V 之间,而镓-硼管

裴素华 女, 1946 年出生, 副研究员, 主要从事半导体器体与微电子技术的研究工作 薛成山 男, 1945 年出生, 研究员, 主要从事半导体器件与微电子技术的研究工作

赵善麒 男, 1963 年出生, 博士, 高工, 主要从事功率器件与电力电子新技术研究工作

1997-01-16 收到, 1997-03-20 定稿

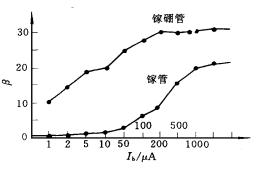

的  $\Delta V$  值小于 100V. 图 2 示出了镓管与镓-硼管 小电流情况下,电流放大系数  $\beta$  随  $I_b$  变化情况,可以明显看出镓-硼管放大性能明显优于镓管 以基极注入  $5\mu$ A 为例,镓管的  $\beta$  值为 0.5~ & 1.2,而镓-硼管的  $\beta$  值却高达 12~ 16; 当基极注入为  $100\mu$ A 时,镓-硼管的  $\beta$  值已经达到器件大电流情况下的放大系数值 (30),但镓管随着  $I_b$  的增加, $\beta$  值虽已增大数 10 倍以上,但还远小于大电流条件下的电流放大系数值

图 2 小电流下镓管与镓硼管放大系数比较

## 3 理论分析

#### 3 1 基区表面杂质浓度分布对电流放大系数的影响

硅内靠近硅表面的杂质,在氧化过程中(本文指磷扩散的再分布过程)要重新分布,这取决于硅-二氧化硅界面上的杂质分凝系数;硅-氧化层中杂质扩散系数的比例;以及氧化速

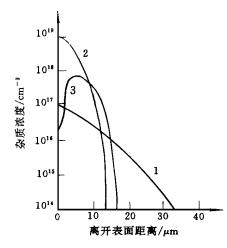

图 3 镓基区重新分布前后杂质浓度分布

- 1、2 重新分布前低浓度、高浓度杂质分布;

- 3 重新分布后基区表面杂质浓度分布

率<sup>[2]</sup>. 图 3 根据实际测量结果给出镓基区重新分布后的表面杂质浓度分布示意图 重新分布后的镓基区表面杂质浓度由原 10<sup>19</sup>/cm³ 降至为 2 × 10<sup>16</sup>/cm³, 且杂质浓度的峰值点离开硅表面约 4μm. 这主要是因为镓在二氧化硅中的扩散系数特别大, 杂质在SiO<sub>2</sub>-Si 界面形成由 Si 指向 SiO<sub>2</sub> 的杂质扩散流, 使硅表面形成耗尽<sup>[1]</sup>. 而硼基区表面无出现其他任何特殊变化, 遵循正常的重新分布规律, 表面浓度由原来 10<sup>19</sup>/cm³ 降至 5 × 10<sup>18</sup>/cm³. 两种基区表面浓度分布存在明显差异, 这种差异直接影响了器件的小电流情况下的增益 在发射极为小电流情况下,晶体管的发射效率表达式:

$$\gamma = \left[1 + \frac{I_{PE}}{I_{PE}} + \frac{I_{RE}}{I_{PE}}\right]^{-1} \tag{1}$$

式中 Іре是注入到发射区的空穴流; Іпе是注入到基

区的电子电流;  $I_{RE}$ 是发射结空间电荷区的复合电流, 其值为  $I_{RE}$  = A  $qX_{me}$   $\times$  R , 其中 A 为 pn 结的结面积;  $_{1}$   $_{1}$   $_{1}$   $_{2}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{5}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{8}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{2}$   $_{1}$   $_{2}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{1}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{1}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{1}$   $_{5}$   $_{5}$   $_{5}$   $_{7}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{5}$   $_{5}$   $_{5}$   $_{7}$   $_{7}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{1}$   $_{2}$   $_{3}$   $_{4}$   $_{5}$   $_{5}$   $_{5}$   $_{5}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7}$   $_{7$

考虑到表面复合后, 基区输运系数  $\beta^*$  的表达式为:

$$\beta^* = 1 - \frac{I_{VR}}{I_{nE}} - \frac{I_{SR}}{I_{nE}}$$

(2)

式中  $I_{VR}$  为体内复合电流;  $I_{SR}$  为表面复合电流 表面复合电流  $I_{SR}=qA_{SS}$   $n_{S}$  其中 S 为表面

复合速度;A s 为基区表面复合有效面积,n s 为表面处的电子浓度,表面复合速度 S 的大小主要与器件表面状态有关 $[^{12}]$ . 由于镓基区的表面浓度较低,在同样的制造环境下,与镓-硼基区相比,抗外界沾污的能力相对减弱,复合速度 S 增大, $I_{SR}$ 增大,由(2)式可知基区输运系数 $\beta$ \*下降 因为晶体管共基极电流放大系数  $\alpha = \mathcal{Y}\beta^*$ ,可见 Ga 基区表面浓度下降会引起器件小电流下,放大系数的明显降低

#### 3.2 电流放大系数对负阻特性的影响

为了进一步研究晶体管负阻特性,给出三极管 C-E 极间的动态电阻表达式[3]

$$r_{\text{CE}} = \frac{\left(1 - \omega M\right)^2 - I_{\text{CBO}} M^2 \frac{d\omega}{dI_C}}{I_{\text{CBO}} \times \frac{dM}{dV_{\text{CE}}}}$$

(3)

式中  $\alpha$  为晶体管共基极电流放大系数;M 为集电结雪崩倍增因子;  $I_{CBO}$  是发射极开路, 集电极-基极间的反向漏电流 显然(3) 式中的分母  $I_{CBO}$  ×  $\frac{dM}{dV_{CE}}$  总是大于零的正数, 但分子式的值却随着  $I_{CE}$  与  $\alpha$  之间变化规律而发生变化, 引起动态电阻  $I_{CE}$  值符号的改变

当  $I_c$  的值较小时,  $\alpha$  随  $I_c$  的增大而增大, 所以  $d\alpha \sqrt{dI_c} > 0$ , 在  $V_{CE}$  达到  $BV_{CEO}$  时, 倍增因子M 明显增大, 使得  $(1-\alpha M)^2$  减小, 而  $I_{CBO} \times M^2 \frac{dM}{dV_{CE}}$  增加, 当M 增加到一定程度, 分子式  $(1-\alpha M)^2 - I_{CBO} M^2 d\alpha \sqrt{dI_c} = 0$ ,  $I_{CEC} = 0$  此时电压发生击穿, 电流急剧上升, 这就是图 1 中的峰值点  $BV_{CEO}$  处

击穿后的  $I_c$  迅速增大, 导致  $\alpha$  明显增加, 分子式 $(1-\alpha M)^2-I_{CBOM}^2$ d $\alpha/dI_{C}<0$ ,  $r_{CE}<0$  即出现负阻特性, 对应着图 1 中的 C 段

当  $I_{\rm C}$  再增加时,  $\alpha$  随  $I_{\rm C}$  的变化减慢,  $d\alpha/dI_{\rm C}$  逐渐减小, 再次使子式的值为零,  $r_{\rm CE}=0$ , 电压出现谷值 $V_{\rm SUS}$

$V_{\rm CE}$ 降至 $V_{\rm SUS}$ 后,  $\alpha$ 随着  $I_{\rm C}$  增加,  $d\alpha/dI_{\rm c}<0$ , 所以  $r_{\rm CE}>0$ , 故  $I_{\rm c}$  随  $V_{\rm CE}$  的增加而增大, 出现谷值后的真正击穿.

利用雪崩击穿的经验公式,推导出蜂值点,谷值点的击穿电压BV ceo、V sus表达式如下:

$$BV_{CEO} = BV_{CEO} \times [1 - \alpha - (I_{CEO} (d\alpha/dI_c))^{1/2}]^{1/n}$$

(4)

$$V_{SUS} = BV_{CBO} \times (1 - \alpha)^{1/n}$$

(5)

从而得到负阻摆幅 ΔV 的表达式:

$\Delta V = BV_{CBO} - V_{SUS} = BV_{CBO} \times \{[1 - \alpha - (I_{CBO}(d\alpha/dI_c))^{1/2}]^{1/n} - (1 - \alpha)^{1/n}\}$  (6) 式中 n 是常数; 对于  $p^+$  n 结, n=4 由 (6) 式可见  $\Delta V$  值的大小取决于  $\alpha$  随  $I_c$  变化率 小电流下若  $\alpha$  随  $I_c$  变化程度不明显,即  $d\alpha/dI_c$  0,故  $I_{CBO}(d\alpha/dI_c)$  0, $\Delta V$  0 即  $V_{SUS}$   $BV_{CBO}$ ,器件的负阻特性不明显;相反若  $\alpha$  随  $I_c$  变化显著,则  $\Delta V$  值就变大 实质上, $\alpha$  随  $I_c$  变化程度明显与否,直接反映了器件在小电流情况下,放大性能的优劣,这与图 2 的测试结果相吻合,如镓-硼管,小电流下放大性能较好,负阻摆幅较小,相反镓管的负阻摆幅较大

# 4 结论

通过对镓、镓-硼基区表面杂质浓度分布的研究和实验证明、说明了基区表面杂质浓度

过低,将使器件小电流下的放大性能变坏,进而导致发射极-集电极击穿后负阻摆幅增大 在 利用开管镓扩散技术提高器件反压水平改善电流特性时,要在基区表面进行补充扩硼工艺, 以改善晶体管的放大性能和负阻特性

#### 参 考 文 献

- [1] 刘秀喜, 采用 SiO 2-Si 系扩镓提高扩散质量和器件性能的研究, 半导体学报, 1995, 16(3): 235~ 240

- [2] 粱鹿孝, 半导体器件表面氧化技术, 北京 科技出版社, 1979, 36

- [3] 张屏英,等,晶体管原理,上海 科技出版社,1985,68~80

# Influence of Surface Impurity Profiles on Characteristics of Negative Resistance of Transistor

Pei Suhua and Xue Chengshan

(Institute of Semiconductors, Shandong Nomal University, Jinan 250014)

#### Zhao Shanqi

(Beijing Power Electronics R & D Center, Beijing 100088)

Received 16 January 1997, revised manuscript received 20 M arch 1997

**Abstract** The characteristics of negative resistance of 3DD 202 transistors have been studied. For comparison, two kinds of base region are formed by Ga or Ga-B, respectively. It has been found that the negative resistance characteristic is strongly affected by the surface impurity profiles in the base region. A method to improve the reverse breakdown voltage is reported

**EEACC**: 2550B, 2560J