CHINESE JOURNAL OF SEM ICONDUCTORS

Vol 20,No. 6 June, 1999

## VLSI 3-维容错结构及其成品率分析\*

## 赵天绪 郝 跃 许冬岗

(西安电子科技大学微电子所 西安 710071)

摘要 本文研究VLSI 电路的NPIRA 结构及其成品率,分析间隙冗余阵列的(s, 8)类结构,提出最优的(s, 8)间隙冗余阵列的定义,同时给出了最优的(s, 8)间隙冗余的成品率的下界表示

**EEACC**: 0170E, 2570

## 1 引言

随着VLSI技术的进步,系统集成(System on a chip)迅速发展,随之其芯片面积增加,甚至发展为圆片系统集成(WSI). 然而,大面积VLSI芯片对由制造缺陷而引起的故障是非常敏感的 为了可行的成品率,必须设计具有一定容错能力的结构,而且所使用的机理必须是高效的,以便容错结构不因电路面积增大,重构互连线更长而降低系统的性能

芯片级的容错结构已成功地用来提高高密度的半导体器件的成品率, 如存储器、CPU、以及门阵列、PLA 等<sup>[1,2]</sup>. 由于规则的结构适合于对备用单元的有效利用, 许多研究已经对并行处理的处理单元(PE)的规则阵列的容错设计进行了研究 在实际的VLSI阵列中, 包含了已经出现故障的单元, 随着对大面积VLSI工艺制造的可能, 为了产生一个无故障(逻辑上的)的, 期望的互连线拓扑结构的阵列, 对含有故障的实际阵列进行容错设计是非常必要的 容错设计策略的目标是通过应用尽可能多的, 好的处理单元来实现大面积的有效性, 从而保证不会因为容错设计结构中的处理单元之间的互连线太长而降低了电路的性能

容错可以通过在系统中的结构冗余或时间冗余来实现 结构冗余需要一些硬件支持, 而时间冗余往往降低系统的性能 对于一个系统而言, 系统的性能常常是一个重要因素, 在 VLSI技术中硬件的成本比较低 故本文将重点讨论 VLSI 阵列的结构冗余问题

结构冗余涉及到一些冗余单元和相应的互连结构 在阵列结构中, 只要没有故障出现, 冗余单元就处于闲置状态: 只有当有故障单元出现而必须替换时, 冗余单元才开始运行.

目前, 几乎提出的所有的容错结构设计方案都局限于 2-维结构[3-5]. 在这些结构中, 很难保证在重构之后连线最短且又简单 进入八十年代以来, 随着绝缘层上的硅(SOI)等 3-维

#### \* 国防科技预研基金支持研究

赵天绪 男, 1964年出生, 博士研究生, 从事VLSI 容错结构设计和成品率分析研究

郝 跃 男, 1958 年出生, 教授, 博士生导师, 从事 IC 可制造性理论与方法, 统计最优化和统计模型, IC 制造动力学 理论与方法以及专用电路集成与系统集成技术与方法的研究

许冬岗 男, 1974 年出生, 硕士研究生, 从事深亚微米新型器件结构与 VLSI 可靠性研究

1998-01-16 收到, 1998-04-16 定稿

集成电路技术的发展, VL SI 开始由平面 (2-维) 进入立体 (3-维) 集成 这不仅提高了芯片的集成度, 同时也可使容错设计的有效性大为增加 本文对三维的容错设计结构进行了系统的研究 由于第三维的应用, 一个备用单元可以替换与之相邻的八个单元中的任何一个, 这显然是对二维结构的一个明显改善三维容错技术是 VL SI 发展的产物, 也是基于三维集成电路技术发展的必然结果

## 2 3-维阵列中的间隙冗余

所选择的 3-维阵列不仅具有支持许多重要的并行算法的能力, 而且能容易地嵌入到其他许多有用的非平面拓扑结构中去 本文提出的基本冗余方法确实具有应用到其他规则阵列结构的潜在能力 我们将主要考虑对规则结构的冗余设计

定义 1 空间(或非平面)间隙冗余阵列是一个有备用处理单元的规则计算阵列,备用单元位于阵列的间隙中,每一个备用单元可以替代距它最近的那些基本单元中的任何一个

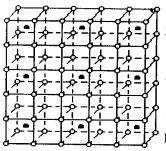

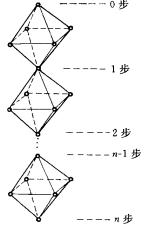

图 1 是一个非平面的间隙冗余阵列 (N P IRA ). N P IRA 结构可以并入不同级别的备用单元,这不仅取决于有多少个空间间隙用来放置备用单元而且还取决于每一个间隙放置多少个备用单元

定义 2 一个NPIRA 的冗余率是空间间隙冗余阵列中的备用处理单元数与计算阵列中基本处理单元数的比值 简记为RR.

图 1 表示的计算阵列中共有 72 个基本处理单元, 有 9 个备用单元 因此, RR 为 12.5%.

图 1 (1,8) NP IRA,

RR 为 12.5% 定义 3 一个 (s,p) 空间间隙冗余阵列是有备用处理单元和连线的一种阵列结构,它使得: (1) 每一个基本单元可以由 s 个备用单元中的任何一个去代替; (2) 除了阵列边界上的备用单元外,每一个冗余单元恰好可以替代 p 个基本单元 (s,p) 均为正整数).

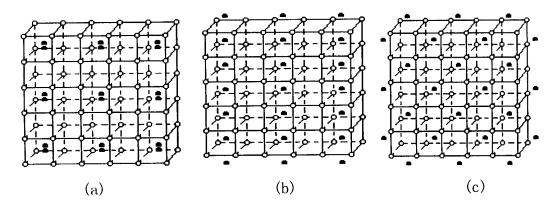

从定义 3 可看出,图 1 是一个(1,8) 间隙冗余阵列结构,而图 2 是 3 个不同结构的(2,8) 间隙冗余阵列 在图 2 的每一种情形中,每一个基本单元可由 2 个(s) 备用单元去替代,而且每一个备用单元可以替代 8 个(p) 基本单元中的任何一个. 阵列的边界备用单元可能连结少于 8 个基本单元,如图 2(c).

下面集中对计算阵列的NPIRA 的结构进行讨论 因为在这样的结构中, 位于间隙中的每一个备用单元总与 8 个基本单元相邻相连结(除了边界上的某些单元外(参考图 1 和图 2). 这就构成了 3-维间隙冗余阵列的(s, 8)类

在图 2 中, 从系统的成品率或者可靠性方面来说, 这 3 个 (2,8) 间隙冗余阵列结构是不等价的 特别地, 在这 3 个 (2,8) 间隙冗余阵列结构中, 每一个基本单元可以和两个备用单元相连结 而对于一个  $2 \times 2 \times 2$  子阵列块中, 有不同个数的备用单元与之相连结 容易看出, 图 2(c) 中阵列结构是最稳定的, 这是因为在图 2(c) 中的任何两个相邻的基本单元共享一个或两个备用单元, 而图 2(a) 和 (b) 中的某些两个相邻单元没有可共享的备用单元 同时, 图 2(c) 中的每 8 个相邻的基本单元至少可以连结 4 个不同的备用单元, 而对于图 2 中的 (a) 和

图 2 (a) (2,8) NPIRA, RR 为 6/24; (b) (2,8) NPIRA, RR 为 6/24; (c) (2,8) NPIRA,RR 为 8/24

(b) 分别为 2 个和 3 个, 这进一步说明图 2(c) 在进行冗余替代时具有最大的灵活性 通过对 (s, 8) N P IRA 结构的研究, 对于任何相邻的 4 个基本单元有下述定理:

定理 1 在任何(s, 8) 的 N P IRA 中, 存在 4 个相邻的基本处理单元至少共享 $\left[\frac{s}{2}\right]$ 个备 用单元

证明: 假设在一个(s, 8)间隙冗余阵列中,不存在 4 个相邻基本单元至少共享 $\left[\frac{s}{2}\right]$ 个备

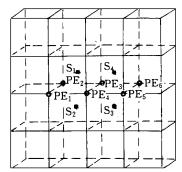

用单元 在图 3 中, 由假定不妨设基本单元 PE1, PE2, PE3, PE4 及 PE3, PE4, PE5, PE6 所共 享的备用单元数严格地小于[ $\frac{1}{2}$ ]个, 那么对于备用位置  $S_1$  和  $S_2$  而言, 处于位置  $S_1$  和  $S_2$  的备用单元数总和为  $\left[\frac{s}{2}\right]$  - 1 个或 者更少个. 同样的讨论, 对于备用位置 S3 和 S4 而言, 处于位 置  $S_3$  和  $S_4$  的备用单元数总和也为 $\left[\frac{s}{2}\right]$ - 1 个或者更少个. 因 此,  $PE_3$  和  $PE_4$  分别最多可以和  $2\left[\frac{1}{2}\right]$  - 2 个备用单元相连 结, 而 2[5]- 2 严格地小于数 s 这是矛盾的, 因为这个结构 是一个(s, 8)的间隙冗余阵列 因此,存在4个相邻的基本单

元共享[六]个或者更多的备用单元

图 3 基本规则NPIRA 备用单元未标出

定理 1 表明, 在任何(s, 8)的间隙冗余阵列中, 一定存在 4 个相邻的基本处理单元可以 共享至少 $\left[\frac{s}{2}\right]$ 个备用单元 因此,给出了最优的 $\left(s,8\right)$ 间隙冗余阵列的定义

定义 4 一个最优的 (s, 8) 间隙冗余阵列的结构是: 它的任何 4 个相邻的基本单元最多 共享[출]个备用单元

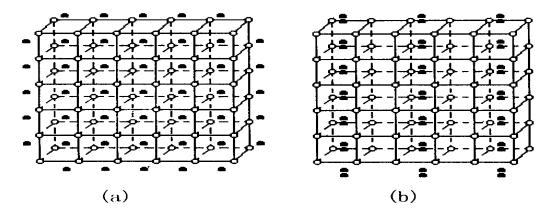

定义 4 表明, 一个最优的(s, 8) 间隙冗余阵列实际上是它的任何 4 个相邻的基本单元所 共享备用单元数不会多于[ $\frac{s}{2}$ ]个. 图 1, 图 2 中的(c) 和图 4 中的(a) 分别是最优 (1, 8), (2, 8) 和 (4,8) 间隙冗余阵列结构

图 4 (a) (4,8) NPIRA, RR 为 7/12; (b) NPIRA, RR 为 8/12

## 3 VLSI芯片成品率的估计

本节中, 我们将通过对芯片成品率的估计来反映NPIRA 的容错能力的有效性 VLSI成品率是按照对单个处理单元的成品率来估计的, 将做如下的假定:

- (1) 所有处理单元,包括备用单元,都有相同的生存概率(即每个单元的成品率),而且处理单元之间的失效是相互独立的;

- (2) 开关和互连线是无故障的, 这就隐含了一个失效的基本单元总可以用一个与之相连的无故障的备用单元来替代:

- (3) 开关和互连线所占据的面积与 PE 的面积相比是可以忽略的, 因此整个 VL SI 阵列的面积就等于 PE (包括基本处理单元和备用单元) 面积的和

在以上的假设下来估计最优NPIRA(s, 8)类的成品率

#### 3 1 最优的(1,8)NPIRA

对于最优的(1,8)N P IRA 的成品率的估计(图 1 所示),可以按照单个处理单元的成品率直接进行。假设p 是每一个处理单元的成品率,那么图 1 中任何一团的成品率是在八个基本单元和一个备用单元中最多有一个失效的概率。这个概率公式由下式给出:

$$p^{9} + C_{9}^{1}(1 - p)p^{8} = p^{9} + 9p^{8}(1 - p)$$

其中  $C_m^n = \frac{m!}{n! (m-n)!}$ ,以下相同

对于一个  $2 \times n \times n$  的非平面阵列共有  $(2 \times n \times n)/8 = n^2/4$  个这样的团, 那么整个阵列的成品率 Y(1,8) 为

$$Y(1, 8) = [p^9 + 9p^8(1 - p)]^{n^2/4}$$

如果图 1 中没有加进备用单元, 它的任何一团的成品率为  $p^8$ , 而一个  $2 \times n \times n$  阵列的成品率为  $(p^8)^{n^2/4} = p^{2n^2}$ . 由于

$$p^9 + 9p^8(1 - p) > p^8$$

则有 $[p^9+9p^8(1-p)]^{n^2/4}>(p^8)^{n_2/4}=p^{2n^2}$ 成立 从此式显然可以看出, 有备用单元的阵列的成品率比没有备用单元的阵列要高

#### 3 2 最优的(2,8)间隙冗余阵列

对于更高级(s>1) 的冗余最优 N P IRA 结构来说, 要求得准确的成品率解析式是相当困难的 如图 2(c), 这主要是因为所有的备用单元之间是相关的 我们通过对比较容易分析的次优 (2,8) N P IRA 结构(图 2(b)) 分析来给出最优的(2,8) N P IRA 结构(图 2(c)) 的成品率下界

为了估计冗余阵列图 2(b) 的成品率, 我们把图 2(b) 的结构分解成如图 5 所示的 n/2 个相同的块 由于这些块之间彼此没有共享备用单元, 因此它们的成品率可以独立地计算, 而

且可以通过分析一个块就可以得到整个阵列的成品率 为此,我们需作出如下假定:假定备用单元只与本块内的基本单元相连结;从图 5 的顶层开始,无论什么时候需要,上面的备用单元都可以替代它下面的故障基本单元;只有当由于备用单元失效不能用时或者已经替换了其他基本单元时,下面的备用单元才可以替代它上面的故障基本单元

替换过程的每一步都标在图 5 上 替换过程的成功可分为下面三个状态:

状态 1: 有可用的备用单元;

状态 2: 无可用的备用单元;

状态 3: 由于代替故障单元的失效而使整个块失效

设 $p^{(k)}$  表示第k 步替代过程处在状态i 的概率 在0 步,没有替代发生、因此

图 5 从图 2(b) 中分解 出的一个冗余块

$$p_1^{(0)} = p$$

$p_2^{(0)} = (1 - p)$

$p_3^{(0)} = 0$

设 $p_{ij}$ 表示从状态i 转移到状态j 的一步转移概率,那么 $p_{11}$ 表示从一个有可用备用单元状态转移到下一步同一状态的概率 这要求在下一步备用单元是无故障的,而且在两个备用单元之间的四个基本单元中最多只有一个出现故障,因此

$$p_{11} = p \{ p^4 + C_4^1 p^3 (1 - p) \} = p^5 + 4p^4 (1 - p)$$

类似地, p12表示从一个有可用备用单元状态转移到下一步无可用备用单元状态的概率, 这要求下一步没有可用备用单元 这样, 要么下一步的备用单元本身就是故障单元, 要么下一步的备用单元和它上面的四个基本单元恰好有一个是故障单元 因此

$$p_{12} = p^4 (1 - p) + C_{5p}^2 (1 - p)^2 = p^4 (1 - p) + 10p^3 (1 - p)^2$$

*p* 13表示从一个有可用备用单元的状态转移到整块失效 此时,下一步的备用单元可能是可用的也可能是不可用的 在可用的情况下,它上面的四个基本单元中至少应该有两个以上的故障单元,才能使整个块失效;在不可用的情况下,它上面的四个基本单元中至少应该出现两个故障单元,才能使整个块失效 因此

$$p_{13} = pC_{4}^{1}p(1-p)^{3} + p(1-p)^{4} + (1-p)C_{4}^{2}p^{2}(1-p)^{2}$$

$$+ (1-p)C_{4}^{1}p(1-p)^{3} + (1-p)^{5}$$

$$= 10p^{2}(1-p)^{3} + 5p(1-p)^{4} + (1-p)^{5}$$

类似地可以得到

$$p_{21} = p^{5}$$

$$p_{22} = 5p^{4}(1 - p)$$

$$p_{23} = (1 - p)^{5} + 5p(1 - p)^{4} + 10p^{2}(1 - p)^{3} + 10p^{3}(1 - p)^{2}$$

一旦这个块失效, 在后面的替代过程中是不可能恢复的 因此

$$p_{31} = 0$$

$p_{32} = 0$

$p_{33} = 1$

基于上面的表述, 在替代过程中的每一步可以表示为具有一步转移概率矩阵

$$T = \begin{bmatrix} p_{11} & p_{12} & p_{13} \\ p_{21} & p_{22} & p_{23} \\ p_{31} & p_{32} & p_{33} \end{bmatrix}$$

和初始状态概率向量

$$P^{(0)} = (p_1^{(0)}, p_2^{(0)}, p_3^{(0)})$$

的M arkov 链, 那么 n 步后状态概率由

$$(p_1^{(n)}, p_2^{(n)}, p_3^{(n)}) = (p_1^{(0)}, p_2^{(0)}, P_3^{(0)}) \times \begin{bmatrix} p_{11} & p_{12} & p_{13} \\ p_{21} & p_{22} & p_{23} \\ p_{31} & p_{32} & p_{33} \end{bmatrix}^n$$

给出 整块在替代过程中的第 n 步或者第 n 步以前失效的概率为 p  $\mathfrak{P}^n$ . 因此, 整块的成品率为(1- p  $\mathfrak{P}^n$ ). 由于一个  $2 \times n \times n$  的非平面阵列共有 n/2 个这样的块, 那么整个阵列的成品率为

$$Y(2, 8) = (1 - p_3^{(n)})^{n/2}$$

由于我们已经分析了(2,8) NPIRA 的次优结构,正如前面所述,这个表达式提供了最优的(2,8) NPIRA 的成品率的下界

#### 3 3 最优的(s, 8) NP IRA (s> 2)

当 s > 2 时, 对最优的 (s, 8) N P  $\mathbb{R}$ A 的成品率估计, 和第 2 种情形一样, 通过对次优的 (s, 8) N P  $\mathbb{R}$ A 的成品率分析, 同样可以给出最优的 (s, 8) N P  $\mathbb{R}$ A 的成品率的下界

基于 SO I 技术的三维集成电路正在发展, VL S I 制造将进入从二维到三维的时代 随着器件尺寸的缩小, SO I 结构是 IC 未来的发展方向, 尤其是目前 S M O X 工艺的日趋成熟和 Sm art Cut(灵巧切削) 技术的突破, 三维集成电路将得到更快发展 但是由于三维电路工艺复杂, 单元失效较二维集成显著增加, 这就使得容错设计在三维集成中占据了重要地位 因此, 容错设计是提高三维集成电路成品率的重要措施之一. 文中提出的容错设计方法可以在 SO I 结构中得到实现.

## 4 结论

本文从理论上对三维集成电路的容错结构进行了系统地分析,提出了最优的(s, 8) N P IRA 的概念,估计了最优的(s, 8) N P IRA 成品率并给出了其下界

#### 参 考 文 献

- [1] R. T. Smith et al., IEEE J. Solid-State Circuits, 1981, 16(5): 506~513

- [2] T. M ano et al., IEEE J. Solid-State Circuits, 1982, 17(8): 726~730

- [3] S Dutt and J. P. Hayes, IEEE Trans Computers, 1990, 39(4): 490~503

- [4] S. Dutt and J. P. Hayes, IEEE Trans Computers, 1992, 41(5): 588~ 598

- [5] A. D. Singh, IEEE Trans Computers, 1988, 37(11): 1398~ 1410

# Three-D Fault-Tolerant Structure and Y ield Analysis of VLSIC ircuit

Zhao Tianxu, Hao Yue, Xu Donggang

(M icroelectronics Institute of X id ian University, X i 'an 710071)

Received 16 January 1998, revised manuscript received 16 April 1998

**Abstract** The NPRA structure of the VLSI circuit and yield are discussed, the definition of an optimal (s, 8) NPRA 's is presented by the class of (s, 8) structure analysis of the interstitial redundant array. A lower bound to the optimal (s, 8) interstitial redundant array yield is discussed and given

**EEACC**: 0170E, 2570