Vol. 27 No. 1 Jan. .2006

# 适用于 1000 Base- T 以太网的低抖动 低功耗频率综合器

# 陆 平 王 彦 郑增钰 任俊彦

(复旦大学专用集成电路与系统国家重点实验室,上海 200433)

摘要:采用高速鉴频鉴相器(TSPC)、经典抗抖动的电荷泵、交叉耦合差分延迟单元以及电阻分压相位内插电路等结构设计了一个应用于 1000Base T 以太网收发器的频率综合器电路,并能兼容 10/100Mbps 模式. 该电路同时满足发送电路上升下降斜率控制和时钟恢复电路对于多相时钟(128 相)的需要,大大节约了面积和功耗. 在晶振的绝对抖动 约为 16ps 情况下,输出 25MHz 测试时钟信号 仅为 11ps. 表明该频率综合器有较强的抑制噪声能力,能很好满足发送和接收电路对于时钟性能的要求. 芯片采用 SMIC 0. 18µm 的标准 CMOS 工艺,电源电压为 1. 8V,功耗小于 4mW.

关键词:以太网;频率综合器;时钟抖动

EEACC: 1205; 1230; 1280

中图分类号: TN492 文献标识码: A 文章编号: 0253-4177(2006)01-0137-06

## 1 引言

本文设计的频率综合器可以为 10/100/1000Base-T 自适应以太网芯片发送和接收电路提供基本时钟信号. 有些设计直接采用 1. 25 GHz 或625MHz 高频时钟发生器[1],这对环振实现不仅增加难度(高频的寄生等问题),而且采用较小尺寸令匹配等性能不易保证. 并且全模拟的时钟数据恢复电路[1,2]对工艺依赖性强,不利于移植. 本设计采用4 路收发器并行收发数据,共用同一个频率综合器(125MHz,与100Base-T兼容),同时引入了动态相位内插单元提供与高频时钟相同的精细相位间隔,并配合数字方法实现 CDR. 不仅简化了设计,增强了可移植性,更保证了时钟信号的优良性能.

应用于 1000Base- T 以太网收发电路的频率综合器由电荷泵型锁相环和数字处理模块构成. 发送电路需要动态选择 8 相且相邻相位间隔为 0. 5ns 的时钟控制 DAC 电流开关实现 4ns 精确的上升下降时间<sup>[3]</sup>. 接收器的数据时钟恢复电路需要从 128 个等相位间隔的时钟动态选择合适的相位. 为了兼容10/100Base- T,VCO 直接设计成 8 级差分结构 16相时钟输出. 因此一个额外的动态低功耗 8 相内插电路应用在电路中以产生冗余相位. 本文中电路不仅能灵活兼容 10/100/1000Mbps 三种模式,并且用动态内插实现更多相位输出. 节约了功耗和面积.

# 2 系统结构

本设计采用 4 路收发器并行收发数据. 数据采 用 ML T3 编码,每个时钟上升沿采样数据可读出 2bit 信息,因此所需最高时钟输出频率为 125M Hz. 与 10/100Base-T 相比 .1000Base-T 以太网收发电 路不仅对时钟相位的要求有所提高,系统时钟输出 方式也发生了较大的变化. 除了算法的改进,主要是 因为 1000Base-T 中存在 MASTER 和 SLAVE 两 种工作模式:在 MASTER 模式下发送和接收(CDR 除外)都采用本地时钟;而在 SLAVE 模式下发送和 接收都采用对方时钟.与10/100Base-T模式下发送 采用本地,接收采用从对方恢复出的时钟情况有所 不同.这意味着在 SLAVE 模式下提供给发送模块 用于控制精确上升下降时间的 8 相时钟不能再采用 固定相位[3],而必须全部像接收时钟一样动态恢复. 在 MASTER 模式下接收电路 ADC 和 CDR 所需的 时钟也不一致,前者需要一固定相位时钟,后者需要 动态恢复.

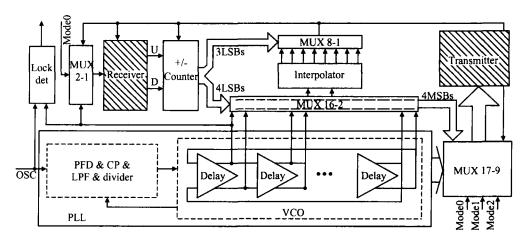

图 1 为千兆以太网频率综合器单路收发器系统框图. 阴影框分别为发送和接收模块,其余部分构成整个频率综合器模块,包括核心电路锁相环、相位内插电路、计数器、四个多路选择器. 除了晶振输入信号,还需要模式选择输入信号 mode2~mode0(000/001:10M/自动协商;010:100M;100:1000M MAS-

TER;101:1000M SLAVE)和接收模块对时钟相位 的判决输入信号 U 和 D.

图 1 频率综合器系统框图

Fig. 1 Block diagram of frequency synthesizer

为便于给发送电路提供固定时钟,也为了兼容 10/100Base T, VCO 设计成 8 级差分 16 相时钟输 出.由于 0.5ns 的相位间隔不足以达到千兆均衡算 法的最佳效果,该16相时钟须通过一个16选2的 多路器(粗选)选择两个相邻时钟送入内插电路,用 以在相邻相位之间均匀产生 8 相内插时钟, 接收器 所需要的动态恢复时钟就从这8个精细相位中选出 (细选). 相位选择信号来自于接收器数字鉴相输出 控制的 7bit 累加器 (U 有效) 或减法器 (D 有效) 输 出:高4位用干粗选,低3位用干细选,同时因为 MASTER 模式下 ADC 需要固定相位时钟,需要一 个 2 选 1 的多路器通过模式选择信号决定送入恢复 的动态时钟还是固定时钟. 对发送器来说, 0. 5ns 的 相位间隔已经足够,因此8相边沿控制时钟可直接 来源于 VCO 的输出. 但正如前面所述,这些时钟在 SLAVE 模式下不再是固定的,不能直接从锁相环 中抽取某些相位,而是必须如接收时钟一样用数字 鉴相信号控制相位移动的方向,从而选出同步的主 时钟和与之对应的连续8个相位的边沿控制时钟.

时钟由关键模块 PLL 产生. 鉴相器对输入的 25MHz 的晶振参考时钟和 VCO 分频后得到的反馈信号进行比较,通过电荷泵、滤波器产生控制电压调节 VCO 的振荡频率,经过反馈后与晶振时钟继续相位比较. 100/1000Mbps 模式需要 125MHz 的时钟,反馈回路采用 5 分频器;10Mbps 模式下则需要 80MHz 时钟采样 ROM,分频系数为 16/5.

# 3 频率综合器电路设计

#### 3.1 鉴频鉴相器和电荷泵

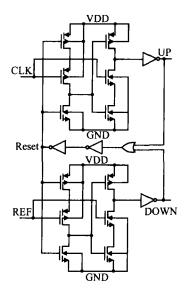

本文采用 TSPC 结构 D 触发器实现鉴频鉴相

器<sup>[4,5]</sup>,如图 2 所示. TSPC 是 C<sup>2</sup> MOS 锁存器的一种简化结构. 它在主从触发器之间用相同相位的时钟来控制,不存在时钟交叠,因此在很高的工作频率下也能够保证 D 触发器的正常工作<sup>[6]</sup>. 另外该结构管子数目比较少,内部电容和延迟都很小,工作速度很快,所以这种结构更适宜应用在高频锁相环当中.

图 2 鉴频鉴相器电路

Fig. 2 Phase and frequency detector

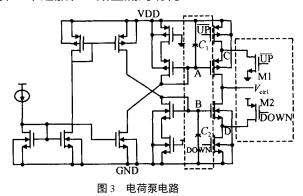

\_\_\_ 图 3 为电荷泵电路示意图. 电荷泵的开关(用UP和 DOWN 控制) 放置在电流镜的外侧,由于上下两路电流镜的控制栅 A 和 B 的电压是相对稳定的,不会把开关的转换过程通过电荷的注入效应耦合到 Vetrl上. 同时 C 和 D 节点的电压由于是跨过电流源与控制电压 Vetrl连接,也有隔离作用,有利于减小控制电压的纹波效应. 这种电荷泵更简单,并可以

省掉1个运放和2路直流的功耗.

Fig. 3 Charge pump circuit

当开关打开,C点电压被拉到  $V_{DD}$ 的时候,由于寄生电容的存在,A 点电压也有一个较小的波动,将会影响到电流镜中的电流值的稳定. B 点和 D 点也有类似情况. 为了稳定 A 和 B 点电压,增加了 2 个 MOS 管电容<sup>[7]</sup>,可以有效稳定 A、B 节点电压. 此外,电路加入两个 MOS 管 M1 和 M2 吸放多余电荷,使漏电流时间更短. 但这样使得 C、D 节点电压波动变大,从而影响 A、B 的电压. 为了更好地稳定控制电压,减小时钟抖动,两个因素应权衡考虑.

电荷泵的充放电电流  $I_{\varphi}$ 是环路带宽、阻尼系数等参数的决定因素之一. 本设计电荷泵采用带隙基准源提供的基准电流,随温度、工艺及电源波动 (PV T) 的变化很小(从 SS @125 ~ FF @ 变化 0. 15 %). 一定程度上稳定了系统的性能.

#### 3.2 压控振荡器

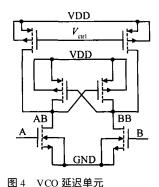

电路采用交叉耦合形式延迟单元构成的压控振荡器(VCO)<sup>[5]</sup>,如图 4 所示. 由控制电压 Verl偏置的两个 PMOS 实现压控输出频率. rail-rail 的输出使压控管的工作范围基本上在线性和饱和之间变化,造成整个 swing 范围内负载的非线性变化. 非线性负载管虽然易于引入电源共模噪声,但对固定频率输出,大的摆幅会提高压摆率,从而减少了噪声对边沿敏感处(整形电路的阈值转换电平)的污染机会. 同时,用两个交叉耦合对管能进一步提高信号边沿的转换速率,改善噪声性能. 而且版图设计也考虑了电源的净化.

对于好的时钟输出,占空比应该为 50 %,特别是对于一些应用下降沿时序的电路(例如 pipeline ADC),精确的占空比更是性能的保证.从延迟单元送出的时钟并非完美的方波,占空比也需要调整.本文应用了一个简单的利用多相位输入的占空比整形电路,电路采用两组完全相同的传输门和倒相器<sup>[5]</sup>.由于 AB 和 BB 是差分输出,具有 180 \*相移.从 AB 上升沿达到阈值为 CL K \_ OU T 充电开始,半个周期以后 BB 开启,下半电路放电,形成对称的下降沿.

Fig. 4 Delay cell of VCO

#### 3.3 相位内插电路

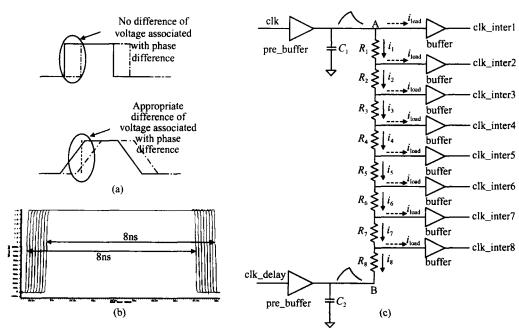

相位内插有电流内插和电压内插两种实现方法.基于本文的 VCO 结构和低功耗的要求,采用电压内插<sup>[8]</sup>.相位内插与一般的直流电压内插的本质不同在于前者是时域上变化的,而后者在任意时刻都有相同的结果(只要输入电平没有变化).关键是将时域上变化的相位内插输入转换成类似静态的电压内插的输入.时钟的转换要求一般速率为纳秒级甚至更小,在这么短的时间内完成电压内插是很难做到的.所以,首要的步骤是用较大的电容负载将需要内差的两个时钟沿拉得较为平缓,至少让超前相位时钟沿的高电平转折点超前于相位滞后时钟沿的低电平转折点,如图 5(a) 所示.

由于时钟相位内插的输出结果还要作为各后续 模块的时钟使用,因此必须将变小的 slew rate 整形 回来,成为好的方波信号,这意味着每个需要输出的 节点必将接一个方波整形的缓冲级,就是一个电容 负载, 电容负载对于直流电平内插没有影响,但是时 钟沿即使再缓慢也是随时间变化的量,即 dv/dt $0. \text{ m d} v / \text{d} t = i_{load} / c$ ,可以根据 slew rate 的值和负载 电容值计算出内插过程中注入负载中的电流.这个 电流虽小,在整个内插中却是一个非常重要的因素, 它决定了电阻取值的变化趋势和内插相位的均匀程 度. 如图 5(c) 所示,输入的时钟沿斜率近似相等,考 虑到匹配要求输出 buffer 的尺寸也完全相同 ,即 c相等,因此各个支路的  $i_{load}$  相等. 由图可知  $i_1 = i_2 + i_3 + i_4 = i_4 + i_5$  $i_{\text{load}} = i_3 + 2i_{\text{load}} = \dots = i_8 + 7i_{\text{load}}$ ,而均匀相位内插 要求均匀电压内插,即  $V = i_1 R_1 = i_2 R_2 = ... =$  $i_8 R_8$ , 所以  $R_1 < R_2 < \dots < R_8$ . 这就是应用在相位 内插时分压电阻不能像普通的电压内插一样均等取 值的原因. 根据该方法计算得到的非均匀电阻串应 用在内插电路中的效果如图 5(b) 所示.

如果精度要求不高,例如时钟恢复中的相位选择,分压电阻可以按照上面的方法粗略取值,由后仿真得到均匀的结果,如果要求稍高,则电阻的取值须经仔细计算,并考虑寄生效应,从上面的分析可以看

图 5 相位内插原理及电路示意 (a) 相位差转换成可内插的电压差; (b) 相位内插结果; (c) 相位内插电路示意 Fig. 5 Principle and circuit of phase interpolation (a) Conversion from phase error to voltage error; (b) Phase interpolation; (c) Circuit of interpolator

出,若采用动态内插,为了保证两个输入时钟具有相同的压摆率, $C_1$  和  $C_2$  的值必不相同。考虑上升沿,两个输入时钟经过 buffer 后分别对图 5(c) 中 A、B 两点充电。假设 pre \_ buffer 的平均充电电流为  $I_{buffer}$ ,且输出 buffer 的负载电容为  $G_{load}$ (这些值可通过仿真精确得到)。首先定一个电容值  $G_1$ ,并令输出缓沿时钟上升沿斜率为 dv/dt=a,可以得到  $Ic_1=aC_1$ , $I_{load}=aG_{load}$ 那么:

$$I_{R_1} = I_{\text{buffer}} - I_{C_1} - I_{\text{load}}$$

(1)

对于内插得到的相邻时钟,相位间隔为 2/128,转换为时间间隔即 8ns/128 = 62. 5ps. 所以内插所得的电压差应为:

$$V = a \times 62.5 ps \tag{2}$$

可得内插电阻值依次为:

$$R_1 = V/I_{R_1} = V/(I_{\text{buffer}} - I_{C_1} - I_{\text{load}})$$

$R_2 = V/I_{R_2} = V/(I_{\text{buffer}} - I_{C_1} - 2I_{\text{load}})$

$R_8=V/I_{R_8}=V/\left(I_{\mathrm{buffer}}-I_{C_1}-8\,I_{\mathrm{load}}\right)$  (3)已知  $I_{C_2}=I_{\mathrm{buffer}}+I_{R_8}$ ,所以  $C_2=I_{C_2}/a=\left(I_{\mathrm{buffer}}+I_{R_8}\right)/a>C_1$  .

由分析可知,在得到相同沿斜率的前提下, Ibuffer 电流的大小直接决定了电阻串的绝对值大小. 太小的电阻值在实际中难以做到精确,与设计目标的稍稍偏离可能导致 V 较大的变化,实际中往往取 k 单位. 在完成的版图中,可能有各种寄生存在,影响到已经确定的电流和电阻电容值,因此版图参数提

取的后仿真也是必要的.

#### 3.4 数字部分

数字部分包括一个 7bit 计数器、4 个多路选择器以及一个锁定检测电路(lock \_ det). 计数器用动态时钟同步,采用格雷编码. 当接收鉴相输出 UP 时,正向计数,时钟相位向前调节一相;当接收鉴相输出 DN时,反向计数,时钟相位向后调节一相. 这里相邻相位间隔是时钟周期的 1/128,是计数器输出的高 4 位选出的相邻两相锁相环输出,均匀内插出 8 相后,再由低 3 位经一个 8-1 多路器选择合适的相位. 因为发送电路需要的时钟只是在 16 相锁相环输出时钟之中选取,故多路器只用计数器的高 4 位控制变化方向即可,同时还需要模式选择信号作为使能决定在哪种模式下需要动态选择时钟输出.

锁定检测电路是额外一个功能模块,目的是检测锁相环的锁定状态,并将指示信号送给接收器数字部分,"通知"其是否可以开始工作,其工作原理如图 6 所示. 电路内部主要仍是由计数器构成,晶振参考时钟经过分频后作为使能信号:高电平有效,使计数器计数;低电平复位,并锁存计数结果. VCO 的输出作为计数时钟. 每次使能无效(低电平)时将锁存结果并与预定值比较,结果一致则说明已经锁定,送出"1";反之,送出"0".

图 6 锁定检测电路示意 Fig. 6 Principle of lock detector

### 4 测试结果

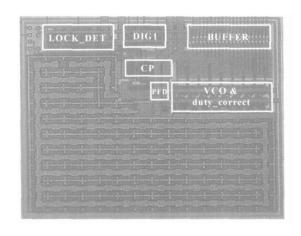

图 7 为频率综合器芯片照片. 版图设计方面注意了电源的净化,采用了模拟数字电源分开,并在每一个小的模拟和数字子模块周围都加保护环和退耦电容,同时避免敏感信号的过长布线和近距离并行. 测试包含两个部分:锁相环的时钟输出性能、相位选择功能是否正确. 前者可以直接通过时钟输出的分频反馈信号直接测量,而移相选择功能则需要间接通过数字均衡的测试结果得到.

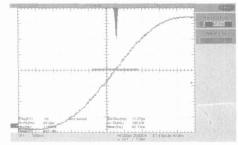

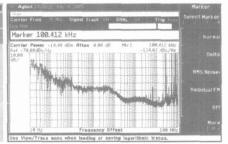

设定模式选择信号为千兆模式. 将 VCO 输出 经 5 分频反馈回 PFD 的信号引出作为测试信号测试其绝对抖动(延迟一个周期). 测试结果表明,在输

图 7 频率综合器芯片 Fig. 7 Photo of frequency synthesizer

入晶振抖动 = 16ps 情况下,该时钟输出波形良好,时钟抖动仅为 = 11ps,jitter<sub>peak-peak</sub> = 64ps,相位噪声为 - 124dBc/ Hz (100k Hz from 25M Hz) 如图 8 (a),(b)所示.而测试数字均衡部分也能得到正确的结果,表明时钟相位调节是准确有效的,也证明时钟照片的良好性能,保证了 128 个相位选择的单调.

图 8 测试波形 (a) 25MHz 测试时钟的抖动特性;(b) 25MHz 测试时钟的相位噪声

Fig. 8 Measurement results (a) Jitter characteristic of the 25MHz clock; (b) Phase noise of the 25MHz clock

# 5 结论

本文设计了一个应用在 1000Base T 并能兼容 10/100Base T 以太网的频率综合器,为模拟前端发送和接收电路提供全部的时钟信号. 电路采用简单高速的 TSPC 鉴频鉴相器,结构简单的低功耗电荷泵和压控振荡器构成一个性能良好的锁相环,同时设计一个稳定的电压型内插电路,提供较均匀相位间隔为 1/128 的多相时钟,很好地保证了数字处理部分为收发电路提供各模式下所需的正确时钟(动态恢复和固定相位时钟). 经过测试,在晶振抖动=16ps 情况下,测试时钟波形良好, 约为 1lps,peak-peak 抖动仅为 64ps,相位噪声为 - 124dBc/Hz(100k Hz from 25M Hz). 整个频率综合器正常工作情况时,电路功耗小于 4mW. 因此,该设计是一个

很好的低功耗低抖动时钟电路,能够为快速、高速以

太网提供精准的多相时钟.

#### 参考文献

- [1] Iravani K, Saleh F, Lee D, et al. Clock and data recovery for 1. 25 Gb/s Ethernet transceiver in 0. 35µm CMOS. Proceedings of the IEEE Custom Integrated Circuits, 1999:261

- [2] Li Shuguang, Ren Junyan, Yang Lianxing, et al. Clock and data recovery circuit for 2.5 Gbps Ggabit Ethernet transceiver. ASIC Proceedings 4th International Conference, 2001:330

- [3] Han Yifeng Li Qiang, Gu Canghai, et al. A novel transmitter for 10/100MHz Base TX Ethernet. Chinese Journal of Semi-conductors, 2005, 26(2):385(in Chinese) [韩益锋,李强,顾沧海,等.一种适用于10/100MHz Base TX 以太网的新型发射电路.半导体学报,2005,26(2):385]

- [4] Chang H H, Lin J W, Yang C Y, et al. A wide-range delay-locked loop with a fixed latency of one clock cycle. IEEE J Solid-State Circuits, 2002, 37(8):1021

- [5] Lee J, Kim B. A low-noise fast lock phase-locked loop with adaptive bandwidth control. IEEE J Solid-State Circuits, 2000,

35(8) :1137

- [6] Jan M. Rabaey. Digital integrated circuits ——a design perspective. Prentice- Hall International, Inc, 1998, 12

- [7] Maxim A. A 0. 16-2. 55-GHz CMOS active clock deskewing PLL using analog phase interpolation. IEEE J Solid-State Cir-

cuits, 2005, 40(1):110

[8] Yang Lixin, Yuan Jiren. An arbitrarily skewable multiphase clock generator combining direct interpolation with phase error average. Proceedings of the International Symposium on Circuits and Systems, 2003, 1(5): -645

# A Low Jitter and Low Power Frequency Synthesizer Applied to 1000 Base-T Ethernet

Lu  $Ping^{\dagger}$ , Wang Yan, Zheng Zengyu, and Ren Junyan

(State Key Laboratory of ASIC & System, Fudan University, Shanghai 200433, China)

Abstract: This paper adopts a high-speed TSPC frequency and phase detector, a typical charge pump, and cross-coupled differential delay cells to realized a good frequency synthesizer applied to 1000Base-T Ethernet transceiver as well as 10/100Mbps modes. This frequency synthesizer can not only meet the requirements of the transmitter for very precise rising (falling) edge time control but also offer much finer time-interval clocks than VCO natural multi-phase outputs, thus greatly saving area and power. The data show that the of the voltage control oscillator jitter cycle-cycle is only 11ps while that of the reference clock jitter-cycle-cycle is 16ps. This indicates that the frequency synthesizer works well for transmitters and receivers. The circuit is designed with SMIC 0. 18µm standard CMOS technology, the power supply is 1. 8V, and the power is lower than 4mW.

Key words: Ethernet; frequency synthesizer; clock jitter

**EEACC:** 1205; 1230; 1280

**Article ID**: 0253-4177 (2006) 01-0137-06