# Low Voltage Flash Memory Cells Using SiGe Quantum Dots for Enhancing F-N Tunneling<sup>\*</sup>

Deng Ning<sup>1</sup>, Pan Liyang<sup>1</sup>, Liu Zhihong<sup>1</sup>, Zhu Jun<sup>1</sup>, Chen Peiyi<sup>1,†</sup>, and Peng Li<sup>2</sup>

(1 Institute of Microelectronics, Tsinghua University, Beijing 100084, China) (2 Wuxi Microelectronics Research Institute, Wuxi 214035, China)

**Abstract :** A novel flash memory cell with stacked structure (Si substrate/SiGe quantum dots/tunneling oxide/poly-Si floating gate) is proposed and demonstrated to achieve enhanced F-N tunneling for both programming and erasing. Simulation results indicate the new structure provides high speed and reliability. Experimental results show that the operation voltage can be as much as 4V less than that of conventional full F-N tunneling NAND memory cells. Memory cells with the proposed structure can achieve higher speed, lower voltage, and higher reliability.

Key words:flash memory;SiGe quantum dots;enhanced F-N tunnelingPACC:6855;7340Q;7360JCLC number:TP333Document code:AArticle ID:0253-4177 (2006) 03-0454-05

### 1 Introduction

Although flash memory technology is highly developed, it faces critical challenges in achieving high speed and high density for the next generation. High-k dielectrics and novel program/erase mechanisms and structures have been studied for high density flash memory<sup>[1-3]</sup>. The main problem for high density memory is the relatively high operation voltage, which results in the necessity of a thick tunneling oxide and a complicated external high voltage circuit<sup>[4-6]</sup>. The tradeoff between high speed and reliability makes further down-scaling difficult.

F-N tunneling is an effective tunneling mechanism ,but it requires a high voltage (~18V) which is not favorable for high density memory. Several years ago ,a texture-like poly-dioxide film was proposed for enhancing F-N tunneling<sup>[7]</sup>. This reduced the operation voltage<sup>[8]</sup> ,but the quality of this kind of tunneling layer is too poor for use in real commercial devices<sup>[9]</sup>.

Here we demonstrate a novel Si substrate/ Si Ge quantum dots/tunneling oxide/poly-Si floating gate stacked structure (flat or with self-aligned tips) for achieving enhanced F-N tunneling for both programming and erasing. Theoretically, higher speed, lower voltage, and higher reliability can be expected for memory cells with the proposed structure. Both simulation and experimental results show that the operation voltage can be as much as 4V less than that of conventional full F-N tunneling NAND memory cells.

### 2 Device structure and principles

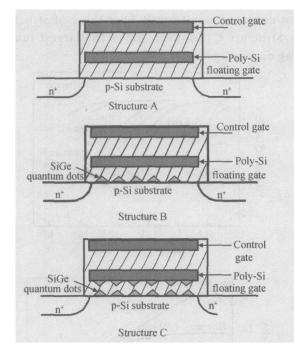

Figure 1 shows schematics of a memory cell with the conventional structure and two cells with the new structure. Structure A is a standard flash memory cell. In structures B and C, Si Ge quantum dots are fabricated directly on Si substrate with a UHV/CVD system to achieve enhanced F-N tunneling programming. The size and shape of the dots are controlled by growth parameters such as temperature ,duration ,and gas flux.

As shown in Fig. 1, structure A is a conventional full F-N tunneling NAND memory cell. In contrast to the flat floating gate in structure B, the poly-Si floating gate with self-aligned tips (structure C) is designed to achieve F-N tunneling for erasing and programming.

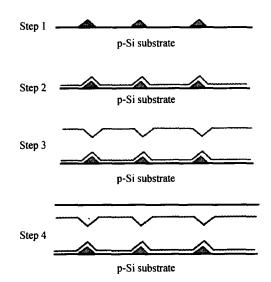

The fabrication process of the poly-Si floating gate with self-aligned tips is shown in Fig. 2. The Si film after the growth of Si Ge dots (step 2) is designed to form a tunneling oxide layer. The oxida-

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 69836020)

<sup>†</sup> Corresponding author. Email :chenpy @tsinghua.edu.cn

Received 26 October 2005, revised manuscript received 16 December 2005

Fig. 1 Schematic structure of conventional full F-N memory cell (A) and the two proposed enhanced F-N tunneling memory cells (B and C)

Fig. 2 Fabrication process of poly-Si floating gate with self aligned tips Step 1:self-assembled Si Ge dots; Step 2:Si films epitaxy; Step 3:oxidation; Step 4:poly-Si deposition

tion rate of the Si Ge quantum dots is much lower than that of Si substrate so that after the Si film is consumed, faster oxidation of Si substrate around the quantum dots results in a tunneling oxide with self-aligned pits on the surface (step 3). Then the self-aligned floating gate tips are deposited using these pits as moulds. Step 3 is the most important process for fabricating a floating gate with self-aligned tips. For a flat poly-Si floating gate, the Si concentration in the dots and the thickness of the tunneling oxide should be carefully designed to obtain a tunneling oxide without pits.

455

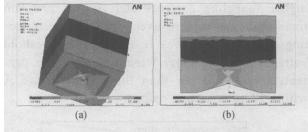

The electric field between the Si Ge quantum dots and floating gate was calculated in ANS YS. Figure 3 shows the local electrical field for structures B and C. For both structures, the local electric field near the Si Ge quantum dots is significantly enhanced because of the F-N tunneling geometrical enhancement factor of the quantum dots. As indicated ,the local field near the self-aligned tips in structure C is enhanced, and thus the tunneling current can be improved for erasing and programming.

Fig. 3 Local electrical field (a) Structure B; (b) Structure C

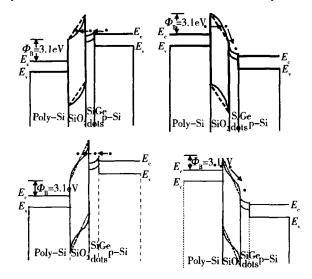

The energy band diagrams for structures B and C are shown in Fig. 4. Bidirectional barriers for both programming (injecting electrons from the channel to the floating gate) and erasing (drawing electrons out of the floating gate) faced by electrons in structure C are effectively nar-

Fig. 4 Energy band diagrams of sturcture B (top) and C(bottom) Left for programming; right for erasing

rowed ,and thus bidirectional F-N tunneling can be significantly enhanced. In structure B ,however ,only the barrier for programming is lowered , so F-N tunneling for erasing cannot be enhanced (actually ,the local electric field near the flat floating gate is even slightly weaker than in structure A).

## 3 Results and discussion

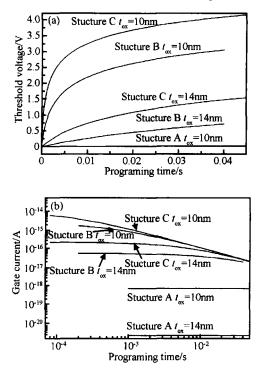

Figure 5 shows the simulated threshold voltage shift and gate current during programming operations for the three structures (assuming only one Si Ge quantum dot in the channel for structures B and C, a gate voltage of 16V, and a tunneling area of 30nm  $\times$ 30nm, which is much smaller than in real devices). Structures B and C yield higher tunneling currents and shorter program times than structure A. Even with a 14nm tunneling oxide in structures B and C, the threshold voltage shifts (memory windows) and gate currents are both larger than those of structure A with a 10nm tunneling oxide.

Fig. 5 Threshold voltage (a) and gate current (b) during programming processes Tunneling oxide thickness  $t_{ox} = 10$ ,14nm

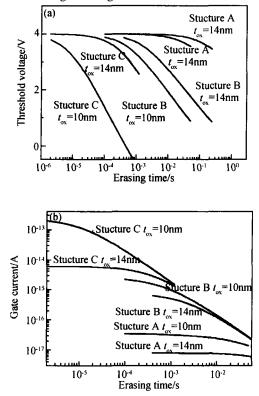

Figure 6 shows the corresponding results for erasing operations. As expected ,the threshold voltage and tunneling current of structure B are not improved significantly over those of structure A. Structure C, however, shows the largest tunneling current during erasing.

Fig. 6 Threshold voltage (a) and gate current (b) during erasing Tunneling oxide thickness  $t_{ox} = 10$ ,14nm

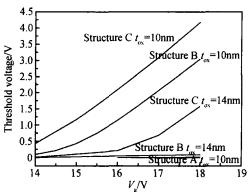

As shown in Fig. 7, the memory cells with a 10nm tunneling oxide with structures B and C show a larger threshold shift than conventional cells under relatively low control gate voltages. By extrapolation,  $V_{CG}$  can be reduced by about 4V without sacrificing the programming/ erasing speed of the conventional structure.

Fig. 7 Threshold voltage dependence on control gate voltage for the three structures Tunneling oxide thickness  $t_{ox} = 10$ ,14nm

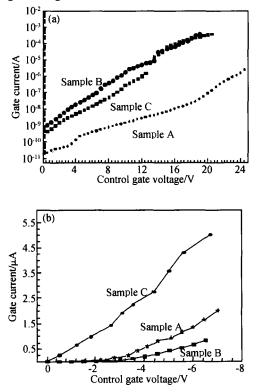

For comparison, samples with the three structures (Fig. 1.) were fabricated with standard 0. 8µm CMOS technology, and the tunneling current was measured. The measured gate currents of the three samples for both programming and erasing are shown in Fig. 8. They show the same trends observed in the simulation. The gate current during programming in samples B and C is more than  $10^3$  times better than that of sample A under a gate voltage of 12V. During erasing, only the gate current in sample C is improved significantly over sample A. This demonstrates the effectiveness of a floating gate with tips in enhancing F-N tunneling during erasing.

Fig. 8 Experimental results of gate current during programming (a) and erasing (b) for three structures

Finally, we explain how structure C improves reliability during programming and erasing. Because the mean electric field in the tunneling oxide is reduced by the enhanced F-N tunneling mechanism (for the same order of programming and erasing current), the strain induced by the local high electric field can be partially relaxed in the surrounding tunneling oxide ,where the elec- tric field is lower.

Furthermore, since a thicker tunneling oxide than in the conventional structure can be used with no loss of speed, the strain-induced leakage current (SILC) can be further reduced.

#### 4 Summary

In summary, we propose two new structures for flash memory cells with the enhanced F-N tunneling effect of SiGe quantum dots and self-aligned tips of the floating gate. The two structures for full F-N programming/ erasing show higher speed and lower operation voltage than the conventional structure without reducing the tunneling oxide thickness. Because of the low mean electric field in the tunneling oxide, higher reliability can be achieved for further scaling-down of the next generation flash memory.

#### References

- Paolo P, Roberto B, Piero O, et al. Flash memory cells<sup>-</sup> an overview. Proceedings of the IEEE, 1997, 85(8):124

- [2] Crisenza G, Annunziata R, Camerlenghi, et al. Non volatile memories :issues ,challenges and trends for the 2000 's scenario. Proc ESSDERC, 1996:121

- [3] Wada M, Mimura S, Nihira H, et al. Limiting factors for programming EPROM of reduced dimensions. IEDM Tech Dig, 1980:38

- [4] Hiroshi I, Hisayo S M. Ultra-thin gate oxides-performance and reliability. IEEE IEDM Tech Dig ,1998:163

- [5] Tan G,Cop R,Dijkstra J, et al. The impact of SILC to data retention in sub-half-micron embedded EEPROMs. Microelectron Eng, 1999 :419

- [6] Melik-Martirosian A, Ma T P, Wang X W, et al. An experimental flash memory cell with 55A EOT silicon nitride tunneling dielectric. Proceeding of the IEEE Nonvolatile Semiconductor Memory Workshop ,2001

- [7] Klein R, Owen W, Simko, et al. 5V only nonvolatile RAM owes it all to polysilicon. Electronics ,1979 ,10:111

- [8] Groeseneken G, Maes H E. Conduction in thermal oxides grown on polysilicon and its influence on floating gate EEP-ROM degradation. IEEE IEDM Technical Digest, 1984:476

- [9] Bisschop J, Korma EJ, Botta E F F, et al. A model for the electrical conduction in polysilicon oxide. IEEE Trans Electron Devices, 1986, 33:1809

- [10] Deng Ning, Chen Peiyi, Li Zhijian. Self-assembled Si Ge islands with uniform shape and size by controlling Si concentration in islands. J Cryst Growth ,2004 ,263 :21

## 基于 SiGe 量子点实现增强 F-N 隧穿的低压闪速存储器<sup>\*</sup>

邓 宁' 潘立阳' 刘志宏' 朱 军' 陈培毅<sup>1,†</sup> 彭 力<sup>2</sup>

(1清华大学微电子学研究所,北京 100084)(2无锡微电子研究所,无锡 214035)

摘要:提出了一种用于半导体闪速存储器单元的新的 Si/Si Ge 量子点/隧穿氧化层/多晶硅栅多层结构,该结构可 以实现增强 PN 隧穿的编程和擦除机制.模拟结果表明该结构具有高速和高可靠性的优点.测试结果表明该结构 的工作电压比传统 NAND 结构的存储器单元降低了 4V.采用该结构能够实现高速、低功耗和高可靠性的半导体 闪速存储器.

关键词:闪速存储器;SiGe量子点;增强 F-N 隧穿

PACC:6855;7340Q;7360J

中图分类号:TP333 文献标识码:A 文章编号:0253-4177(2006)03-0454-05

<sup>\*</sup>国家自然科学基金资助项目(批准号:69836020)

<sup>†</sup>通信作者. Email :chenpy @tsinghua.edu.cn 2005-10-26 收到,2005-12-16 定稿