## 基于类渗流导电的超薄栅氧化层 软击穿后的电流模拟 \*

## 王彦刚 计铭真 谭长华 段小蓉

(北京大学微电子学研究所,北京 100871)

摘要:研究了超薄栅氧化层(3.0nm)软击穿(soft breakdown,SBD)后的栅电流和衬底电流特性.提出了一个基于类渗流导电的 SBD 后栅电流和衬底电流的解析公式——类渗流导电公式.该公式能够在较大的电压范围(-4~+3V)模拟氧化层 SBD 后的栅电流和衬底电流的电流-电压特性,为超薄栅氧化层可靠性的研究提供了一个较为简便的公式.

关键词: 软击穿; 超薄栅氧化层; 类渗流导电

PACC: 7750; 7360H; 7340Q

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2006)04-0735-06

## 1 引言

随着金属-氧化物-半导体 (metal-oxide-semiconductor, MOS) 场效应器件几何尺寸的按比例缩小,栅氧化层越来越薄. 根据国际半导体工艺协会的预测,90nm的 CMOS 工艺中,栅氧化层厚度将减小到 1. 1nm<sup>[1]</sup>. 超薄栅氧化层的可靠性问题已经成为半导体工业界关注的焦点之一,其中,栅介质的导电行为是可靠性研究的重要组成部分,氧化层退化过程及击穿后的导电特性已经引起了人们的广泛兴趣<sup>[2~8]</sup>. 此外,薄栅(<3nm)下,量子效应将严重影响器件的特性,栅氧化层可靠性的研究面临着许多新的挑战,如直接隧穿(direct tunneling,DT) 栅漏电流的增大、硼穿透效应、多晶硅耗尽效应、工艺过程引起的电荷损伤等.

高场应力下,薄栅氧化层(<5nm)中出现了一种新的击穿模式,即软击穿(soft breakdown, SBD).SBD 后器件的电流-电压(I-V)行为比较复杂,栅电流(I<sub>g</sub>)在较高电压下明显偏离 Fowler-Nordheim(FN)隧穿导电规律.许多研究者报道了较高栅电压(<6V)下的 I<sub>g</sub> 特性,如基于 DT 机制的导电规律<sup>[2]</sup>、类 FN 隧穿<sup>[3,4]</sup>、渗流导电<sup>[5]</sup>、变步长跳跃导电<sup>[6]</sup>、量子点接触导电<sup>[7]</sup>等. 然而,上述导电模型有的需要花费较长时间迭代求解泊松方程,有的涉及的参数较多,从而使其应用受到了一定的限制.目前,仍然缺少一个适用于器件工作电压范围内

的 I-V 解析模型.

另外,在器件退化过程中,衬底电流(I<sub>b</sub>)也随应力时间不断增大.目前,I<sub>b</sub>已经成为 MOS 器件氧化层可靠性研究的重要参数之一<sup>[9]</sup>.有研究发现,薄栅氧化层 SBD 后的 I<sub>g</sub>与 I<sub>b</sub>存在线性关系<sup>[10]</sup>,二者的相关性有助于人们从不同方向探讨氧化层 SBD 后的导电机制.早期的 I<sub>b</sub>模型是基于碰撞电离机制的,后来的阳极空穴注入和价带电子隧穿模型在超薄栅下与实验结果存在很大偏差.目前同样缺乏一个氧化层 SBD 后简单适用的 I<sub>b</sub>模型.

本文利用类渗流导电模型和模拟的方法,对恒压应力下超薄栅 MOS 器件 SBD 后的 I<sub>s</sub> 和 I<sub>b</sub> 特性进行了研究,提出了一个简单描述 I<sub>s</sub> 与 I<sub>b</sub> 的 I-V 特性的半经验公式,在器件工作电压下,该公式与实验结果符合得很好.

## 2 实验

实验样品是  $0.13\mu m$  标准 CMOS 工艺制造的 MOS 场效应晶体管,栅氧化层是热生长的 SiO<sub>2</sub>,由量子力学的电容-电压方法测得的有效氧化层厚度分别为 1.9, 2.15, 2.4 和 3.0 nm, 面积为  $2.8 \times 10^{-5}$  cm<sup>2</sup>. 样品栅极施加恒定电压应力  $V_{\rm g,stress}$  (constant voltage stress, CVS) 进行退化实验,同时源端、漏端及衬底端接地. 实验温度分别为 300, 348 和 398 K. 用 HP4145B 型半导体参数分析仪测量器件的电流时间特性以监测氧化层的退化及击穿过程,实验过

<sup>\*</sup>国家重点基础研究专项基金资助项目(批准号:TG2000-036503)

<sup>†</sup> 通信作者. Email:wangyg@ime.pku.edu.cn 2005-09-03 收到,2005-11-11 定稿

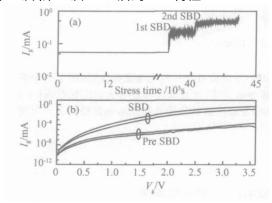

程中周期性的中断应力并进行 FV 特性的测量. 栅氧化层的软击穿结合栅电流-时间曲线的突变和 FV 特性的突变进行判定[8]. 图 1 给出了 FV 下,FV 和MOS 器件 SBD 前后的电流-时间特性以及 SBD 前和第一次、第二次 SBD 后的 FV 特性.

图 1 CVS 下, nMOS 器件 SBD 前后的电流-时间特性和 FV 特性  $t_{ox} = 2.15$  nm, T = 300 K,  $V_{g,stress} = 3.6$  V

Fig. 1 Current-time and current-voltage characteristics of nMOS device before and after SBD under CVS  $t_{ox} = 2.15 \text{ nm}$ , T = 300 K,  $V_{g,stress} = 3.6 \text{ V}$

## 3 结果和讨论

#### 3.1 栅电流

器件退化实验中,高场应力将在  $SiO_2$  内及  $Si/SiO_2$  界面处产生缺陷,这些缺陷将显著影响氧化层的导电特性. 根据渗流理论 $^{[11]}$ , 当缺陷密度达到一个极限值以后,将形成连接两极的低阻通道进而发生氧化层击穿,表现为  $I_g$  的突变. Okada 等人 $^{[12]}$ 和 Miranda 等人 $^{[13]}$ 发现,SBD 后的 FV 特性可以用幂律  $(power\ law\ ,PL)$  公式描述:

$$I_g = aV_g^b \tag{1}$$

其中 a, b 是常数. Houssa 等人[14] 利用非线性导电渗流网络和非弹性量子隧穿规律对该模型进行了解释,并发现 b 的值介于 2.9~3.3 之间.

另一种较为流行的 SBD 模型是阳极界面物理 损坏区模型  $^{[2]}$  ,又称有效氧化层减薄模型. 该理论认 为高场应力打断了 Si/ SiO2 界面处的 Si —O 键 ,氧原子的脱离使表面氧化层呈现体硅的特性 ,从而使有效 SiO2 层减薄. SBD 后仍然存在绝缘层 ,此时的氧化层更加容易通过载流子的直接隧道效应漏电 ,根据该理论 ,Sune 等人  $^{[7]}$  提出了量子点接触导电 (quantum point contact conduction ,QPC) 模型 ,之后 Miranda 等人对 QPC 进行了修正 ,提出了一个扩展的 QPC (extended QPC ,EQPC) 公式  $^{[15]}$  :

$$I_g = A sinh^n [B(V_g - V_0)]$$

(2)

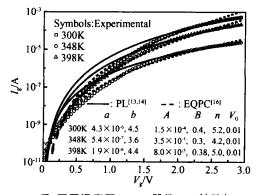

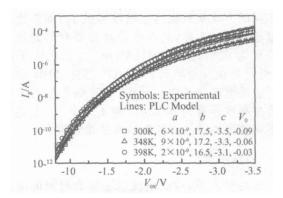

其中  $A \setminus B \setminus n \setminus V_0$  是常数. 图 2 是不同温度下 PL 公式和 EQPC 公式模拟结果与本文实验数据的比较. 通过最优化拟合发现,对超薄氧化层器件,PL 公式与实验结果在低压下存在较大的偏离,而 EQPC 公式在低压和较高压范围都与实验结果不符.

图 2 SBD 后,不同温度下 nMOS 器件 FV 特性与 PL 公式<sup>[13,14]</sup>和 EQPC 公式<sup>[16]</sup>模拟结果的比较  $t_{ox}=2.15$ nm,  $V_{g,stress}=3.5$ V

Fig. 2 Comparison between the FV characteristics and the fitting results by  $PL^{[13,14]}$  and  $EQPC^{[16]}$  for nMOS devices after SBD at different temperatures  $t_{ox} = 2.15 \text{nm}$ ,  $V_{g,stress} = 3.5 \text{V}$

本文在对大量实验数据分析模拟的基础上,结合现有击穿机制,提出了一个在较大电压范围内(从反型区到积累区),对两种类型器件均适用的简单公式:

$I = a(V_{ox} - V_0)^b exp[c(V_{ox} - V_0)]$  (3) 称为类渗流导电(percolation-like conduction, PLC) 公式. 其中参数 a 表征 SBD 前直接隧穿漏电流的大小,b 和 c 与 SBD 后栅氧化层的导电机制相关, $V_0$  是常数. a, b 和 c 的大小与 SBD 后参与导电的载流子在氧化层内的有效质量和 Si/SiO<sub>2</sub> 界面的势垒高度相关. 本文中,参数 a, b, c 和  $V_0$  通过模拟方法得到. 在考虑量子效应和多晶硅耗尽效应的基础上,栅氧化层电压( $V_{ox}$ )通过量子力学的电容-电压方法模拟得到: $V_{ox} = V_g - V_{EB} - Q_0 - Q_{oly}$ ,其中  $V_{EB}$ , $Q_0$  和  $Q_0$  和  $Q_0$  分别是平带电压、衬底的表面势和多晶硅的表面势.

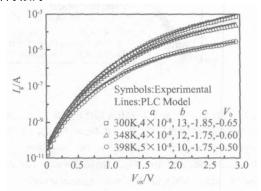

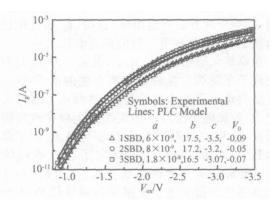

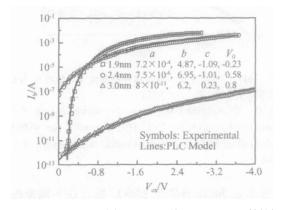

PLC 公式综合考虑了渗流导电和量子点接触导电的物理机制,意味着 SBD 后两种机制共同影响氧化层的导电特性. 模拟发现参数 c 一般为负值,说明高电压下渗流导电起主要作用(公式(3)中的幂指数项增加很大),而与隧穿导电对应的(3)式中的指数项变化不大. 这是因为在器件工作电压范围内载流子的直接隧穿几率变化不大,而非线性渗流漂移电流随电压剧烈增加. 我们对 PLC 公式的实用性和可行性在大量实验样品上进行了验证. 图 3 是nMOS 器件在不同温度下的实验数据与 PLC 公式

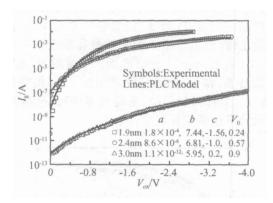

模拟结果的比较,该图与图 2 的实验数据相同. 图 4 是不同厚度的 nMOS 器件常温下实验数据与 PLC 公式模拟结果的比较. 模型参数随温度和氧化层厚度变化,通过选取优化的参数,模拟结果与实验数据符合得很好.

图 3 SBD 后,不同温度下 nMOS 器件反型区 I-V 特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15 \, \mathrm{nm}$ ,  $V_{g,stress}=3.5 \, \mathrm{V}$  Fig. 3 Comparison between the inversion I-V characteristics and the PLC fitting results for nMOS device after SBD at different temperatures  $t_{ox}=2.15 \, \mathrm{nm}$ ,

$V_{g,stress} = 3.5V$

图 4 SBD 后,不同厚度 nMOS 器件积累区 I-V 特性与 PLC 公式模拟结果的比较 T=300K

Fig. 4 Comparison between the accumulation I-V characteristics and the PLC fitting results for nMOS devices after SBD at different oxide thicknesses  $T = 300 \, \text{K}$

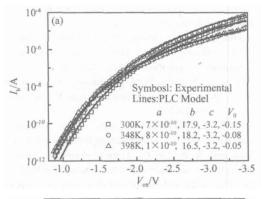

图 5(a)和(b)分别是 pMOS 器件在不同温度下及同一温度下多次 SBD 后的模拟结果,更薄栅 (1.9nm)pMOS 器件的模拟结果见图 10.上述模拟结果与实验数据的一致性进一步说明了利用 PLC 模型进行电路模拟的可行性.

表 1 是 PL C 公式模拟 2 15 nm 器件 SB D 后  $I_g$  -  $V_{ox}$ 特性的参数分析,i 和 i 分别表示参数 i 的 平均值和标准差,i 可以表示 lga, b, c 和  $V_0$ . 其中选取 nMOS 器件三种温度下的模拟参数作为一组数据,而 pMOS 器件不同温度下及同一温度下多次

图 5 (a) SBD 后,不同温度下 pMOS 器件反型区 I-V 特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15$ nm,  $V_{g,stress}=-3.8$ V; (b) 三次 SBD 后,pMOS 器件反型区 I-V 特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15$ nm, T=300 K,  $V_{g,stress}=-3.8$ V Fig. 5 (a) Comparison between the inversion I-V characteristics and the PLC fitting results for pMOS devices after SBD at different temperatures  $t_{ox}=2.15$ nm,  $V_{g,stress}=-3.8$ V; (b) Comparison between the inversion I-V characteristics and the PLC fitting results for pMOS devices after three SBDs  $t_{ox}=2.15$ nm, T=300 K, T=300

表 1 2. 15nm 器件氧化层 SBD 后  $I_g$  的 PLC 模型参数分析 Table 1 Analysis of  $I_g$  PLC model parameters for 2. 15nm device after oxide SBD

| $t_{OX} = 2.15  \text{nm}$ | lg <i>a</i> | lg a  | b      | b    | С      | c     | $V_0$  | v <sub>0</sub> |

|----------------------------|-------------|-------|--------|------|--------|-------|--------|----------------|

| nMOS                       | - 7.37      | 0.056 | 11.67  | 1.53 | - 1.78 | 0.058 | - 0.58 | 0.076          |

| pMOS                       | - 8.16      | 0.35  | 16. 98 | 0.45 | - 3.23 | 0.078 | - 0.06 | 0.022          |

过不同的方式从衬底到达栅极形成  $I_{\rm g}$ ,如渗流过程或量子隧穿过程等,其有效质量和要翻越的势垒高度分别为  $0.5~m_{\rm o}$  和  $3.~15{\rm eV}$ ,  $m_{\rm o}$  为自由电子的质量.而对处在反型状态的 p MOS 器件,SBD 后主要由衬底反型区价带空穴导电,其有效质量和要穿越的势垒高度分别为  $0.~32~m_{\rm o}$  和  $4.~7{\rm eV}^{[16]}$ ,上述参数的不同使得两种器件的模拟参数相差较大.

#### 3.2 衬底电流

高场应力下,衬底电流也随应力时间的增大而增加.SBD 发生时 Ib 突变,Crupi 等人[10] 首次提出监测 Ib 突变的方法判定击穿.目前,Ib 的退化已经成为表征 MOS 器件可靠性的重要参数之一.

在厚氧化层和高栅电压下,普遍认为 I<sub>b</sub> 是沟道热载流子在漏端发生碰撞电离产生的电子空穴对被衬底收集而形成的多子电流. 然而随着器件尺寸的缩小,外加电压已经不能提供发生碰撞电离所需的能量. 但 SBD 后低压下的 I<sub>b</sub> 仍将增大,对于薄栅低电压下 I<sub>b</sub> 的来源,人们提出了一些不同的观点<sup>[17]</sup>:如 5. 5nm 器件的阳极空穴注入模型,4. 5~5. 5nm 器件的价带电子陷阱辅助隧穿模型,4. 5nm以下器件的价带电子隧穿和变频光子泵效应<sup>[18]</sup>等.

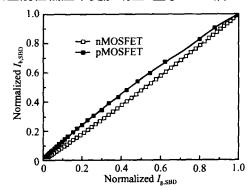

实验发现,SBD 后归一化的  $I_b$  与  $I_g$  在所研究的电压范围( $-4 \sim +3V$ )内存在近似线性关系. 如图 6 所示,图中对两个电流分别除以其最大值进行归一化. 但当  $V_{ox}$ 相同时,  $I_b$  与  $I_g$  的大小有较大差别,该差别在低压下更加明显. 鉴于 SBD 后  $I_b$  与  $I_g$

图 6 MOS 器件 SBD 后的归一化  $I_b$  与  $I_g$  的近似线性关系  $t_{ox}$  = 1. 9nm, T = 300 K

Fig. 6 Linear relationship between normalized  $I_b$  and  $I_g$  for MOS devices after SBD  $t_{ox}=1.9$ nm, T=300 K

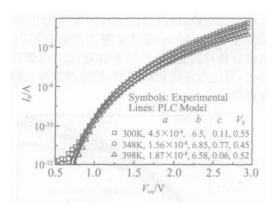

的近似线性关系,作为尝试,本文利用上面引入的公式(3)对 SBD 后的 Ib- Vox特性进行了模拟. 图 7 是 nMOS 器件不同温度下 SBD 后 Ib 实验值与 PLC 公式模拟结果的比较,该图与图 3 的实验数据取自同一组样品,模拟发现 Ib 与 Ig 的模型参数存在较大的差别. 由于模型参数由不同载流子的隧穿过程

图 7 SBD 后,不同温度下 nMOS 器件反型区  $I_b$ -  $V_{ox}$ 特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15 \, \mathrm{nm}$  ,  $V_{g,stress}=3.5 \, \mathrm{V}$  Fig. 7 Comparison between the inversion  $I_b$ -  $V_{ox}$  characteristics and the PLC fitting results for nMOS devices after SBD at different temperatures  $t_{ox}=2.15 \, \mathrm{nm}$  ,  $V_{g,stress}=3.5 \, \mathrm{V}$

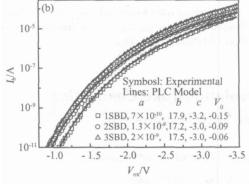

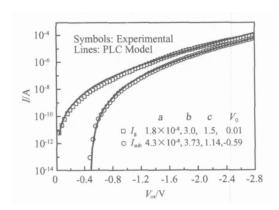

决定,上述模拟参数的不同说明 I<sub>b</sub> 与 I<sub>g</sub> 的产生机制是不同的.图 8 是不同厚度的 nMOS 器件常温下 I<sub>b</sub> 的实验数据与 PLC 公式模拟结果的比较,该图与图 4 的实验数据取自同一组样品.图 9 (a) 和 (b) 分别是 pMOS 器件在不同温度下一次 SBD 后及同一个样品三次 SBD 后 I<sub>b</sub> 的实验结果与 PLC 公式模拟的比较,该图与图 5 的实验数据取自同一组样品.图 10 是 1.9nm 的 pMOS 器件在常温下 SBD 后的模拟结果,作为比较,该图还示出了 I<sub>g</sub> 的模拟结果.通过大量样品的模拟,发现利用(3)式模拟的 I<sub>b</sub> 与实验结果能够较好地吻合.

图 8 SBD 后 ,不同厚度的 nMOS 器件积累区  $I_b$ -  $V_{ox}$ 特性与 PLC 公式模拟结果的比较  $T=300\,K$

Fig. 8 Comparison between the accumulation  $I_b\text{--}V_{ox}$  characteristics and the PLC fitting results for nMOS devices after SBD at different oxide thicknesses  $$T=300\,\text{K}$$

表 2 是 PLC 公式模拟 2.15nm 器件 SBD 后 Ib-Vox特性的参数分析,每一组原始参数的选取条件和表 1 相同.分析结果也和表 1 相似,对同类型的

图 9 (a) SBD 后,不同温度下 pMOS 器件反型区  $I_{b^-}$   $V_{ox}$ 特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15$ nm,  $V_{g,stress}=-3.8$ V; (b) 三次 SBD 后, pMOS 器件反型区  $I_{b^-}$   $V_{ox}$  特性与 PLC 公式模拟结果的比较  $t_{ox}=2.15$ nm, T=300 K,  $V_{g,stress}=-3.8$ V

Fig. 9 (a) Comparison between the inversion  $I_b$ -  $V_{ox}$  characteristics and the PLC fitting results for pMOS device after SBD at different temperatures  $t_{ox} = 2.15 \, \text{nm}$ ,  $V_{g,stress} = -3.8 \, \text{V}$ ; (b) Comparison between the inversion  $I_b$ -  $V_{ox}$  characteristics and the PLC fitting results for pMOS device after three SBDs  $t_{ox} = 2.15 \, \text{nm}$ ,  $T = 300 \, \text{K}$ ,  $V_{g,stress} = -3.8 \, \text{V}$

图 10 SBD 后, 1. 9nm pMOS 器件反型区 I<sub>g</sub> 和 I<sub>b</sub> 特性与PLC 公式模拟结果的比较 T=300 K

Fig. 10 Comparison between the inversion  $I_g$ ,  $I_b$  characteristics and the PLC fitting results for pMOS device after SBD  $t_{ox}=1.9 \, nm$ ,  $T=300 \, K$

器件,各模型参数随温度和击穿次数的变化不大,c和  $V_0$  的标准差在 0.1 以下,lga 和 b 的标准差在  $0.18 \sim 0.66$  之间,说明不同温度和多次 SBD 后  $I_0$  的导电机制是相同的.不同类型器件模拟参数的差别也是由于参与导电的载流子的有效质量以及载流子要穿越的势垒高度的不同引起的.

表 2 2 15nm 器件氧化层 SBD 后 I<sub>b</sub> 的 PLC 模型参数分析 Table 2 Analysis of I<sub>b</sub> PLC model parameters for 2. 15nm device after oxide SBD

| t <sub>ox</sub> = 2. 15nm | lg a   | lg a  | b     | b    | С      | c     | $V_0$   | v <sub>o</sub> |

|---------------------------|--------|-------|-------|------|--------|-------|---------|----------------|

| nMOS                      | - 7.63 | 0. 25 | 6.64  | 0.18 | 0.08   | 0.026 | 0.51    | 0.051          |

| pMOS                      | - 8.97 | 0.18  | 17.46 | 0.66 | - 3.16 | 0.089 | - 0.086 | 0.039          |

## 4 结论

综合考虑了渗流导电和量子点接触导电两种机制,提出了一个简单实用的 SBD 后 Ig 和 Ib 的经验解析公式.该公式能够在较大电压范围内模拟氧化层 SBD 后的 Ig- Vox, Ib- Vox特性,其使用不受器件类型、氧化层厚度(1.9~3.0nm)、环境温度、注入方式(栅或衬底注入)和击穿次数的限制.该公式的可行性已经在大量的实验样品上得到了验证.

**致谢** 感谢摩托罗拉公司为本工作提供了测试样品.

#### 参考文献

- [1] http: www.itrs.net/Common/2004 Update/2004\_03\_ PIDS.pdf

- [2] Lee S H, Cho B J, Kim J C, et al. Quasi-breakdown of ultrathin gate oxide under high field stress. IEEE Tech Dig Int Electron Devices Meet, 1994:605

- [3] Farmer K R, Saletti R, Buhrman R A. Current fluctuations and silicon oxide wear-out in metal-oxide-semiconductor tunnel diodes. Appl Phys Lett, 1988, 52(20):1749

- [4] Zhang H Q, Xu M ZH, Tan C H. Characteristics of ultrathin oxide pMOSFET device after soft breakdown. Chinese Journal of Semiconductors, 2003, 24(11):1149

- [5] Chen MJ, Kang T Kuo, Liu C H, et al. Oxide thinning percolation statistical model for soft breakdown in ultrathin gate oxides. Appl Phys Lett, 2000, 77(4):555

- [6] Houssa M, Nigam T, Mertens P, et al. Soft breakdown in ultrathin gate oxides: Correlation with the percolation theory of nonlinear conductors. Appl Phys Lett, 1998, 73 (4):514

- [7] Sune J, Miranda E, Nafria M, et al. Point contact conduction at the oxide breakdown of MOS devices. IEEE Tech Dig Int Electron Devices Meet, 1998:191

- [8] Wang Yangang, Xu Mingzhen, Tan Changhua, et al. Substrate current characteristics after soft breakdown in ultrathin gate oxide nMOSFTEs under constant voltage stress. Chinese Journal of Semiconductors, 2005, 26(5):999(in Chinese) [王彦刚,许铭真,谭长华,等. 恒压应力下超薄栅 nMOSFET软击穿后的衬底电流特性.半导体学报, 2005, 26

(5) -999

- [9] Pierpaolo P, Alberto D S, Luca S, et al. A comparative analysis of substrate current generation mechanisms in tunneling MOS capacitors. IEEE Trans Electron Devices, 2002, 49(8): 1427

- [10] Crupi F, Iannaccone G, Crupi I, et al. Characterization of soft breakdown in thin oxide nMOSFETs based on the analysis of the substrate current. IEEE Trans Electron Devices, 2001.48(6):1109

- [11] Degraeve R, Groeseneken G, Bellens R, et al. A consistent model for the thickness dependence of intrinsic breakdown in ultra-thin oxides. IEEE Tech Dig Int Electron Devices Meet, 1995:863

- [12] Okada K, Taniguchi K. Electrical stress-induced variable range hopping conduction in ultrathin silicon dioxides. Appl Phys Lett, 1997, 70(3):351

- [13] Miranda E, Sune J, Rodriguez R, et al. A function-fit model

- for the soft breakdown failure mode, IEEE Electron Device Lett, 1999, 20(6):265

- [14] Houssa M, Nigam T, Mertens P, et al. Model for the current-voltage characteristics of ultrathin gate oxides after soft breakdown. J Appl Phys, 1998, 84(8):4351

- [15] Miranda E, Mallaina E. Single-equation model for low and high voltage soft breakdown. conduction. Microelectron Reliab. 2004, 44(1):163

- [16] Yang B J , Lai P T, Wong H. Conduction mechanisms in MOS gate dielectric films. Microelectron Reliab ,2004 ,44(5):709

- [17] Schuegraf K F, Hu C. Metal-oxide-semiconductor fieldeffect-transistor substrate current during Fowler-Nordheim tunneling stress and silicon dioxide reliability. J Appl Phys, 1994,76(6):3695

- [18] Xu Mingzhen, Tan Changhua, Li Mingfu. Extended Arrhenius law of time-to-breakdown of ultrathin gate oxides. Appl Phys Lett, 2003, 82 (15):2482

# Current Simulation Based on the Percolation-Like Conduction in Ultra-Thin Gate Oxides After Soft Breakdown \*

Wang Yangang<sup>†</sup>, Xu Mingzhen, Tan Changhua, and Duan Xiaorong

(Institute of Microelectronics, Peking University, Beijing 100871, China)

Abstract: The characteristics of the gate current ( $I_g$ ) and substrate current ( $I_b$ ) of ultra-thin gate oxides ( 3nm) after soft breakdown (SBD) are studied. An analytic formula for  $I_g$  and  $I_b$  after SBD —the percolation-like conduction (PLC) formula, based on the percolation-like mechanism, is proposed. The post SBD current-voltage relationship of  $I_g$  and  $I_b$  in a larger voltage range (-4~+3V) is simulated with the PLC formula, which is simple for the study of ultra-thin gate oxide reliability.

Key words: soft breakdown; ultra-thin gate oxide; percolation-like conduction

PACC: 7750; 7360H; 7340Q

Article ID: 0253-4177 (2006) 04-0735-06

<sup>\*</sup> Project supported by the Special Funds for Major State Basic Research Project of China (No. TG2000-036503)

<sup>†</sup> Corresponding author. Email:wangyg@ime.pku.edu.cn