# Alloy Temperature Dependence of Offset Voltage and Ohmic Contact Resistance in Thin Base In GaP/ GaAs HBTs<sup>\*</sup>

Yang Wei<sup>†</sup>, Liu Xunchun, Zhu Min, Wang Runmei, and Shen Huajun

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

Abstract: The alloy temperature dependence of  $V_{offset}$  and  $R_{contact}$  is studied, and an optimal alloy temperature range for the best trade-off between  $V_{offset}$  and  $R_{contact}$  is given for thin base HBTs. In addition, the reason for the high  $V_{offset}$  at high alloy temperature is interpreted using Schottky clamped theory. The lower  $V_{offset}$  of our U-shaped emitter HBT than that of traditional strip emitter HBTs is explained.

Key words : heterojunction bipolar transistor; U-shaped emitter; alloy; offset voltagePACC : 7340JEEACC : 2560F; 2550H; 2550RCLC number : TN385Document code : AArticle ID : 0253-4177 (2006) 05-0765-04

### 1 Introduction

In GaP/ GaAs HBTs have inherent advantages, including low 1/f noise, low manufacturing cost, and a reliable fabrication process, that make them attractive for use in MMIC circuits<sup>[1~5]</sup>. The cutoff frequency  $f_t$  of a device is a key parameter that directly confines circuit operation speed<sup>[6]</sup>. Decreasing the base thickness is an effective way to enhance  $f_t$ . In the fabrication of HBTs, a high-temperature alloy process is usually adopted to form an ohmic contact to the collector. It is necessary to consider the influence of high alloy temperature on the thin base HBT. An excessive alloy temperature of the collector metal will induce a high offset voltage  $(V_{offset})$ , while an insufficient alloy temperature will be bad for the formation of ohmic contact to the collector ,and a bad contact will lead to a high specific contact resistance  $(R_{contact})$ . An HBT 's performance is greatly affected under both conditions<sup>[7~9]</sup>.

In this paper, the alloy temperature dependence of  $V_{\text{offset}}$  and  $R_{\text{contact}}$  has been studied. In addition, the reason for the high  $V_{\text{offset}}$  at high alloy temperature is interpreted using Schottky clamped theory. The lower  $V_{\text{offset}}$  in our U-shaped emitter HB T than that in traditional strip emitter HB Ts is explained by a formula deduced from the fundamental device equation.

#### 2 Experiment

Epitaxial structure plays a key role in an HBT 's performance. A 100mm GaAs-substrate epitaxial wafer grown by MBE was provided by the Shanghai Institute of Microsystem and Information Technology of the Chinese Academy of Sciences. The structure of the epitaxial layers is shown in Table 1. A high concentration of indium in the 9th layer helps form a good ohmic contact between the emitter metal and epitaxy layer. The 4th layer, as a base layer, is designed with a thickness of only 40nm to enhance  $f_t$ , whereas the normal base layer thickness is over 70nm.

| Table 1 Structure of the epitaxial layers |                    |       |                   |                              |        |

|-------------------------------------------|--------------------|-------|-------------------|------------------------------|--------|

| Layer No.                                 | Composition x      |       | Thickness<br>/ nm | Doping<br>/ cm <sup>-3</sup> | Dopant |

| 9                                         | $In_x Ga_{1-x} As$ | 0.6   | 50                | $>1 \times 10^{19}$          | Si     |

| 8                                         | $In_x Ga_1 - xAs$  | 0.6~0 | 50                | $>1 \times 10^{19}$          | Si     |

| 7                                         | GaAs               |       | 120               | 5 ×10 <sup>18</sup>          | Si     |

| 6                                         | $In_x Ga_{1-x}P$   | 0.5   | 50                | 3 ×10 <sup>17</sup>          | Si     |

| 5                                         | GaAs               |       | 3                 | Undoped                      |        |

| 4                                         | GaAs               |       | 40                | 4 ×10 <sup>19</sup>          | Be     |

| 3                                         | GaAs               |       | 2                 | Undoped                      |        |

| 2                                         | GaAs               |       | 150               | 2 ×10 <sup>16</sup>          | Si     |

| 1                                         | GaAs               |       | 500               | 5 ×10 <sup>18</sup>          | Si     |

| SI GaAs substrate                         |                    |       |                   |                              |        |

|                                           |                    |       |                   |                              |        |

<sup>\*</sup> Project supported by the Knowledge Innovation Engineering of the Chinese Academy of Sciences (No. KGX2-101) † Corresponding author. Email :weiyang @ustc.edu

Received 15 November 2005 , revised manuscript received 17 February 2006

In the device fabrication, the key process involved a self-aligned U-shaped emitter, a lateral etched undercut (LEU), a high temperature alloy, etc.

In the self-aligned emitter, the emitter metal acts as the mask for etching the emitter and as a shield in depositing the base metal.

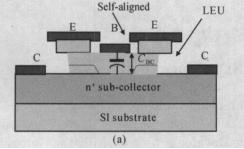

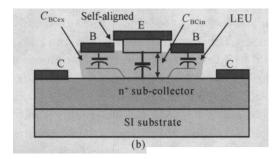

The majority of the extrinsic base-collector junction area is removed by  $L EU^{[10]}$  with a selective etchant. This means that  $G_{\rm bc}$ , a main nonlinear factor in HBTs, is greatly reduced in U-shaped emitter HBTs, compared to traditional strip HBTs<sup>[11]</sup>. The profiles of U-shaped emitter and traditional strip emitter HBTs are shown in Fig. 1.

Fig. 1 Comparative profiles of U-shaped emitter and traditional strip emitter HBTs (a) U-shaped emitter;(b) Strip emitter

To find a proper alloy temperature for the thin base HBT, an experiment is conducted in a temperature range from 360 to 420 , and  $V_{\text{offset}}$  and  $R_c$  are measured.

#### 3 Results and discussion

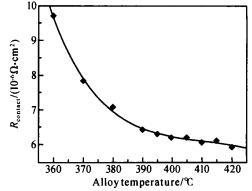

The ohmic contact resistance is measured using the transmission line method. The results are shown in Fig. 2. The specific contact resistance of the metal-semiconductor contact ( $R_{contact}$ ) is about 6 ×10<sup>-6</sup> · cm<sup>2</sup>.  $R_{contact}$  varies slowly with temperature ,but it increases faster as the temperature falls below 390 ,and almost reaches 1 ×10<sup>-5</sup> · cm<sup>2</sup> at 360 . Therefore , we think the alloy should be carried out above 390 .

Fig. 2 Alloy temperature dependence of R<sub>contact</sub>

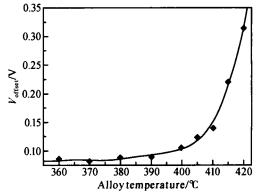

The alloy temperature dependence of  $V_{\rm offset}$  is shown in Fig. 3. The symbols are the experimental results ,and the solid line is the fitting curve.  $V_{\rm offset}$ increases slowly from 0. 085 to 0. 09V when the alloy temperature increases from 360 to 390 . But when the temperature exceeds 400 , $V_{\rm offset}$  increases dramatically , and reaches a very high va-lue , 0. 32V ,in 420 .

Fig. 3 Alloy temperature dependence of  $V_{\text{offset}}$  from 360 to 420

First from the experimental results shown above we can conclude that the optimal alloy temperature for a thin base HBT is between 390 and 400 for the best trade-off between  $V_{\text{offset}}$  and  $R_{\text{c}}$ .

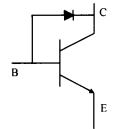

Second ,the high  $V_{\text{offset}}$  can be understood with Schottky clamped theory<sup>[12]</sup>. In a high temperature alloy ,the base contact metal might penetrate the base layer and reach the collector area. Then a Schottky diode is formed between the base and the collector. As shown in Fig. 4 ,a Schottky diode is parallel to the normal base-collector p-n junction. Then the transistor is said to be "Schottky clamped ". Since the turn-on voltage of a Schottky diode is lower than that of the p-n junction  $V_{offset}$  is larger when Schottky clamping occurs. As  $V_{offset}$  and hence  $V_{knee}$  increase, the output power and power efficiency of the device decrease, which are harmful to the power amplifier with a low power supply.

Fig. 4 Schottky clamped HBT

Another characteristic of the U-shaped HBT is that the value of  $V_{\text{offset}}$  is only about 0. 09V, while that of a traditional strip emitter HBT is about 0. 15V or higher<sup>[11]</sup>. In GaP/ GaAs HBTs have received much attention due to their inherent advantages, including better DC and AC performance, noise figure properties, and reliability than Al-GaAs/ GaAs HBTs. However, a disadvantage of In-GaP/ GaAs HBT is its larger offset voltage<sup>[9]</sup>. The lower  $V_{\text{offset}}$  of the U-shaped emitter HBT is attributed to the U-shaped layout structure and LEU technology. As can be seen in Fig. 1, the effective base-collector area of the U-shaped emitter HBT is greatly reduced. Base-collector junction capacitors (Cbc) measured using ICCAP also de-monstrate a reduction in U-shaped HB Ts. Liu<sup>[12]</sup> studied the relation between  $V_{\text{offset}}$  and the area ratio  $A_c/A_e$  for graded HBTs, where  $A_c$  and  $A_e$  are the collector and emitter areas, respectively. But abrupt HBTs have not been discussed. From fundamental physical relations,  $V_{\text{offset}}$  can be computed by<sup>[12]</sup>

$$V_{offset} = \frac{-\frac{bc}{d}KT}{q} ln\left(\frac{-l_{cs}}{f_{es}}\right) + \frac{-bc}{be} I_b R_e + (1 - \frac{-bc}{be}) (V_{be} - I_b R_b)$$

(1)

where  $I_{cs}$  and  $I_{es}$  are the base-collector diode saturation ration current and base-emitter diode saturation current, respectively. <sub>be</sub> and <sub>bc</sub> are the ideality factors of the emitter current in the reverse-active mode and of the collector current in the forwardactive mode, respectively, and <sub>f</sub> is the forward current transfer ratio. The first term of Eq. (1) is dominant in determining V<sub>offset</sub>. Since the <sub>f</sub>, I<sub>cs</sub>, and  $I_{es}\xspace$  are defined as follows :

$$I_{es} = \frac{qp_{e0} A_{e} D_{pe}}{L_{E}} + \frac{qn_{b0} A_{e} D_{nb}}{L_{B}} coth (X_{b}/L_{b})$$

(2)

$$I_{cs} = \frac{qp_{c0} A_c D_{pc}}{L_c} + \frac{qn_{b0} A_e D_{nb}}{L_B} coth (X_b / L_b)$$

(3)

$$_{f} = \frac{1}{I_{es}} \times \frac{qn_{b0} A_{e} D_{nB}}{L_{b}} \operatorname{coth}(X_{b}/L_{b}) \qquad (4)$$

From the above four equations, we get:

$$V_{offset} = \frac{-bc}{q} \frac{kT}{ln} \left( 1 + \frac{A_c}{A_e} \times \frac{L_b p_{c0} D_{pc}}{L_c n_{b0} D_{nb}} \right) + \frac{-bc}{be} I_b R_e + \left( 1 - \frac{-bc}{be} \right) \left( V_{be} - I_b R_b \right)$$

(5)

$$L_{c} = \sqrt{D_{pc}} \qquad (6)$$

$$L_{b} = \sqrt{D_{nB}} \qquad (7)$$

$$D_n = \frac{kT}{e}\mu$$

(8)

where  $L_b$  is the minority electron diffusion length in the base and  $L_c$  is the minority hole diffusion length in the collector. Equation (5) shows that  $V_{offset}$  increases with  $A_c/A_e$ . Since the other parameters in Eq. (5) are mainly determined by epitaxial material,  $A_c/A_e$ , which is determined by layout, is the only variable. Calculations using Eq. (5) show a rough difference of 0.05V between the U-shaped emitter HBT and the traditional strip emitter HBT, which roughly agrees with the experimental results. There is still some error between the computations and experimental results, which may be caused by the fabrication process of the HBT.

#### 4 Conclusion

For the best trade-off between  $V_{\text{offset}}$  and  $R_{\text{contact}}$ , a temperature in the range from 390 to 400 , is appropriate for the alloy of thin base HB Ts. High  $V_{\text{offset}}$  at high alloy temperatures can be interpreted using Schottky clamped theory. The lower  $V_{\text{offset}}$  in our U-shaped emitter HB T than in traditional strip emitter HB Ts is attributed to the lower  $A_c/A_c$ . This further demonstrates the superiority of U-shaped emitters, which was shown by Bai *et al.*<sup>[10]</sup> with high  $f_t$  and  $f_{\text{max}}$ .

Acknowledgements The author would like to thank Wang Suqin, Wang Ning, Liu Hongmin, Wu Jin, and Ma Xiaolin, for their enthusiastic help with this research.

#### References

- [1] Portilla J, Fuente M L, Pascual J P, et al. Low-noise monolithic Kurband VCO using pseudomorphic HEMT technology.

IEEE Microw Guided Wave Lett, 1999, 7:380

- [2] Rogers J W M, Macedo J A, Plea C. The effect of varactor nonlinearity on the phase noise of completely integrated VCOs. IEEE J Solid-State Circuits, 2000, 35:1360

- [3] Michael G C Johannes K N. A 3. 3-V 21-Gb/s PRBS generator in AlGaAs/ GaAs HBT technology. IEEE J Solid-State Circuits ,2000, 3:1266

- [4] Kroemer H. Heterojunction bipolar transistors and integrated circuits. Proc IEEE, 1982, 70:13

- [5] Asbeck P, Chang F, Wang K C, et al. GaAs-based heterojunction bipolar transistors for very high performance electronic circuits. Proc IEEE, 1993, 81:1709

- [6] Rodwell MJ W, Urteaga M, Mathew T, et al. Submicron scaling of HBTs. IEEE Trans Electron Devices, 2001, 48: 2606

- [7] Hattendorf M L , Hartmann Q J , Feng M. Incorporation of an

alloy-though passivating-ledge process into a fully self-aligned In GaP/ GaAs HBT process. GaAs MANTECH ,Inc ,2001

- [8] Lour W S. High-gain, low offset voltage, and zero potential spike by In GaP/ GaAs -doped single heterojunction bipolar transistor. IEEE Trans Electron Devices, 1997, 44:346

- [9] Cheng S Y. Analysis of improved dc and ac performances of an InGaP/ GaAs heterojunction bipolar transistor with a graded Al<sub>x</sub>Ga<sub>1-x</sub>As layer at emitter/ base heterojunction. Solid-State Electron, 2004, 48:1087

- [10] Bai Dafu,Liu Xunchun, Wang Runmei, et al. Super performance InGaP/GaAs HBT with novel structure. Chinese Journal of Semiconductors, 2004, 25(7):757 (in Chinese) [白 大夫,刘训春,王润梅,等. 高性能新结构 InGaP/GaAs 异质 结双极型晶体管.半导体学报,2004,25(7):757]

- [11] Shi Ruiying, Sun Haifeng, Liu Xunchun, et al. Key processes for fabrication of self-aligned InGaP/ GaAs HBT device and circuit. Chinese Journal of Semiconductors, 2005, 26(1):106 (in Chinese) [石瑞英, 孙海锋 刘训春, 等. 100mm InGaP/ GaAs HBT及相关电路关键工艺. 半导体学报, 2005, 26(1): 106]

- [12] Liu W. Handbook of heterojunction bipolar transistors. A Wiley-Interscience Publication, 1998

## 合金温度对薄基区 In Ga P/ Ga As 残余电压和欧姆接触的影响 `

杨 威<sup>†</sup> 刘训春 朱 旻 王润梅 申华军

(中国科学院微电子研究所,北京 100029)

摘要:研究了薄基区 HBT 合金温度对残余电压 Vorfset 和欧姆接触电阻 Roontact 的影响,给出了薄基区 HBT 的最佳合金温度区域.用肖特基钳位理论解释了合金温度过高导致 Vorfset 偏大的现象.从晶体管基本物理机制推导出 Vorfset 与集电极、发射极面积比 A<sub>c</sub>/A<sub>c</sub> 的关系,并用此解释了 U 形发射极 HBT 具有较小 A<sub>c</sub>/A<sub>c</sub> 的原因,进一步证明了 U 型发射极结构的优越性.

关键词:异质结双极型晶体管;U形发射极;合金;残余电压 PACC:7340J EEACC:2560F;2550E;2550R 中图分类号:TN385 文献标识码:A 文章编号:0253-4177(2006)05-0765-04

+通信作者. Email :weiyang @ustc.edu

2005-11-15 收到,2006-02-17 定稿

<sup>\*</sup>中国科学院知识创新工程资助项目(批准号:KGX2-101)