# A 16 bit Stereo Audio A/D Converter \*

Chen Lei<sup>1,†</sup>, Zhao Yuanfu<sup>2</sup>, Gao Deyuan<sup>1</sup>, Wen Wu<sup>2</sup>, Wang Zongmin<sup>2</sup>, and Zhu Xiaofei<sup>2</sup>

(1 Aviation Microelectronics Center, Northwestern Polytechnic University, Xi'an 710072, China) (2 Beijing Microelectronics Technology Institute, Beijing 100076, China)

Abstract: A 16 bit stereo audio novel stability fifth-order A/D converter that consists of switched capacitor modulators, a decimation filter, and a bandgap circuit is proposed. A method for the stabilization of a high order single stage modulator is also proposed. A new multistage comb filter is used for the front end decimation filter. The A/D converter achieves a peak SNR of 96dB and a dynamic range of 96dB. The ADC was implemented in 0.5µm 5V CMOS technology. The chip die area occupies only 4. 1mm x2. 4mm and dissipates 90mW.

Key words:A/D converter; switched capacitor; stability; decimation filter; bandgap circuitsEEACC:1265 HCLC number:TN432Document code:AArticle ID:0253-4177 (2006) 07-1183-06

## 1 Introduction

Oversampling A/D converters are currently the most popular converters for audio applications. High order A/D converters are the most suitable A/D converters for low-frequency, highresolution applications, in view of their inherent linearity ,low tone ,reduced antialiasing filtering requirements, and robust analog implementation<sup>[1,2,4]</sup>. Several stereo audio A/D converters have been reported  $[2^{2}]$ . This paper presents a lowcost stereo audio ADC and presents the modulator design. A novel stability fifth-order switched capacmodulator is given. A switched-capacitor itor integrator including an op-amp and a bandgap circuit is introduced. This paper also describes how to design a decimation filter, and a novel transformable stage non-recursive comb filter structure is presented.

# 2 Modulator design

#### 2.1 Proposed A/D converter topology overview

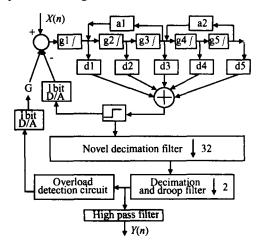

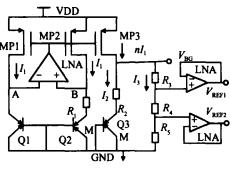

To achieve an overall signal-to-noise ratio (SNR) of about 96dB for a 16 bit output ,the proposed A/D converter consists of two identical novel stability fully differential fifth-order modulators which use a switched capacitor topology ,a special comb filter and droop filter ,a novel overload detection circuit ,and a bandgap reference. Figure 1 shows a block diagram of the stereo audio

A/D converter. Only one of the two fifth-order

modulators is shown in Figure 1 because they are identical. The modulator coefficients were derived from a fifth-order inverse Chebyshev high pass filter. Two complex pairs of zeros in the passband control the rise of the quantization noise floor at the passband edge<sup>[3]</sup>.

Fig. 1 16 bit stereo audio A/D converter architecture

The modulator shapes the quantization noise, shifting it out of the audio band in the fre-

<sup>\*</sup> Project supported by the State 10th Five- Year National Defense Pre-Research Plan of China (No. 41308010307)

<sup>†</sup>Corresponding author. Email :chenleinpu @yahoo.com

Received 15 October 2005, revised manuscript received 10 April 2006

quency domain. The high order of the modulator enables it to randomize the modulator outputs, reducing idle tone levels. The 1 bit stream, which is sampled 64 times from the modulator, is converted to once-sampled 16 bit data.

This also acts as a low pass filter to remove the shaped quantization noise. A novel decimation filter and decimation and droop filter will achieve the decimationby-64 as shown in Fig. 1. The DC components are removed by a digital high pass filter.

# 2.2 A novel method to stabilize a high order modulator

All high-order single loop modulators are conditionally stable. Various stabilization techniques for restoring the normal operation of a modulator have been proposed<sup>[2,5]</sup>. There are two common nonlinear global stabilization techniques for sensing instability: the state-variable clamping technique and the integrator reset technique. The other approach is to use local feedback signals to stabilize the modulator. In single bit designs, the integrator reset approach is the preferred solution to this problem. There are two commonly used instability detection methods. One is to look for long strings of 1s or 0s at the modulator output. The other method is to monitor the signal amplitude at the quantizer input to see if predetermined amplitude thresholds are exceeded for a specified number of consecutive clock cycles<sup>[4,5]</sup>.

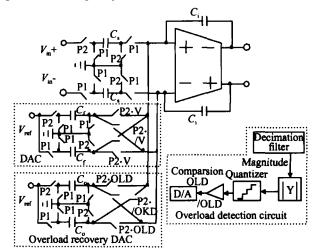

The above methods are based on detecting the analog part to give a feedback control signal. In this paper, we propose a method for the stabilization of a high order single stage modulator, which is to detect the digital decimation filter output to create a control signal. It is very simple compared to common stabilization techniques. A simple digital overload detection circuit pre-evaluates the decimation filter output and creates feedback signals to the first integrator through another overload recovery DAC as shown in Fig. 2. If the decimation filter output signal exceeds a high-threshold value, the feedback signal OLD controls the DAC output signal to be subtracted from the input signal of the first integrator in order to keep the modulator stable. However, if the decimation filter output signal is less than a low-threshold value, the feedback signal OLD controls the DAC output signal to be added to the input signal of the first integrator. G is the control gain factor on addition and subtraction, which is determined by  $C_0$  and  $C_f$ . An estimate of the input signal magnitude is obtained digitally by processing the output of the decimation filter as shown in Fig. 1. The composite addition or subtraction value is about 5% of the full scale peak-topeak value of the analog input voltage. It can increase the dynamic range by 2dB. Therefore, one concern is the phase delay through the decimation filter ,which could cause a misalignment. Since the input signal is heavily oversampled, it is moving relatively slowly with respect to the sample clock, which will further alleviate the cause for concern over phase misalignment through the filter.

#### 2.3 Switched-capacitor integrator

The modulator samples the analog input at a 3. 072M Hz rate, which is 64 times the 48k Hz A/ D converter output rate. A fully differential switched capacitor implementation was chosen for better common-mode rejection of digital noise from the substrate and the power supplies.

#### 2.3.1 First SC integrator

Figure 2 shows the first integrator of the first stage with a 1bit DAC and an overload recovery DAC. The analog integrator is driven by nonoverlapping two-phase clocks P1 and P2, and the bottom plate sampling is used to minimize inputdependent charge injections.

Fig. 2 First SC integrator ,DAC ,and overload recovery DAC

On phase 2 of the non-overlapping clock, the differential input is sampled onto the capacitor  $C_s$ . To avoid distortion due to signal dependent charge injection, the grounded phase 2 switch is opened

slightly before the input phase 2 switch. On phase 1, the input capacitors are connected to the op-amp input terminals, and the stored charge is transferred. The signals V and / V are the true and complemented outputs of the comparator. Instead of using both a positive and a negative reference, the feedback sense of the reference is inverted by swapping the phase 1 and phase 2 clocks on the reference input sampling switches<sup>[5,6]</sup>.

The specifications of the subsequent integrators were much more relaxed because non-idealities associated with them are greatly attenuated when referred back to the input. The second to fifth integrator had to be treated with some care to assure that they do not contribute any excess noise at the band edge. The differential architecture is fully pipelined, with each integrator having an effective delay of one sample. The comparator was a dynamic latching comparator. Switched-capacitor common-mode feedback was used in the op-amps of all the integrators.

#### 2.3.2 Op-amp design

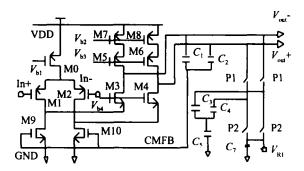

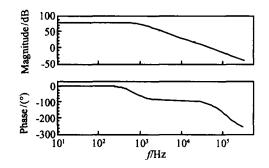

The performance of the input amplifier in higher order loops determines the overall converter performance. The op-amp of the first integrator is one of the converter<sup>[4,6]</sup>. As shown most critical circuits in a in Fig. 3 ,a standard folded cascode op-amp was considered adequate for this dc gain requirement ,and no gainenhancement techniques were incorporated. A P-channel input stage is used for reducing the 1/f noise. When the non-linearity of the OTA gain is considered, the gain of the first OTA needs to be increased to 80dB in order to limit the distortion. The first OTA requires a dominant closed-loop pole of at least 1.5 times the sampling frequency of the converter. Note that 15 % was added to the specifications of the pole to take the time loss for non-overlapping and delayed clock signals into account. Therefore the dominant closed-loop pole is large to 1.5 ×1.15 × $f_s^{[7]}$ . The folded cascode opamp magnitude and phase frequency response are shown in Fig. 4.

The fully differential op-amp needs a common mode voltage feedback circuit to keep the sum of the outputs at the midpoint between the supply rails<sup>[6]</sup>. The amplifier employs switched capacitor common mode feedback (CMFB) as shown in Fig. 3. Capacitors  $C_1$  and  $C_2$  are used to sense the output common-mode voltage.  $C_3$ ,  $C_4$ , and  $C_5$  are charged in the P2 clock.

Fig. 3 Folded-cascode op-amp and common mode circuits

Fig. 4 Folded-cascode op-amp magnitude and phase frequency response

#### 2.4 Bandgap reference circuits

References are key elements in the design of biasing schemes for analog or mixed-signal circuits. The bandgap reference circuit provides a very small dependence of the reference voltage on temperature. A high performance CMOS bandgap reference circuit using lateral bipolar transistors is presented in the high resolution ADC. The circuit is composed of a bandgap reference and a driver circuit. In the bandgap circuit, the LNA is a lownoise, low-offset op-amp. The input stage of the op-amps utilizes lateral PNP transistors<sup>[8]</sup>, and the LPNP transistor structure is the key component for successful operation. From Fig. 5, assuming that  $V_A = V_B$  and  $I_2 = I_1$ , the voltage  $V_{BG}$  is

$$V_{BG} = \frac{R_2}{R_1} \times \left(\frac{kT}{q} \ln M\right) + V_{BE3}$$

(1)

$V_{\text{REF1}}$  and  $V_{\text{REF2}}$  is

$$\begin{cases} V_{REF1} = \frac{R_4 + R_5}{R_3 + R_4 + R_5} \times V_{BG} \\ V_{REF2} = \frac{R_5}{R_3 + R_4 + R_5} \times V_{BG} \end{cases}$$

(2)

By choosing the appropriate  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ , and  $R_5$ , any  $V_{\text{REF}}$  with very low temperature sensitivity be-

Fig. 5 Bandgap reference circuits

tween the  $V_{BG}$  and GND can be obtained. The main advantage of the lateral PNP transistor is the improved noise performance, especially with low intrinsic 1/f noise and good and gain bandwidth, and its offset voltage is neglected, unlike with MOS devices. The reference voltage has a simulated temperature coefficient of 8 3ppm/ over the temperature range of - 40 to 125 at the typical model.

## **3** Decimation filter design

For this design a linear phase ,decimate-by-64 filter was developed with greater than 65dB stopband attenuation and less than 0. 05dB passband ripple. The passband is specified from dc to 0.  $453f_s$  ,and the stopband from 0.  $583f_s$ . To efficiently perform the decimation by 64 ,a multistage decimation filter was used. A front end filter decimates by 32 ,and a back-end filter does the final decimation by two<sup>[3,10]</sup>. The whole design architecture is shown in Fig. 1.

To reduce the circuit area and power ,we adopt a transformable stage non-recursive comb filter structure instead of the conventional comb filter. The conventional comb filter transform function<sup>[9]</sup> is shown in Eq. (3). In this paper ,however ,we adopt the transform function in Eq. (4) ,of which many simulations were made. The novel structure meets the design specifications and reduces the number of stages. Generally the outputs of comb filter enter into the compensatory filter in order to compensate the frequency roll off generated by the comb filters. The TSNC filter architecture is shown in Fig. 6.

$$H_{c}(z) = (1 + z^{-1})^{6} (1 + z^{-2})^{6} (1 + z^{-4})^{6} \times (1 + z^{-8})^{6} (1 + z^{-16})^{6}$$

(3)

$$H(z) = (1 + Z^{-1})^{3} (1 + Z^{-2})^{4} (1 + Z^{-4})^{4} \times (1 + Z^{-8})^{5} (1 + Z^{-16})^{7}$$

(4)

Thus the DC gain of the TSNC filter is  $2^3 \times 2^4 \times 2^4 \times 2^4$

$2^5 \times 2^7 = 2^{23}$ , and the corresponding data path width is 24bits. Therefore it can achieve 7-bit reduction in data path width with little loss in filter performance compared to conventional comb filter structures<sup>[4,5,9]</sup>. Polyphase parallel processing techniques were employed in order to further increase the sampling rate. The design method of the proposed decimation filter and conventional comb filters is a top-down way, which is constructed in SPW and described by Verilog-HDL language for system. Filter codes were simulated in Active HDL5.1 and synthesized in Synopsys DC. The two kinds of decimation filter were placed and routed in Cadence SE54, and laid out in Virtuoso with a standard cell of 0. 5µm COMS STD 90 library technology. The proposed filter has 45 % less hardware and 35 % power consumption compared to conventional comb filters in designing the same frequency circuits<sup>[10]</sup>.

| X(n) (1 | $+z^{-1})^{3}$ (1+z  | <sup>-1</sup> )* <u>-</u> (1+2                    | r')4          |

|---------|----------------------|---------------------------------------------------|---------------|

|         | $2^{-(1+z^{1})^{5}}$ | $\frac{1}{2} \frac{(1+z^{1})^{7}}{(1+z^{1})^{7}}$ | 2 <u>Y(n)</u> |

Fig. 6 TSNC filter architecture diagram

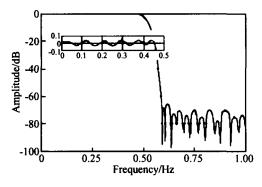

The back-end performs the final decimationby-two and compensates for the passband droop of the front-end filter. A 54-tap finite impulse response (FIR) filter is implemented as a poly-phase filter. The sums of pairs of the delayed TSNC filter outputs were stored in the data RAM. RAM is used to realize delay units in order to save the area and power consumption. The data RAM utilizes a 6T CMOS static memory cell. If shifter registers are adopted, one delay unit will need 30 T (D trigger)<sup>[11]</sup>. Vast data shifts can also be reduced by using RAM. The data from RAM enters the adder and multiplier. Instead of a conventional CSD (canonic signed digit) number system with shifters and adders ,our approach is to use 2 's complement Booth multiplier<sup>[12]</sup>. The multiplier coefficients are given by the ROM. The coefficients are required to be 13bits wide to meet the specifications. The Radix-4 Booth decoder will have 8 partial products. We choose sequential add in order to reduce chip area. The whole decimation filter frequency response is shown in Fig. 7.

## 4 Conclusion

A 16 bit stereo audio novel stability fifth-order A/D converter has been proposed. The ADC was implemented in 0. 5µm 5V CMOS technology.

Fig. 7 Decimation filter frequency response

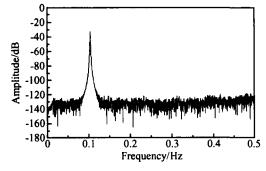

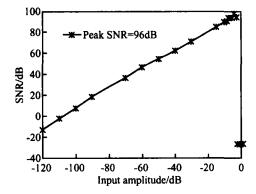

All test results were taken at nominal operating conditions :  $f_s = 3$ . 072M Hz ,with analog and digital supply of 5V. The measurement passband edge is 21. 8k Hz. Figure 8 shows a 1024-point FFT spectrum for a 5k Hz sine wave at - 30dBFS. The spectrum has a flat noise floor without any spurious components. The measured SNR ratios versus the relative input amplitude  $V_{in}/V_{ref}$  are shown in Fig. 9. The converter achieves a peak SNR of 96dB. The dynamic range is 96dB. THD

Fig. 8 1024-point FFT with 5kHz, - 30dBFS input

Fig. 9 SNR versus input level with 5kHz sinewave

and noise when the input signal is full scale (-0.5 dB) is -80 dB. Figure 10 shows the layout of the A/D converter. The chip die area occupies only 4. 1mm ×2. 4mm and dissipates 90mW.

Fig. 10 Layout of the A/D converter

#### References

- Leung K, Swanson EJ, Leung K. A 5V 118dB analog todigital converter for wideband digital audio. IEEE Int Solid-State Circuits Conf Dig Tech Papers, 1997:218

- Fujimori I, Koyama K, Trager D, et al. A 5-V single-chip delta-sigma audio A/D converter with 111dB dynamic range. IEEEJ Solid-State Circuits, 1997, 32(3):329

- [3] Maulik P C, Chadha M S, Lee W L, et al. A 16-bit 250kHz delta-sigma modulator and decimation filter. IEEE J Solid-State Circuits, 2000, 35(4):458

- [4] Xu Donglin, Zhao Hui, Wang Zhaogang, et al. A 5mW l. 8V low oversampling ratio modulator with 81dB dynamic range. Chinese Journal of Semiconductors, 2004, 25(1):12

- [5] Norsworthy S R, Schreier R. Delta-sigma data converters: theory, design, and simulation. IEEE Press, 1997

- [6] Ritoniemi T, Pajarre E, Ingalsuo S, et al. A stereo audio sigma delta A/D converter. IEEE J Solid-State Circuits, 1994, 29(12):1514

- [7] Geerts Y, Steyaert M, Sansen W. Design of multi-bit deltasigma A/D converters. Kluwer Academic Publishuers, 2002

- [8] Degrauwe M G, Leuthold O N, Vittoz E A, et al. CMOS voltage references using lateral bipolar transistors. IEEE J Solid-State Circuits, 1985, 20:1151

- [9] Crochiere R E, Rabiner L R. Multi-rate digital signal processing. Prentice Hall, Englewood Cliffs, USA, 1983

- [10] Chen Lei, Zhao Yuanfu, Gao Deyuan, et al. A modified decimation filter design for oversampled sigma delta A/D converters. The 6th International Conference on ASIC Proceedings, 2005:294

- [11] Chen Xiaoyuan. Circuit and physical design of decimator used in ovesampling A/D converter. Master Thesis, Tsinghua University, 1997:37

- [12] Sokolovic M, Jovanovic B, Damnjanovic M. Decimation filter design. 24th International Conference on Microelectonics, 2004,2:601

# 一种 16 位音频 A/D 转换器\*

陈 雷<sup>1,†</sup> 赵元富<sup>2</sup> 高德远<sup>1</sup> 文 武<sup>2</sup> 王宗民<sup>2</sup> 朱小飞<sup>2</sup>

(1 西北工业大学航空微电子中心,西安 710072)(2 北京微电子技术研究所,北京 100076)

摘要:提出了一种 16 位立体声音频新型稳定的 5 阶 A/D 转换器.该转换器由开关电容 调制器、抽取滤波器和带隙基准电路构成.提出了一种新的稳定高阶调制器的方法和一种新的梳状滤波器.采用 0.5µm 5V CMOS 工艺实现 A/D 转换器. A/D 转换器可以得到 96dB 的峰值 SNR,动态范围为 96dB.整个芯片面积只有 4.1mm x2.4mm,功耗为 90mW.

关键词: A/D转换器;开关电容;稳定性;抽取滤波器;带隙基准电路

EEACC: 1265 H

中图分类号:TN432 文献标识码:A 文章编号:0253-4177(2006)07-1183-06

<sup>\*</sup>十五国防预研资助项目(批准号:41308010307)

<sup>†</sup>通信作者. Email :chenleinpu @yahoo. com 2005-10-15 收到,2006-04-10 定稿