## SiC 隐埋沟道 MOS 结构夹断模式下的 C-∨ 特性畸变 \*

### 郜锦侠<sup>†</sup> 张义门 张玉明

(西安电子科技大学微电子学院 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

摘要:用数值和解析的方法研究了 SiC 隐埋沟道 MOS 结构夹断模式下 CV 特性的畸变. 隐埋沟道 MOSFET 中存在一个 pn 结,在沟道夹断以后,半导体表面耗尽区和 pn 结耗尽区连在一起,这时总的表面电容是半导体表面耗尽区电容和 pn 结电容的串联,使埋沟 MOS 结构的 CV 特性发生畸变. 文中通过求解泊松方程,用解析的方法分析了这种畸变发生的物理机理,并对栅电容进行了计算,计算结果与实验结果符合得很好.

关键词: 埋沟 MOS 结构; 夹断模式; CV 特性; SiC; 畸变

**PACC:** 7340Q; 7210

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177 (2006) 07-1259-05

## 1 引言

SiC 是一种宽禁带半导体,它在高温、高功率、高频、抗辐射方面具有很广泛的应用. SiC MOS FET 的特性一直受到低的反型层迁移率的限制[1],低的反型层迁移率是由于大的界面态密度和界面粗糙度散射所造成的[2].为了减小界面对载流子输运的影响,有人开始研究 SiC 埋沟 MOS FET [3]. 我们已经成功研制了 4H-SiC 埋沟 MOS FET [5]. 这种结构的器件被认为在高频大功率及其集成电路等领域中具有很好的应用前景. 怎样表征和提取器件基本参数就成为一个重要的问题.

BC-MOSFET 是在衬底表面注入一层与衬底掺杂类型相反的杂质,由于注入层很浅,其深度一般小于半导体表面反型时所产生的最大空间电荷区厚度,而且这层注入层会在半导体中形成一个 pn 结.这两个因素造成埋沟 MOS 结构 C-V 特性的畸变,使 C-V 特性有别于表面沟道 MOS 结构.在过去的三十年里,虽然有很多埋沟器件理论方面的研究<sup>[6~8]</sup>,但是却很少有人详细研究过埋沟 MOS 结构的 C-V 特性.本文通过数值和解析的方法分析了隐埋沟道 MOS 结构夹断模式下 C-V 特性的畸变.

## 2 理论分析

2.1 隐埋沟道 MOS 结构和常规 MOS 结构 CV 特性曲线的比较

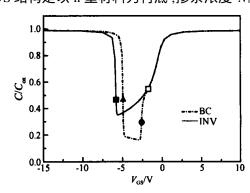

为更好地分析埋沟 MOS 结构(下面用 BC 表

示)的 CV 特性 ,用数值方法分别计算了隐埋沟道 MOS 结构和常规 MOS 结构 (用 INV 表示)的 CV 特性 ,如图 1 所示. 隐埋沟道 MOS 结构的参数为: 沟道区注入施主浓度  $N_D = 1 \times 10^{17}$  cm<sup>-3</sup> ,衬底掺杂浓度  $N_A = 2 \times 10^{16}$  cm<sup>-3</sup> ,沟道深度  $x_i = 0.2 \mu$ m. 而常规 MOS 结构是以 n 型材料为衬底 ,掺杂浓度  $N_D =$

图 1 埋沟和常规 MOS 结构 CV 曲线的比较

Fig. 1 Comparison of *CV* curves between BC and conventional MOS structures

8 ×10<sup>16</sup> cm<sup>-3</sup>. 栅氧化层厚度均取 40nm,平带电压  $V_{\rm FB} = 0$ V. 图中,实心圆点是隐埋沟道 MOS 结构的 沟道夹断阈值点(记为  $V_{\rm T}$ ),实心三角点和实心方块点分别是隐埋沟道 MOS 结构和常规 MOS 结构的表面反型阈值点. 空心方块点是沟道峰值电势开始小于 pn 结内建电势的临界点,当栅压大于该点时,沟道电势等于 pn 结内建电势  $V_{\rm B}$ ,两条曲线是重合的,BC MOS 结构中的 pn 结电容不起作用;当栅压

<sup>\*</sup>国家重点基础研究发展规划资助项目(批准号:A50103250091)

<sup>†</sup>通信作者. Email:gaogao \_ 505 @163.com

小于该临界点时,沟道中峰值电势开始小于 pn 结内建电势,BC MOS 结构的栅电容开始发生畸变.当栅压减小至夹断电压  $V_p$  时,沟道被表面耗尽区和 pn 结耗尽区夹断.由于注入沟道净掺杂浓度和常规 MOS 结构衬底的掺杂浓度是相同的,要使两者半导体表面反型,所需要的表面势是相同的,但是对于 BC 有注入层的存在,改变了半导体表面耗尽区和氧化层中的电场分布,使两者的表面反型阈值电压并不相同.

计算表明,当沟道深度较深或注入沟道掺杂浓度较高使沟道不能由栅压正常夹断的情况下,两种结构的 CV 特性曲线是完全重合的.

从上面的分析可知,埋沟器件 pn 结的存在会使它的 CV 曲线发生畸变,这种畸变有什么影响? 产生的机理是什么?目前还未见报道.

#### 2.2 夹断模式下泊松方程的解

利用耗尽近似和沟道均匀掺杂近似,对 BC 结构在夹断模式下的泊松方程进行求解,可以求出夹断模式下沟道中的峰值电势  $V_{ch}$ 、峰值电势所处的位置  $x_{sp}$ 及  $p_n$  结 p 型一侧耗尽区的坐标  $x_p$ .

$$V_{ch} = \begin{bmatrix} V_{s0} + \frac{q(N_D^+ + N_A^-)}{2_{s0}} & x_i^2 - V_{BS} \\ \frac{q(N_A^- X_i^2)}{2_{s0}} & \frac{q(N_D^+ + N_A^-)}{2_{s0}} + V_{BS} \end{bmatrix} - \begin{bmatrix} \frac{q(N_D^+ + N_A^-)}{2_{s0}} & \frac{q(N_D^+ + N_D^-)}{2_{s0}} & \frac{q(N_D^+ + N_D^$$

上面各式中  $V_{BS}$ 为衬源电位差;  $N_{A}$  为衬底中离化受主浓度;  $N_{D}$  为离化施主浓度;  $x_{P}$  为  $P_{D}$  相  $P_{D}$  则 是一侧耗尽区的宽度. 令  $V_{ch} = V_{bi} - (V_{bi} - V_{ch})$ , 由 (2), (3) 两式知, 夹断模式下埋沟 MOS 结构中的  $P_{D}$  结可以被看作为加上了一个大小为  $V = V_{bi} - V_{ch}$  的正向电压, 当  $V_{ch} = V_{bi}$  时, 等效的正向电压为零. 因

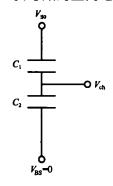

图 2 表面电容等效电路图

Fig. 2 Equivalent circuit of surface capacitance

此,夹断条件下埋沟 MOS 表面电容可以看作为半 导体表面耗尽区电容和 pn 结电容的串联,如图 2 所示.

#### 2.3 电容的计算

总的栅电容为:

$$\frac{1}{C} = \frac{1}{C_{ox}} + \frac{1}{C_s + C_{it}} \tag{4}$$

式中  $C_{ox}$  为氧化层电容;  $C_{t} = qD_{t}$  为界面态电容;  $C_{s} = -dQ_{s}/dV_{s0}$  为表面电容,  $Q_{s}$  是表面空间电荷层的电荷面密度. 经过数值求解泊松方程可知, 埋沟模式下  $p_{t}$  结耗尽区内的电势分布与表面势无关, 此时  $p_{t}$  结电容不起作用. 因此

$$C_s = C_1 = \frac{s - 0}{x_s}$$

(5)

式中 x<sub>s</sub> 可用耗尽层近似算出.

在夹断模式下,以峰值电势所在的位置为分界点,表面电容  $C_1$  是表面耗尽区电容  $C_2$  和  $p_1$  结电容  $C_2$  的串联:

$$\frac{1}{C_s} = \frac{1}{C_1} + \frac{1}{C_2} \tag{6}$$

利用耗尽层近似,忽略耗尽层中的自由载流子浓度,则夹断模式下等效的 MOS 结构空间电荷区电荷面密度  $Q_1$  和 pn 结耗尽区电荷  $Q_2$  分别为:

$$Q_1 = x_{sp} q N_D^+$$

(7)

$$Q_2 = (x_i - x_{sp}) q N_D^+$$

(8)

则 C<sub>1</sub> 和 C<sub>2</sub> 分别为:

$$C_{1} = -\frac{dQ_{1}}{d(V_{s0} - V_{ch})}$$

$$= -qN_{D}^{+}\frac{dX_{sp}}{dV_{ch}}\left[\frac{dV_{s0}}{dV_{ch}} - 1\right]^{-1} = \frac{s - 0}{X_{sp}} \qquad (9)$$

$$C_{2} = -\frac{dQ_{2}}{d(V_{bi} - V_{ch})} = -qN_{D}^{+}\left(\frac{dX_{sp}}{dV_{ch}}\right)$$

$$= \sqrt{\frac{q s - N_{A}^{-}N_{D}^{+}}{2(N_{D}^{+} + N_{A}^{-})(V_{ch} - V_{BS})}} \qquad (10)$$

$$C_{s} = 1/\left(\frac{1}{C_{1}} + \frac{1}{C_{2}}\right)$$

$$= 1/\left(\frac{X_{i}}{s - 0} + \sqrt{\frac{2N_{D}^{+}(V_{ch} - V_{BS})}{q - 0N_{A}^{-}(N_{A}^{-} + N_{D}^{+})}}\right) = \frac{s - 0}{X_{p}} \qquad (11)$$

## 3 计算结果与分析

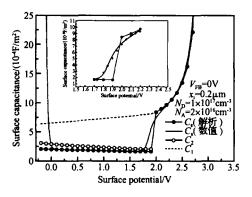

图 3 是埋沟器件在夹断模式下表面电容随表面势的变化关系. 图中,实线为数值方法计算出来的曲线;虚线为用(5)和(9)式计算的  $C_1$ 值;空心圆点线为用(10)式计算的  $C_2$ 值;实心圆点线为  $C_1$ 和  $C_2$ 的串联,即用解析方法计算出的表面电容值. 在用解析方法计算时假定:当峰值沟道电势小于  $C_1$ 即 结内建

电势时,用(11)式计算表面电容;当峰值沟道电势等于 pn 结内建电势时,不考虑 C 的影响. 当表面势小于 1. 7V,沟道完全夹断且半导体表面反型之前,用(11)式计算的表面电容与用数值方法计算的曲线是完全重合的;当表面势大于 2. 2V 时,沟道完全开启,MOS 结构工作于埋沟模式,pn 结电容不起作用. 此时,仅考虑 C 的作用所计算出来的曲线与数值计算结果也是完全重合的. 这说明用(5)式和(11)式可以准确地计算埋沟模式和夹断模式下的表面电容.

图 3 表面电容随表面势的变化关系

Fig. 3 Plot of surface capacitance as a function of surface potential

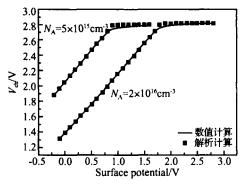

但是,从图 3 也可以看出,当 1.7V < V<sub>s0</sub> < 2.2V 时,这段区域是 MOS 结构从埋沟模式变为夹断模式的过渡区域,沟道中峰值电子浓度已经开始小于 Nb ,但还没有完全耗尽,峰值附近的载流子浓度不可完全忽略,因此耗尽层近似不再适用.峰值电势不等于 pn 结内建电势,但又不能用(1)式来计算.在该栅压范围内,数值计算的电容曲线和解析计算的电容曲线存在一些差别.图 4 是峰值电势随栅压的变化关系,无论掺杂浓度为何值,数值计算结果和解析计算结果都存在着一个不吻合的区域,该区域就对应着从埋沟模式到夹断模式的过渡区域.

图 4 峰值电势随表面势的变化关系

Fig. 4 Graph of peak potential versus surface potential

实际上,当表面势小于 2 2V,表面耗尽区的边缘已经开始深入到 pn 结的耗尽区,在该区域内载流子已经耗尽,随着表面势的减小,耗尽区的扩展速度加快.pn 结耗尽区内的载流子浓度随坐标的变化呈指数变化关系,我们用一个指数分布的等效耗尽层厚度代入(5) 式来近似计算过渡区的电容: $x_{s,eff} = x_{s0} + A_1e^{-V_{s0}/A_2}$ ,其中  $x_{s0}$ 为峰值电势开始小于 pn 结内建电势时的表面耗尽区宽度临界值, $A_1$ ,  $A_2$  为两个参数.要用解析方法准确解出这两个参数是非常困难的,对于本文所取的参数, $A_1$ ,  $A_2$  分别取 20.6 和 0.098 可以得到与数值解相符的曲线.如图 3 插图所示,图中,十字点线即为用该等效方法计算的结果.

将栅压和表面势的关系表示如下:

$$V_{G} = V_{s0} - V_{bi} - \frac{Q_{s}(V_{s0})}{C_{ox}} + V_{FB}^{*}$$

(12)

$$V_{FB}^{*} = -\frac{qQ_{f}}{C_{ox}} - \frac{qQ_{it}(V_{s0})}{C_{ox}} + \phi_{ms}$$

$$= V_{FB} - \frac{Q_{it}(V_{s0})}{C_{ox}} + \frac{Q_{it}(V_{s0} = V_{bi})}{C_{ox}}$$

(13)

其中  $V_{\text{FB}} = -qQ_{\text{C}}/C_{\text{Ox}} - qQ_{\text{It}}(V_{\text{s0}} = V_{\text{bi}})/C_{\text{Ox}} + \theta_{\text{hs}}$ 为由金属-半导体功函数差、固定氧化层电荷和界面态电荷确定的平带电压 ;  $Q_{\text{s}}(V_{\text{s0}}) = qN_{\text{D}}^{+}x_{\text{sp}}$ 为表面电荷密度 ;  $Q_{\text{F}}$  为固定氧化层电荷密度 ;  $\Phi_{\text{hs}}$  为金半功函数差 ;  $C_{\text{Ox}}$  为氧化层电容 ;  $Q_{\text{It}}(V_{\text{s0}})$  为界面态电荷密度 度.

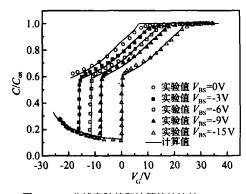

图 5 是埋沟 MOS 结构 C-V 特性理论曲线和实验曲线的比较. 实验曲线取自文献[3], 其基本参数为:电容面积 4 ×10<sup>-4</sup> cm<sup>2</sup>; 氧化层厚度为 73. 6nm; 沟道深度为 0. 16µm; n 型沟道掺杂浓度为 4.9 × 10<sup>17</sup> cm<sup>-3</sup>; p 型衬底掺杂浓度为 1 ×10<sup>16</sup> cm<sup>-3</sup>. 用耗尽层近似和均匀掺杂近似计算所得的最大耗尽层宽度约为 0. 1µm, 而 pn 结 n 型一侧耗尽区的宽度约为 14nm, 也就是说,在正常情况下,器件关断之前

图 5 CV 曲线实验值和计算值的比较

Fig. 5 Comparison between experimental and calculational *CV* curves

已经进入表面反型状态,靠 pn 结耗尽区和表面耗尽区无法使器件关断.因此要使沟道夹断,必须施加衬底电压.将以上各参数代入(4)式进行计算,在计算中,我们也计入了界面态的影响,所采用的是文献[9]所提出的指数分布界面态模型,禁带中部界面态密度取  $1 \times 10^{11}$  cm $^{-3}$ ,  $D_c = 1 \times 10^{13}$  cm $^{-3}$ , = 0.2eV.由图 5 可知,计算结果与实验结果符合得很好,说明用本文推出的解析表达式可以很好地描述各种工作模式下隐埋沟道 MOS 结构的 CV 特性.

## 4 参数提取分析

通过以上分析可以看出,隐埋沟道 MOS 结构表面积累时的栅电容仍然可以用来提取氧化层厚度.除此之外,根据本文模型,还可以用来提取下述参数.

#### 4.1 衬底载流子浓度的提取

结合方程(1)~(3)以及方程(12),(13),可以求 出夹断区栅电容和栅压之间的关系:

$$\left(\frac{C_{ox}}{C}\right)^{2} = \frac{2C_{ox}^{2}}{qN_{A} s_{0}} \left(V_{CS} - V_{FB} + V_{bi} + \frac{q(N_{A} + N_{D}^{+}) x_{i}^{2}}{2 s_{0}} - V_{BS} + \frac{q(N_{A} + N_{D}^{+}) x_{i} d}{ox_{0}} + \frac{q_{S_{0}} N_{A} d^{2}}{2 c_{ox}^{2}}\right)$$

(14)

这样,利用夹断区 $(C_{\text{ox}}/C)^2$ - $V_{\text{os}}$ 的线性关系的斜率就可以提取衬底载流子浓度  $N_{\text{A}}$ .

#### 4.2 沟道载流子浓度的提取

从图 1 可以看出,表面耗尽以后,沟道夹断之前,BC MOS 结构和常规 MOS 结构的 CV 特性有一段重合的区域,栅电容和栅压之间的关系可表示为:

$$\left(\frac{C_{ox}}{C}\right)^{2} = 1 - \frac{2 C_{ox}^{2} (V_{G} - V_{FB}^{*})}{q_{s \ 0} N_{D}^{+}}$$

(15)

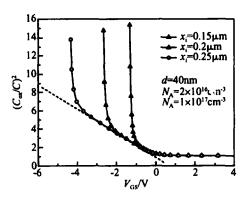

这样,在忽略界面态影响的情况下,可以用该区域的( $C_{\rm ox}/C$ ) $^2$ - $V_{\rm ox}$ 的线性关系来提取沟道载流子浓度  $N_{\rm o}^+$ ,但是如果衬底掺杂浓度太大或者沟道太浅,  $C_{\rm ox}V$  曲线在表面耗尽以后很快就发生畸变,以至于无法确定上述的线性关系,于是,这种方法就不再适用,如图 6 所示.对于图中给出的参数条件,在沟道深度为 0. 15 $\mu$ m 时,就没有一个明显的线性区域,因此,这种情况下不能用( $C_{\rm ox}/C$ ) $^2$ - $V_{\rm ox}$  曲线斜率来提取  $N_{\rm ox}^+$ .

#### 4.3 注入沟道深度的提取

在平带电压、衬底载流子浓度和沟道载流子浓

图 6 不同离子注入沟道深度下的( $C_{\rm Ox}/C$ )  $^2$ - $V_{\rm GS}$ 曲线 Fig. 6 ( $C_{\rm Ox}/C$ )  $^2$  versus  $V_{\rm GS}$  at different channel depths

度已知的情况下,可利用夹断区 $(C_{cx}/C)^2$ - $V_{cs}$ 曲线的截距提取出注入沟道深度.

## 5 结论

本文提出了注入埋沟 MOS 结构的 CV 特性的模型,该模型揭示了埋沟 MOS 的 CV 特性发生畸变的机理,与文献中的实验数据相比,本文模型与文献报道的实验结果符合得较好,说明本文模型的正确性.本研究不仅给出了埋沟 MOS 结构夹断模式下 CV 特性的一种物理上的理解,也对隐埋沟道MOS 结构设计和研究,以及这种结构的参数提取起到指导作用.

#### 参考文献

- [1] Chung G Y, Tin C C, Williams J R, et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Lett, 2001,22(4):176

- [2] Das M K, Um B S, Cooper J A Jr. A nomalously high density of interface states near the conduction band in SiO<sub>2</sub>/4H-SiC MOS devices. Mater Sci Forum, 2000, 338 ~ 342:1069

- [ 3 ] Sheppard S T, Melloch M R, Cooper J A Jr. Characteristics of inversion-channel and buried-channel MOS devices in 6 H-SiC. IEEE Trans Electron Devices, 1994, 41 (7):1257

- [4] Harada S, Suzuki S, Senzaki J, et al. High channel mobility in normally-off 4H-SiC buried channel MOSFETs. IEEE Electron Device Lett, 2001, 22(6):272

- [5] Gao Jinxia, Zhang Yimen, Zhang Yuming. Fabrication of 4H-SiC buried-channel nMOSFETs. Chinese Journal of Semiconductors, 2004, 25 (12):1561

- [6] Edwards J R, Marr G. Depletion mode IGFET made by deep ion implantation. IEEE Trans Electron Devices, 1973, 20 (3): 283

- [7] Rao G R. An accurate model for a depletion mode IGFET used as a load device. Solid-State Electron, 1978, 21 (5):711

- [8] Turchetti C, Massetti G. Analysis of the depletion-mode MOSFET including diffusion and drift currents. IEEE Trans Electron Devices, 1985, 32 (4):773

[9] Tang Xiaoyan, Zhang Yimen, Zhang Yuming. Analysis of the effect of interface state charges on threshold voltage and transconductance of 6 H-SiC N-channel MOSFET. Acta Physica Sinica,2002,51(4):771(in Chinese)[汤晓燕,张义门,张玉明. 界面态电荷对 6 H 碳化硅 n 沟 MOSFET 阈值电压和跨导的影响. 物理学报,2002,51(4):771]

# C-V Characteristic Distortion in the Pinch-Off Mode of a Buried Channel MOS Structure in 4 H SiC\*

Gao Jinxia<sup>†</sup>, Zhang Yimen, and Zhang Yuming

(Key Laboratory of the Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, Microelectronics Institute, Xidian University, Xi'an 710071, China)

Abstract: The distortion of the C-V characteristics of a SiC buried-channel MOS structure is presented. It is difficult to characterize the gate capacitance because there is a pn junction in buried-channel MOS FETs. The surface depletion region and m side space-charge region merge when the channel is punched through. In this case, the total surface capacitance is the sum of the surface depletion region capacitance and the pn junction capacitance, and the C-V characteristics are distorted. The analytic expression of gate capacitance in the pinch-off mode is obtained by solving Poisson's equation. The C-V characteristics in the pinch-off mode are analyzed on a fundamental physical level. The gate capacitance calculated with the model agrees well with experimental results.

Key words: buried-channel MOS structure; pinch-off mode; C-V characteristics; SiC; distortion

**PACC:** 7340Q; 7210

**Article ID**: 0253-4177 (2006) 07-1259-05

<sup>\*</sup> Project supported by the State Key Development Program for Basic Research of China (No. A50103250091)

<sup>†</sup>Corresponding author. Email:gaogao \_ 505 @163.com