# A High Performance 0. 18µm RF nMOSFET with 53 GHz Cutoff Frequency \*

Yang Rong, Li Junfeng<sup>†</sup>, Xu Qiuxia, Hai Chaohe, Han Zhengsheng, and Qian He

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract :** This paper presents the fabrication and performance of a 0. 18 $\mu$ m nMOSFET for RF applications. This device features a nitrided oxide/poly-silicon gate stack, a lightly-doped-drain source/drain extension, a retrograde channel doping profile, and a multiple-finger-gate layout, each of which is achieved with conventional semiconductor fabrication facilities. The 0. 18 $\mu$ m gate length is obtained by e-beam direct-writing. The device is fabricated with a simple process flow and exhibits excellent DC and RF performance :the threshold voltage of 0. 52V, the sub-threshold swing of 80mV/dec, the drain-induced-barrier-lowering factor of 69mV/V, the off-state current of 0. 5nA/ $\mu$ m, the saturation drive current of 458 $\mu$ A/ $\mu$ m (for the 6nm gate oxide and the 3V supply voltage), the saturation transconductance of 212 $\mu$ S/ $\mu$ m, and the cutoff frequency of 53GHz.

Key words: structure; process; radio frequency; nMOSFETEEACC: 2550; 2560RCLC number: TN385Document code: AArticle ID: 0253-4177(2006)08-1343-04

## 1 Introduction

In recent years ,the scaling down of CMOS has led to significant improvements in the RF performance of MOS devices. Consequently, CMOS has become a viable option for analog/ RF applications in the multi-GHz frequency range. Compared with the GaAs technology that is widely used in RF applications, CMOS technology has the advantages of a mature process, low cost, and high integration density. The ITRS Roadmap 2003<sup>[1]</sup> predicted that RF CMOS would be predominant in cost-sensitive RF applications, such as Bluetooth and WLAN, which have been demonstrated tremendous market potential. To date, many RF CMOS products have become available in markets or reached the demonstration stage. RF/ mixed signal CMOS circuit fabrication services are also available in mainstream foundries<sup>[2~7]</sup>.

However, in the Chinese mainland, RF CMOS research is far behind that of the international community. In 2004, we reported a 0. 25µm SOI RF MOSFET with a 17. 78 GHz cutoff frequency<sup>[8]</sup>. This was later improved to 25. 6 GHz for the same gate length<sup>[9]</sup>. However, this is still much lower than that of currently available 0. 25µm MOSFETs with cutoff frequencies in the 30 ~ 40 GHz range<sup>[2,4]</sup>. With much effort, we have scaled the gate length down to 0. 18µm for bulk silicon devices and achieved a 53 GHz cutoff frequency in this work. These specifications are comparable to state of the art technologies provided by foundries (40 ~ 60 GHz)<sup>[2,4]</sup>. The simple process flow and the DC characteristics of the device are also presented.

### 2 Structure and fabrication

The starting substrate material was 100mm ptype (001) wafer with a resistivity of  $10 \sim 20$  . cm. The main processes were based on the technology platform for 0.  $1 \sim 0.35 \mu$ m CMOS integrated circuits that was developed at the Institute of Microelectronics of the Chinese Academy of Sciences (IMECAS)<sup>[10,11]</sup>. Some necessary adjustments were made for RF MOSFETs.

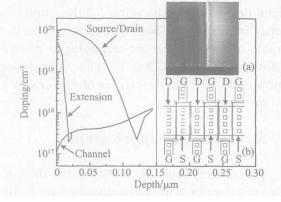

The process flow is shown in Fig. 1. After LO-COS isolation, dual implants (B and  $BF_2$ ) were used in channel engineering to form a retrograde

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2002AA1Z1580) and the National Natural Science Foundation of China (No. 60576051)

<sup>†</sup> Corresponding author. Email: lijunfeng @ime. ac. cn Received 6 December 2005, revised manuscript received 15 May 2006

doping profile for the purpose of properly adjusting threshold voltage and suppressing short-channel effects (SCE). The doping profile, obtained with

| • LOCOS isolation                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\rm T}$ -adjusting & anti-punchthrough implanting:<br>BF <sub>2</sub> <sup>+</sup> /80 keV/2×10 <sup>12</sup> cm <sup>-2</sup> /7°+B <sup>+</sup> /45 keV/7×10 <sup>12</sup> cm <sup>-2</sup> /7° |

| Gate stack patterning: 6 nm SiON/250 nm poly-silicon                                                                                                                                                  |

| 4 LDD implanting: As <sup>+</sup> /5keV//3×10 <sup>14</sup> cm <sup>-2</sup> /7°                                                                                                                      |

| TEOS oxide sidewall 200nm                                                                                                                                                                             |

| Deep S/D implanting. $As^+/25 \text{ keV}/5 \times 10^{15} \text{ cm}^{-2}/7^{\circ}$                                                                                                                 |

| <b>♀</b> RTA. 1015℃,6s                                                                                                                                                                                |

| <b>d</b> TiSi <sub>2</sub> salicidation                                                                                                                                                               |

Fig. 1 Process flow for 0. 18µm RF nMOSFET

the TSUPREM simulator<sup>[12]</sup>, is shown in Fig. 2. Our use of the e-beam direct-writing technique in combination with wafer pretreatment in plasma of CF<sub>4</sub> is a key for the patterning of the 0. 18 $\mu$ m gate, as shown in the inset (a) of Fig. 2. A shallow source/drain (S/D) extension junction with sufficiently high doping is indispensable for slight SCE (short channel effects) and low series S/D resist-

Fig. 2 Simulated doping profiles Insets are SEM image of 0.  $18\mu$ m gate line (a) and multi-finger gate structure (b).

ance ,which were obtained by low energy ,mediumdose As implantation followed by typical heavydose ,deep S/D As implantation and RTA (rapid thermal annealing). Ti-salicide with a Ge PAI (preamorphous implant) was used to reduce the parasitic resistance of the gate ,drain ,and source electrodes<sup>[11]</sup>. Note that the Ge PAI can suppress the TiSi<sub>2</sub> narrow line effects since it is the key factor in reducing the sheet resistances , especially for the 0. 18µm gate. Additionally ,for the layout ,as a typical RF MOSFET gate structure , the multi-fingergate pattern, which is shown in the inset (b) of Fig. 2, was used to further reduce the gate parasitic series resistance.

## **3** Results and discussion

The DC characteristics of the fabricated devices were measured with an HP4145 semiconductor parameter analyzer, and the RF S-parameter was measured by an HP8510C vector network analyzer connected to a Cascade Microtech Summit 9000 probe station with ground-signal-ground (GSG) pattern probes. The Y parameters (converted from the measured S parameters) of the open patterns were subtracted from those of the DUT (device under test) in order to extract the parasitics inserted by the probes and the pads to a certain degree<sup>[13]</sup>.

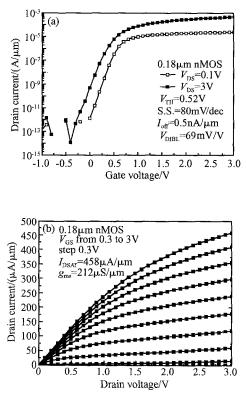

The transfer characteristics of the 0.18 $\mu$ m nMOSFET, under 0.1 and 3V drain biases, are shown in Fig. 3 (a). A threshold voltage of 0.52V is obtained ,which is moderate for operation with a 3V supply voltage. The other parameters extracted from this figure include the sub-threshold swing of 80mV/dec, the drain-induced-barrier-lowering

Fig. 3 DC characteristics of 0. 18µm RF nMOSFET (a) Transfer characteristics; (b) Output characteristics

(DIBL) factor of 69mV/V, and the off-state current of 0.  $5nA/\mu m$ . These parameters show that the SCE are well controlled by the dual implant approach combined with the LDD structure.

Figure 3 (b) shows the output characteristics of the device. For operation with 3V supply voltage the saturation drive current of 458µA/µm and the saturation transconductance of  $212\mu S/\mu m$  are obtained, which are high enough for the 6nm gate oxide. Clearly, higher drive current and transconductance can be achieved by thinning the gate oxide ,which is typically 3nm for 0. 18µm technology in foundry services. Additionally, extrapolating the source-to-drain resistance  $(R_{DS})$  of a group of devices with different gate lengths to zero gate length, an extracted parasitic S/D series resistance of ~259  $\cdot\mu$ m is obtained ,which is ~ 30 % larger than the prediction for high performance MOS-• $\mu$ m) defined by ITRS 2003<sup>[1]</sup>. FETs (< 200)Further improvement may be achieved by adjusting the LDD extension structure (length and doping) or adopting advanced salicidation technologies, such as Ti/ Co-, Co-, and Ni-salicidation<sup>[11,14]</sup>.

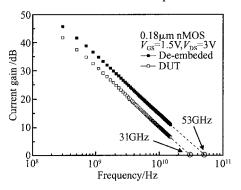

Extrapolated cutoff frequencies  $(f_T)$  are shown in Fig. 4. The extrapolation is from the maximum available frequency of 15 GHz and along the dashed line with the slope of - 20dB/dec. The de-embedded and DUT cutoff frequencies are 53

Fig. 4 Current gain versus frequency of  $0.18\mu$ m nMOSFET

and 31 GHz, respectively. This indicates that the deembedding approach is absolutely indispensable for the accurate characterization of RF devices on lossy silicon substrates. The 53 GHz cutoff frequency is comparable to state-of-the-art 0. 18 $\mu$ m RF CMOS technology<sup>[2,4]</sup>. However, it should be noted that there is still room for improvement of cutoff frequency since the S/D series resistance could be further reduced as mentioned above.

## 4 Conclusion

In this paper, the structure and process of a 0. 18µm nMOSFET have been proposed for RF applications. The device is fabricated with a simple process flow and demonstrates excellent DC characteristics and the high cutoff frequency of 53 GHz, which is comparable to current RF CMOS technologies provided by mainstream foundries. This device is promising for multi-GHz RF applications.

Acknowledgements The authors would like to thank all the process researchers and engineers in the Laboratory of Deep Sub-Micron Integrated Circuits of the Institute of Microelectronics at the Chinese Academy of Sciences (IMECAS) for their support and assistance in device fabrication; Dr. Liu Ming, Mr. Niu Jiebing in IMECAS, for their help in e-beam direct-writing patterning and SEM analysis; Ms. Wu Jin, Ms. Liang Xiaoxin at IMECAS, Prof. Lin Chenglu, Prof. Sun Xiaowei, Ms. Zhang Dan, and Ms. Luo Suhua at the Shanghai Institute of Microsystem and Information Technology (SIMIT), for their help in RF measurements.

#### References

- [1] http://www.public.itrs.net/Files/2003ITRS/Home2003. htm

- [2] http://www.charteredsemi.com/technology/rf\_cmos.asp

- [3] http: www.tsmc.com/english/b\_technology/b01\_platform/b01030\_ms.htm

- [4] http://www.umc.com/english/process/1.asp

- [5] http://www.smics.com/website/en/Version/Technology/ mixed Signal CMOS.htm

- [6] http://www.jazzsemi.com/process\_technologies/msa.shtml

- [7] http://www.gsmcthw.com/enhtml/technology.jsp?page\_ type = 18 &id = 18

- [8] Li Junfeng, Yang Rong, Zhao Yuyin, et al. 0. 25µm SOI RF nMOSFETs depleted partially. Chinese Journal of Semiconductors, 2004, 25 (9):1061

- [9] Yang Rong, Qian He, Li Junfeng, et al. SOI technology for radio frequency integrated circuits applications. IEEE Trans Electron Devices, 2006, 53(6):1310

- [10] Xu Qiuxia, Qian He, Yin Huaxiang, et al. High performance 70nm CMOS devices. Chinese Journal of Semiconductors, 2001,22(2):134

- [11] Xu Qiuxia, Qian He, Yin Huaxiang, et al. The investigation of key technologies for sub-0. 1-µm CMOS device fabrication. IEEE Trans Electron Devices, 2001, 48(7):1412

- [12] Avanti ! Company. TMA Tsuprem User 's Manual. Version 2000.4,2000

- [13] Koutsoyannopoulos Y K, Papananos Y. Systematic analysis

# 截止频率 53 GHz 的高性能 0.18µm 射频 nMOSFET<sup>\*</sup>

#### 杨荣 李俊峰<sup>†</sup> 徐秋霞 海潮和 韩郑生 钱 鹤

(中国科学院微电子研究所,北京 100029)

摘要: 阐述了 0.18µm 射频 nMOSFET 的制造和性能.器件采用氮化栅氧化层/多晶栅结构、轻掺杂源漏浅延伸结、 倒退的沟道掺杂分布和叉指栅结构.除 0.18µm 的栅线条采用电子束直写技术外,其他结构均通过常规的半导体制 造设备实现.按照简洁的工艺流程制备了器件,获得了优良的直流和射频性能:阈值电压 0.52V,亚阈值斜率 80mV/dec,漏致势垒降低因子 69mV/V,截止电流 0.5nA/µm,饱和驱动电流 458µA/µm,饱和跨导 212µS/µm (6nm 氧化层,3V 驱动电压)及截止频率 53GHz.

关键词:结构;工艺;射频;nMOSFET EEACC:2550;2560R 中图分类号:TN385 文献标识码:A 文章编号:0253-4177(2006)08-1343-04

Digital Signal Processing, 2000, 47(8):699

[14] Iwai H, Ohguro T, Ohmi S. NiSi salicide technology for scaled CMOS. Microelectron Eng, 2002, 60:157

<sup>\*</sup>国家高技术研究发展计划(批准号:2002AA1Z1580)和国家自然科学基金(批准号:60576051)资助项目

<sup>†</sup> 通信作者. Email:lijunfeng@ime.ac.cn 2005-12-06 收到,2006-05-15 定稿