# A Low Noise, 1. 25 Gb/s Front- End Amplifier for Optical Receivers<sup>\*</sup>

Xue Zhaofeng, Li Zhiqun<sup>†</sup>, Wang Zhigong, Xiong Mingzhen, and Li Wei

(Institute of RF- & OEICs, Southeast University, Nanjing 210096, China)

**Abstract :** This paper presents a low noise ,1. 25 Gb/s and 124dB front-end amplifier that is designed and fabricated in 0. 25 $\mu$ m CMOS technology for optical communication applications. Active inductor shunt peaking technology and noise optimization are used in the design of a trans-impedance amplifier, which overcomes the problem of inadequate bandwidth caused by the large parasitical capacitor of the CMOS photodiode. Experimental results indicate that with a parasitical capacitance of 2pF, this circuit works at 1. 25 Gb/s. A clear eye diagram is obtained with an input optical signal of - 17dBm. With a power supply of 3. 3V, the front-end amplifier consumes 122mW and provides a 660mV differential output.

Key words:front-end amplifier;TIA;shunt peaking;active inductorEEACC:1220Document code:AArticle ID:0253-4177(2006)08-1373-05

## 1 Introduction

Front-end amplifiers are key components in optical communication systems. A front-end amplifier includes a trans-impedance amplifier (TIA) and a limiting amplifier (LA). The task of the TIA is to transform a current signal from a photodiode (PD) into a voltage signal and amplify it. The task of the LA is to further amplify this small voltage signal into a large, invariable amplitude voltage to drive a time recovery circuit and data decision circuit. The performance of the front-end amplifier influences the optical receiver directly. CMOS technology has the merits of low power consumption, low cost, high integration, and mixed integration. PDs fabricated in CMOS technology have greater area than PDs fabricated in GaAs technology and achieve a capacitance of about 2pF. Considering the monolithic integration of PDs with front-end amplifiers, this paper designs front-amplifiers for PDs with large capacitance.

# 2 Architecture of the front-end amplifier

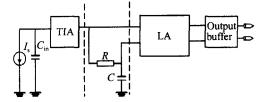

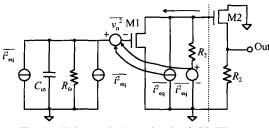

Figure 1 shows a schematic diagram of the front-end amplifier, including the TIA, LA, and an

output buffer (OB). It is well known that tradeoffs between bandwidth and PD capacitance are inevitable and crucial in a conventional-source (CS) TIA. Considering that the capacitance of a CMOS photodiode is 2p F, which is much higher than the 0. 5p F of GaAs photodiodes, an improved CS TIA using active inductor shunt peaking technology is adopted to extend the bandwidth. It introduces a larger feedback resistance, which increases the trans-impedance gain and decreases the input-referred noise current of the TIA at a bit rate of 1. 25 Gb/ s. Thus this improved CS TIA has a wide band, low noise, and high gain.

Fig. 1 Diagram of front-end amplifier

The RC network can hold the same operating voltage on the two differential inputs of the LA and input the single-ended high frequency signal from the TIA into the LA. The LA has a differential gain of 50dB and full differential structures to reduce the negative influence of the power supply

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2002AA312240) † Corresponding author. Email : zhiqunli @seu. edu. cn

Received 6 November 2005, revised manuscript received 24 February 2006

## **3** The Trans-impedance amplifier

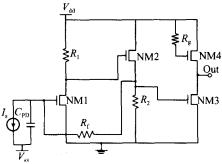

For a conventional CS TIA ,the total input capacitance can be expressed as  $C_{in} = C_{PD} + C_t + C_{para}$ , including the capacitance  $C_{PD}$  of the PD, the input capacitance  $C_t$  of the amplifier and the parasitic capacitance C<sub>para</sub>. The - 3dB bandwidth of the TIA is given by  $f_{-3dB} = 1/2$   $R_{in} C_{in}$ . CPD plays an important role in achieving the bandwidth of the CS TIA ,because the bigger  $C_{PD}$  is the smaller the bandwidth of the TIA will be. Assuming that  $R_{in} = 100$ ,  $f_{-3dB}$ = 1 GHz , and  $C_{\rm in}$  = 1/2  $R_{\rm in} f_{-3dB}$  , the  $C_{\rm in}$  of the CS TIA can be simply calculated to be 1.6pF, which is less than the 2pF of the CMOS PD. Therefore the structure of a conventional CS TIA is not appropriate. In order to meet the requirements of bandwidth and noise performance simultaneously, a new CS TIA structure using active inductor shunt peaking technology is proposed. It is shown in Fig. 2.

Fig. 2 Diagram of improved CS TIA

#### 3.1 Active inductor shunt peaking

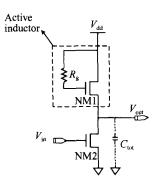

The bandwidth of the amplifier can be enhanced by the inductive load in the second CS amplifier stage (see Fig. 2). This well-known technique, called shunt peaking, extends the bandwidth by about 70 % in the frequency response. The inductive load can be implemented with a spiral inductor or an active inductor (Fig. 3)<sup>[2]</sup>. It is difficult to design a spiral inductor with a high inductance (e.g. 35nH) while keeping the self-resonance well outside the pass band (1 GHz). Furthermore, a spiral inductor is small and can operate at frequencies up to about 8. 1 GHz.

Fig. 3 Active inductor shunt peaking

The equivalent  $L^{[2]}$  and  $R^{[2]}$  of the active inductor are expressed as follows:

$$L = \frac{\frac{R_{g}}{T} - \frac{1}{g_{m-T}}}{1 + (\frac{1}{T})^{2}} = \frac{R_{g}}{T}$$

(1)

$$R = \frac{\frac{1}{g_{m}} + R_{g}(\frac{1}{T})^{2}}{1 + (\frac{1}{T})^{2}} = \frac{1}{g_{m}}$$

(2)

The *L* of the active inductor increases with  $R_g$ , but this increase is restricted. To avoid undesirable peaking in the frequency response, *L* should be set to  $L_{opt} = 0.4 R^2 C_{tot}^{[3,4]}$ . From Eqs. (1) and (2), when the nMOS is set at a certain DC drop and width the optimal value of  $R_g$  can be expressed as

$$R_{gopt} = 0.4 R^2 C_{tot}$$

$T = 0.4 \times \frac{1}{T} \times \frac{C_{tot}}{C_{gs}^2}$  (3)

where  $C_{\text{tot}}$  is the equivalent output capacitor as shown in Fig. 3, and  $C_{\text{tot}} = C_{\text{Line}} + C_{\text{db2}} + C_{\text{sb1}}$ , with the assumption that  $C_{\text{tot}} = C_{\text{gs1}}$ . Thus,

$$R_{gopt} = \frac{0.4}{T C_{gsl}}$$

(4)

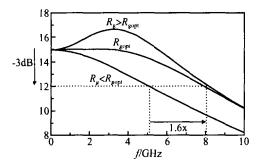

We set the gate width of NM1 to  $6\mu$ m, after obtaining  $C_{gs1}$  8. 5f F, and  $R_{gopt}$  2. 5k by calculation. Figure 4 shows the inductive bandwidth extension of the active inductor. The shunt peaking with  $R_{gopt} = 2$ . 5k extends the bandwidth by about 60 % over the case without shunt peaking (i. e.  $R_g = 0$ ).

#### 3.2 Equivalent input noise current of the TIA

The equivalent circuit of the CS TIA is shown in Fig. 5, where  $\overline{i_{eq}^2}$  is the equivalent input noise current of the CS TIA,  $\overline{i_{Rfs}^2} = 4kT/R_{fs}$  is the parallel current noise of  $R_{fs}$ ,  $\overline{i_n^2} = 4kT$  gm is the channel current noise of M1, and  $\overline{v_{R1}^2} = 4kTR_1$  is the thermal

Fig. 4 Bandwidth extension by active inductor

Fig. 5 Noise equivalent circuit of CS TIA

voltage noise of  $R_1$ . Since M2 and  $R_2$  contribute less noise to  $\overline{i_{eq}^2}$ , they can be ignored. Note that  $i_n^2$ and  $\overline{v_{R_1}^2}$  can be transformed to a gate series voltage noise  $\overline{v_n^2}^{[1]}$ ,

$$\overline{v_n^2} = \frac{4 \, kT}{g_m} + \frac{4 \, kT}{g_m^2 \, R_1}$$

(5)

The total input-inferred noise current density is given by

$$\overline{\mathbf{i}_{eq}^{2}} = \frac{4\,kT}{R_{fs}} + \overline{\mathbf{v}_{n}^{2}} \times \left| \frac{1}{R_{fs}} + sC_{in} \right|^{2}$$

$$= \frac{4\,kT}{R_{fs}} + \frac{4\,kT}{R_{1}\,g_{m}^{2}\,R_{fs}^{2}} + \frac{4\,kT}{g_{m}\,R_{fs}} + \frac{4\,kT}{R_{1}} + \frac{4\,kT}{g_{m}^{2}\,R_{fs}^{2}} + \frac{4\,kT}{g_{m}^{2}\,R_{fs}^{2}} + \frac{4\,kT}{R_{1}} + \frac{2}{R_{1}} + \frac{2}{R_{1}$$

From Eq. (6), we know that total input-inferred noise current correlates with  $R_{fs}$ ,  $R_1$ ,  $g_m$ ,  $C_{pd}$ , and  $C_{gs}$ .  $f_T$  is the unity current-gain frequency. When the bandwidth of the TIA is 1GHz,  $R_{fs}$ and  $R_1$  should be made as large as possible to reduce the total noise. At high frequencies, the last term of Eq. (6) becomes dominant. Since  $C_{pd}$ 2pF, the  $C_{gs}$  of M1 should be enlarged by increasing the gate width of M1 in order to decrease the noise. However, the increase of the gate width of M1 augments  $g_m$ , which enlarges the last term of Eq. (6). Therefore, there are some trade-offs between  $C_{gs}$  and  $g_m$ , and an optimum gate width of NM1 exists.

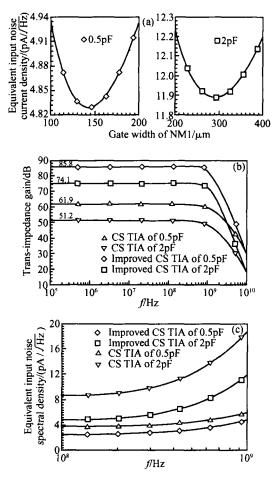

#### 3.3 Simulation results of the TIA

The TIA is simulated using Cadence Spectre in 0.  $25\mu$ m CMOS technology. The simulated results are shown in Figs. 6 (a) ,(b) ,and (c).

First ,when  $C_{pd}$  2p F ,Figure 6 (a) shows that the equivalent input noise current density varies with the NM1 gate width of the improved CS TIA (Fig. 2). The minimum input noise current density of 11. 89pA/  $\sqrt{\text{Hz}}$  can be obtained with the optimum width of 284µm. The frequency responses of the improved CS TIA and the conventional CS TIA are shown in Fig. 6 (b) , where the bandwidth of each is 1 GHz and their trans-impedance gains are 74dB ( $R_f = 1.5$  K) and 51dB ( $R_f = 450$ ) ,respectively. Their equivalent input noise spectral densities at 1 GHz are 11. 8 and 18. 81pA/ Hz ,respectively ,as shown in Fig. 6 (c).

Fig. 6 Spectral simulation results (a) Equivalent input noise current density versus gate width of NM1; (b) Simulated frequency responses; (c) Equivalent input noise spectral density

Second, when  $C_{pd} = 0.5 \text{ pF}$ , Figure 6 (a) also shows that the minimum input noise current density of 4.  $83\text{pA}/\sqrt{\text{Hz}}$  can be obtained with the optimum width of 145µm for M1. The trans-impedance gain of the improved CS TIA and the conventional CS TIA are 85. 8dB ( $R_f = 3.75 \text{ K}$ ) and 51dB ( $R_f =$ 1.5 K), respectively, as shown in Fig. 6 (b). Their equivalent input noise spectral density at 1 GHz are 4. 83 and 6. 03pA/ $\sqrt{\text{Hz}}$ , respectively, as shown in Fig. 6 (c).

Typical simulation results are listed in Table 1, which shows that the improved CS TIA has better performance than the conventional CS TIA for PDs with a high or low capacitance.

| ruoro i Typicul simulated periormanee parameters |                                 |                                  |                                                                                       |

|--------------------------------------------------|---------------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| Circuits                                         | <i>C</i> <sub>pd</sub><br>/ p F | Trans-impedance<br>gain/ (dB · ) | $\frac{\overline{i_{eq}^2}(1 \text{GHz})}{\frac{1}{2} (p \text{A}/\sqrt{\text{Hz}})}$ |

| Conventional                                     | 0.5                             | 61.9                             | 6.03                                                                                  |

| CS TIA                                           | 2                               | 51.2                             | 18.81                                                                                 |

| Improved                                         | 0.5                             | 85.8                             | 4.8                                                                                   |

| CS TIA                                           | 2                               | 74.1                             | 11.89                                                                                 |

Table 1

Typical simulated performance parameters

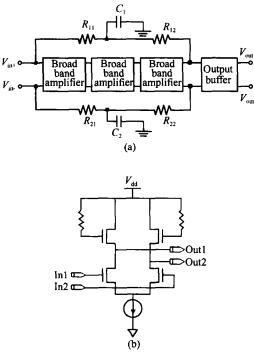

## 4 Limiting amplifier

Figure 7 (a) shows the LA structure, which contains three broad-band amplifiers, an output buffer ,and a DC feedback network. In order to im-

prove the bias stability and reduce the crosstalk among stages ,we adopt direct coupling between staFig. 7 (a) Limiting amplifier structure; (b) Broadband amplifier

ges and provide independent bias for different stages. Figure 7 (b) shows the circuit of each broadband amplifier<sup>[4]</sup>.

Due to the high-gain and direct coupling, a small voltage offset at the input causes the output stage to saturate and even makes the circuit lose its function of limiting amplifying. The DC feedback networks, which include  $R_{11}$ ,  $R_{12}$ ,  $R_{21}$ ,  $R_{22}$ ,  $C_1$ , and  $C_2$ , make the circuit stable.

#### 5 Measured results

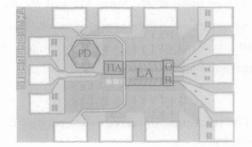

The chip has dimensions of 0.666mm  $\times$  0.470mm = 0.313mm<sup>2</sup> (Fig. 8). Together with a pulse pattern generator (Advantest D3186), a digital sampling scope (Agilent 86100A), a cascade probe platform, and 40 GHz microwave probes, this chip is determined to achieve good performance by probe testing. With a 3.3V power supply, the front-end amplifier consumes 122mW.

Fig. 8 Microphotograph of the front-end amplifier

#### 5.1 Voltage measurements

Figure 9 shows the measured eye diagrams of the front-end amplifier with a 1. 25 Gb/s  $2^{31}$  - 1

Fig. 9 Eye diagrams at a bit rate of 1. 25 Gbps (a) Input voltage of 1. 3mVpp; (b) Input voltage of 1. 1Vpp pseudorandom bit sequence (PRBS) signal at input voltage amplitudes of 1. 3mVpp and 1. 1Vpp. The single output voltage swings are 334 and 329mV, respectively. The RMS jitters are 15 and 10ps. The dynamic range of the input voltage is 1.  $3mV \sim$ 1. 1V.

#### 5.2 Optical measurements

For optical measurements, a lightwave multimeter (Agilent 83430A) and an attenuator (Agilent 8163B) are used as a light source. A p-i-n photodiode is used as an optical detector with a responsivity of 0. 8A/W. A 1. 25 Gb/ s  $2^{31}$ -1 PRBS signal is used as the modulation signal. The sensitivity of the front-end amplifier is estimated to be -17dBm, with a photodiode output current of 15. 8µ A. Figure 1 0 shows eye diagrams at optical

Fig. 10 Eye diagrams with optical signal input at  $-15dBm(23.3\mu A)$  (a) and  $-17dBm(15.8\mu A)$  (b)

signal inputs of -15dBm (23. 3µA) and -17dBm. The single output voltage swings are 326 and 325mV, respectively. The RMS jitters are 15 and 10ps, respectively.

## 6 Conclusion

This paper presents a front-end amplifier designed and fabricated in 0. 25µm CMOS technology for optical communications. Active inductor shunt peaking technology and noise optimization are used in the design of the improved CS TIA ,which overcomes the inadequate bandwidth problem caused by the large parasitical capacitance of the CMOS photodiode and makes monolithic integrated circuits with CMOS photodiodes into reality.

#### References

- Razavi B. Design of analog CMOS integrated circuits. McGraw-Hill ,2001

- [2] Hu Yan, Wang Zhigong, Feng Jun. 5 Gb/s0.25µm COMS limiting amplifier. Chinese Journal of Semiconductors, 2003,24(12):1250

- [3] Lee T H. The design of CMOS radio-frequency integrated circuits. Beijing: Publishing House of Electronics Industry, 2002:146

- [4] Sackinger E, Fischer W C. A 3-GHz 32-dB CMOS limiting amplifier for SONET OC-48 receivers. IEEE J Solid-State Circuits ,2000 ,35(12) :1884

## 低噪声 1. 25 Gb/ s 光接收机前端放大器 \*

薛兆丰 李智群 王志功 熊明珍 李 伟

(东南大学射频与光电集成电路研究所,南京 210096)

摘要:设计并实现了一种基于 TSMC 0. 25µm CMOS 工艺的低噪声、1. 25 Gb/s 和 124dB 的光接收机前端放大器.跨阻放大器设计采用了有源电感并联峰化和噪声优化技术,克服了 CMOS 光检测器大寄生电容造成的带宽不够的问题.测试结果表明,在 2pF 的寄生电容下,前端放大器工作速率达到了 1. 25 Gb/s,在光功率为 - 17 dB m 的光 信号输入下得到了清晰的眼图.芯片采用 3. 3V 电压供电,功耗为 122 mW,差分输出电压幅度为 660 mV.

关键词:前端放大器;跨阻放大器;并联峰化;有源电感

EEACC: 1220

中图分类号:TN72

文献标识码:A

文章编号: 0253-4177(2006)08-1373-05

†通信作者. Email :zhiqunli @seu.edu.cn 2005-11-06 收到,2006-02-24 定稿

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2002AA312240)