| Citation: |

Zhongjian Jiang, Zuochang Ye, Yan Wang. Efficient SRAM yield optimization with mixture surrogate modeling[J]. Journal of Semiconductors, 2016, 37(12): 125001. doi: 10.1088/1674-4926/37/12/125001

Z J Jiang, Z C Ye, Y Wang. Efficient SRAM yield optimization with mixture surrogate modeling[J]. J. Semicond., 2016, 37(12): 125001. doi: 10.1088/1674-4926/37/12/125001.

Export: BibTex EndNote

|

Efficient SRAM yield optimization with mixture surrogate modeling

doi: 10.1088/1674-4926/37/12/125001

More Information-

Abstract

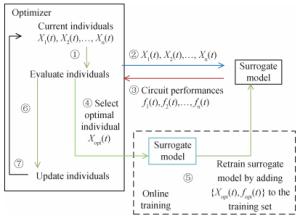

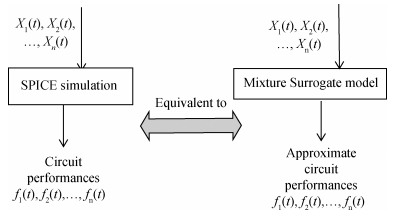

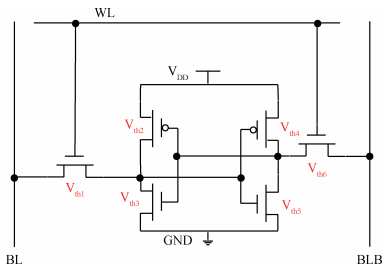

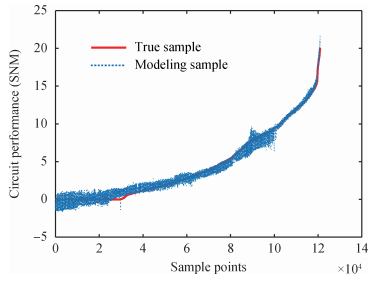

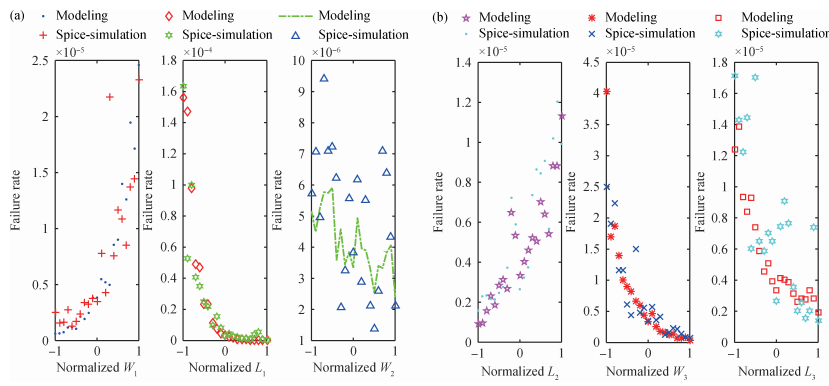

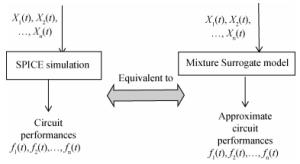

Largely repeated cells such as SRAM cells usually require extremely low failure-rate to ensure a moderate chi yield. Though fast Monte Carlo methods such as importance sampling and its variants can be used for yield estimation, they are still very expensive if one needs to perform optimization based on such estimations. Typically the process of yield calculation requires a lot of SPICE simulation. The circuit SPICE simulation analysis accounted for the largest proportion of time in the process yield calculation. In the paper, a new method is proposed to address this issue. The key idea is to establish an efficient mixture surrogate model. The surrogate model is based on the design variables and process variables. This model construction method is based on the SPICE simulation to get a certain amount of sample points, these points are trained for mixture surrogate model by the lasso algorithm. Experimental results show that the proposed model is able to calculate accurate yield successfully and it brings significant speed ups to the calculation of failure rate. Based on the model, we made a further accelerated algorithm to further enhance the speed of the yield calculation. It is suitable for high-dimensional process variables and multi-performance applications. -

References

[1] Li Xin, Le Jiayong, Pileggi L T. Statistical performance modeling and optimization, Foundations and Trends in Electronic Design Automation, 2006, 1(4): 331 doi: 10.1561/1000000008[2] Hong Xinhong, Pan Liyang, Zhang Wendi, et al. Simulation and research on a 4T-cell based duplication redundancy SRAM for SEU radiation hardening. Journal of Semiconductors, 2015, 36(11): 114003 doi: 10.1088/1674-4926/36/11/114003[3] Luo Yinhong, Zhang Fengqi, Guo Hongxia, et al. Impacts of test factors on heavy ion single event multiple-cell upsets in nanometer-scale SRAM. Journal of Semiconductors, 2015, 36(11): 114009 doi: 10.1088/1674-4926/36/11/114009[4] Niederreiter H. Random number generation and quasi-Monte Carlo methods. Society for Industrial and Applied Mathematics, 1992[5] Yao J, Ye Z, Wang Y. Efficient importance sampling for high-sigma yield analysis with adaptive online surrogate modeling. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2013: 1291 https://www.researchgate.net/publication/260740479_Efficient_Importance_Sampling_for_High-sigma_Yield_Analysis_with_Adaptive_Online_Surrogate_Modeling[6] Basu S, Kommineni B, Vemuri R. Variation-aware macromodeling and synthesis of analog circuits using spline center and range method and dynamically reduced design space. IEEE VLSID, 2009[7] Zhang Moning, Ye Zuochang, Wang Yan. Efficient high-sigma yield analysis for high dimensional problems. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2014: 1 https://www.researchgate.net/publication/269311321_Efficient_high-sigma_yield_analysis_for_high_dimensional_problems[8] Yao Jian, Ye Zuochang, Wang Yan. An efficient SRAM yield analysis and optimization method with adaptive online surrogate modeling. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2015, 23: 1245 doi: 10.1109/TVLSI.2014.2336851[9] Yu Guo, Dong Wei, Feng Zhuo, et al. A framework for accounting for process model uncertainty in statistical static timing analysis. 44th ACM/IEEE Design Automation Conference, 2007, 2007: 829 http://cn.bing.com/academic/profile?id=2107261135&encoded=0&v=paper_preview&mkt=zh-cn[10] Kanj R, Joshi R, Nassif S. Mixture importance sampling and its application to the analysis of SRAM designs in the presence of rare failure events. 43rd ACM/IEEE Design Automation Conference, 2006: 69 http://dl.acm.org/citation.cfm?id=1146930[11] Gong Fang, Yu Hao, Shi Yiyu, et al. Variability-aware parametric yield estimation for analog/mixed-signal circuits: concepts, algorithms, and challenges. IEEE Design & Test, 2014, 31: 6 https://www.researchgate.net/profile/Hao_Yu10/publication/261992925_Variability-Aware_Parametric_Yield_Estimation_for_AnalogMixed-Signal_Circuits_Concepts_Algorithms_and_Challenges/links/00b7d53626068a26fa000000.pdf?disableCoverPage=true[12] Wang J, Yaldiz S, Li X, et al. SRAM parametric failure analysis. 46th ACM IEEE Design Automation Conference, 2009: 496 http://www.docin.com/p-931586118.html[13] Dong Changdao, Li Xin. Efficient SRAM failure rate prediction via gibbs sampling. IEEE Trans Comput-Aid Des Integr Circuits Syst, 2012, 31: 1831 doi: 10.1109/TCAD.2012.2209884[14] Tibshirani R. Regression shrinkage and selection via the Lasso. Journal of the Royal Statistical Society, Series B (Methodological), 1996, 58: 267 http://cn.bing.com/academic/profile?id=2119862467&encoded=0&v=paper_preview&mkt=zh-cn[15] Juan D C, Garg S, Marculescu D. Statistical peak temperature prediction and thermal yield improvement for 3D chip multiprocessors. ACM Transactions on Design Automation of Electronic Systems, 2014, 19: 39 http://dl.acm.org/citation.cfm?id=2633606[16] Gong Fang, Liu Xuexin, Yu Hao, et al. A fast non-Monte-Carlo yield analysis and optimization by stochastic orthogonal polynomicals. ACM Trans Design Automation of Electronic Systems, 2012, 17: 39 http://eda.ee.ucla.edu/pub/J68.pdf[17] Liu B, Messaoudi J, Gielen G. A fast analog circuit yield estimation method for medium and high dimensional problems. Automation & Test in Europe Conference & Exhibition, 2012: 751 http://dl.acm.org/citation.cfm?id=2492896 -

Proportional views

DownLoad:

DownLoad: