| Citation: |

Nan Zhao, Hua Luo, Qi Wei, Huazhong Yang. A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration[J]. Journal of Semiconductors, 2014, 35(7): 075006. doi: 10.1088/1674-4926/35/7/075006

N Zhao, H Luo, Q Wei, H Z Yang. A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration[J]. J. Semicond., 2014, 35(7): 075006. doi: 10.1088/1674-4926/35/7/075006.

Export: BibTex EndNote

|

A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration

doi: 10.1088/1674-4926/35/7/075006

More Information-

Abstract

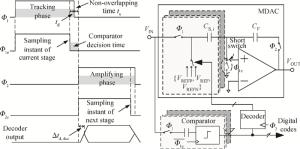

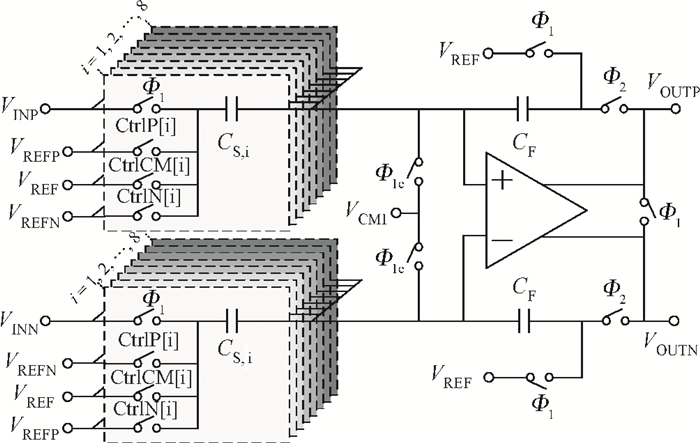

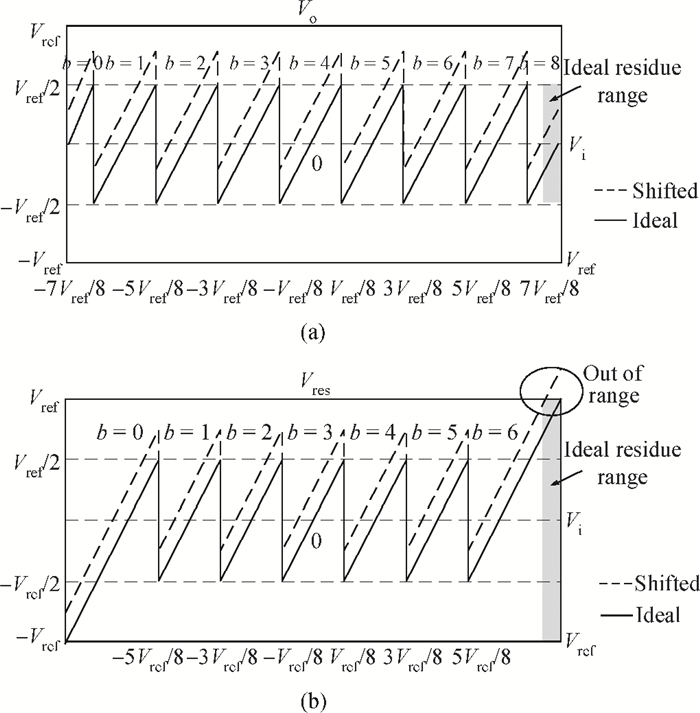

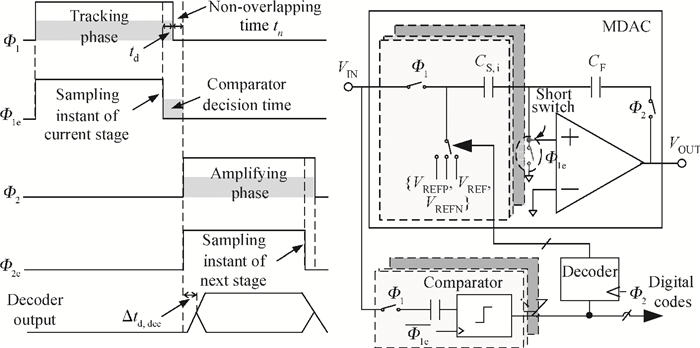

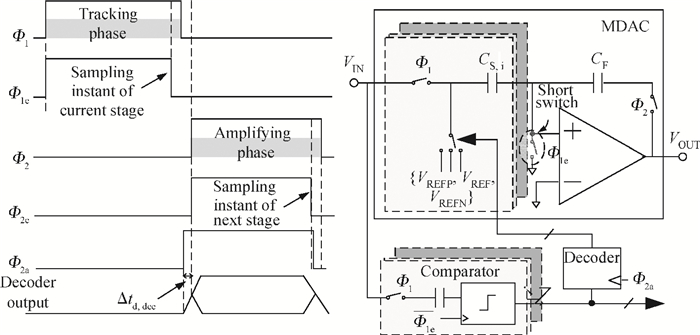

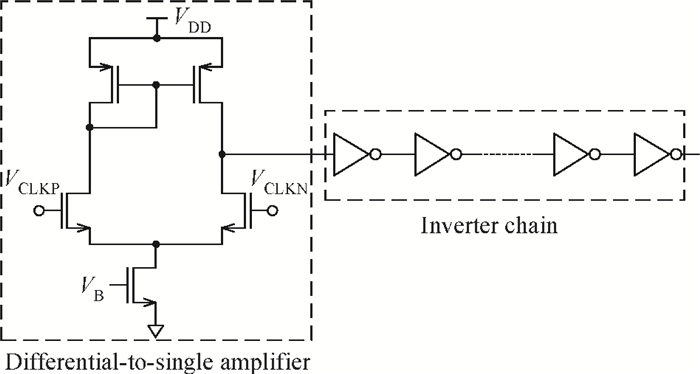

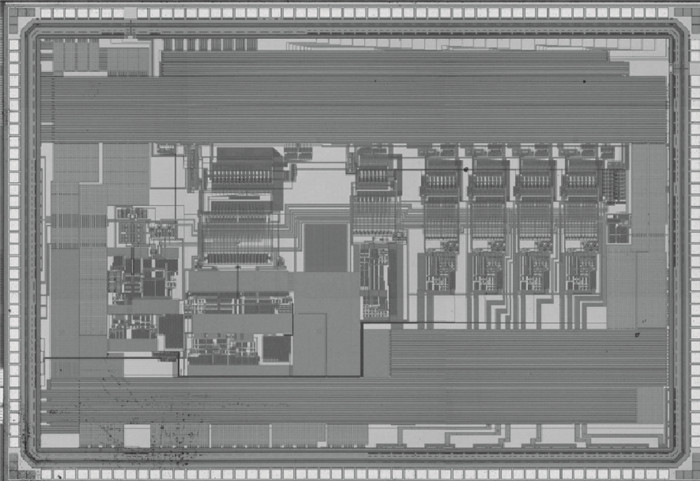

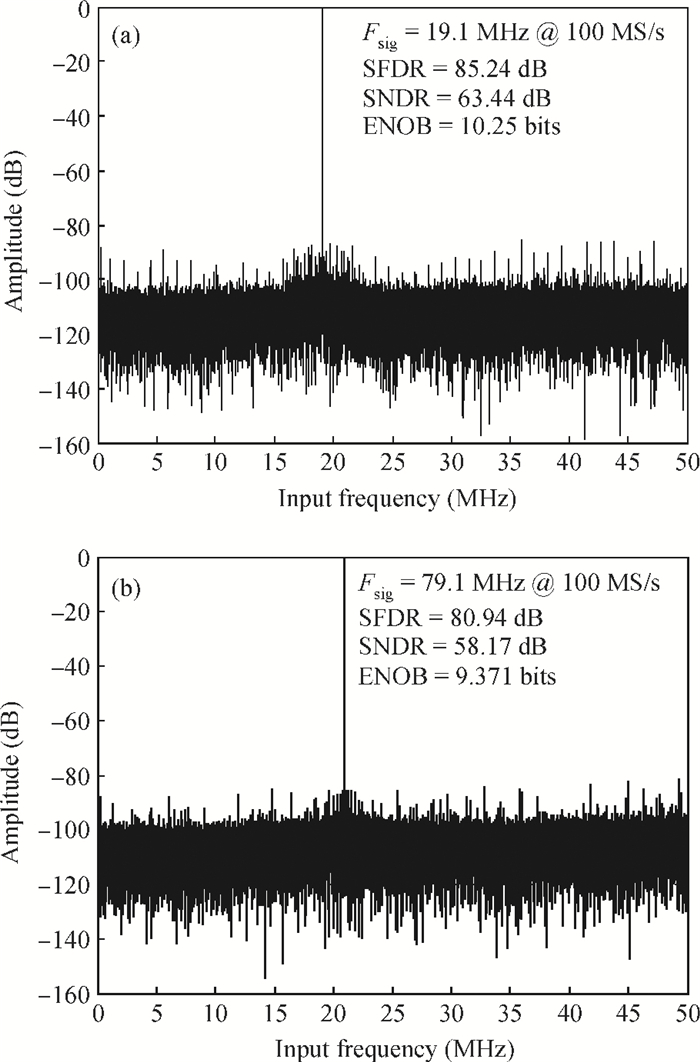

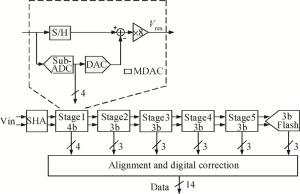

This paper describes a 14-bit 100-MS/s calibration-free pipelined analog-to-digital converter (ADC). Choices for stage resolution as well as circuit topology are carefully considered to obtain high linearity without any calibration algorithm. An adjusted timing diagram with an additional clock phase is proposed to give residue voltage more settling time and minimize its distortion. The ADC employs an LVDS clock input buffer with low-jitter consideration to ensure good performance at high sampling rate. Implemented in a 0.18-μm CMOS technology, the ADC prototype achieves a spurious free dynamic range (SFDR) of 85.2 dB and signal-to-noise-and-distortion ratio (SNDR) of 63.4 dB with a 19.1-MHz input signal, while consuming 412-mW power at 2.0-V supply and occupying an area of 2.9×3.7 mm2.-

Keywords:

- analog-to-digital converter,

- ADC,

- pipeline,

- calibration-free,

- timing,

- clock buffer

-

References

[1] Van de Vel H, Buter B A J, van Der Ploeg H, et al. A 1.2-V 250-mW 14-b 100-MS/s digitally calibrated pipeline ADC in 90-nm CMOS. IEEE J Solid-State Circuits, 2009, 44(4): 1047 doi: 10.1109/JSSC.2009.2014702[2] Cho Y J, Lee K H, Choi H C, et al. A calibration-free 14b 70 MS/s 3.3 mm2 235 mW 0.13μm CMOS pipeline ADC with high-matching 3-D symmetric capacitors. IEEE Custom Integrated Circuits Conference, 2006: 485[3] Daito M, Matsui H, Ueda M, et al. A 14-bit 20-MS/s pipelined ADC with digital distortion calibration. Asian Solid-State Circuits Conference, 2005: 61 http://cat.inist.fr/?aModele=afficheN&cpsidt=18276207[4] Luo L, Lin K, Cheng L, et al. A digitally calibrated 14-bit linear 100-MS/s pipelined ADC with wideband sampling frontend. Proc ESSCIRC, 2009: 472 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=5325956[5] Yang W, Kelly D, Mehr I, et al. A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input. IEEE J Solid-State Circuits, 2001, 36(12): 1931 doi: 10.1109/4.972143[6] Lewis S H, Gray P R. A pipelined 5-Msample/s 9-bit analog-to-digital converter. IEEE J Solid-State Circuits, 1987, 22(6): 954 doi: 10.1109/JSSC.1987.1052843[7] Bardsley S, Dillon C, Kummaraguntla R, et al. A 100-dB SFDR 80-MSPS 14-bit 0.35-μm BiCMOS pipeline ADC. IEEE J Solid-State Circuits, 2006, 41(9): 2144 doi: 10.1109/JSSC.2006.880590[8] Geelen G, Paulus E, Simanjuntak D, et al. A 90 nm CMOS 1.2 V 10 b power and speed programmable pipelined ADC with 0.5 pJ/conversion-step. IEEE International Solid-State Circuits Conference, Digest of Technical Papers, 2006: 782[9] Brunsilius J, Siragusa E, Kosic S, et al. A 16b 80 MS/s 100 mW 77.6 dB SNR CMOS pipeline ADC. IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011: 186[10] Yin Xiumei, Wei Qi, Xu Lai, et al. A low power 12-b 40-MS/s pipeline ADC. Journal of Semiconductors, 2010, 31(3): 035006 doi: 10.1088/1674-4926/31/3/035006[11] Conpration T I. LVDS application and data handbook. 2010[12] Kester W. Analog-digital conversion, analog devices. Section 2. 3. 2004: p. 2. 72, Fig. 2. 81[13] Fan Ye, Cheng Long, Lin Kaihui, et al. An 80-MS/s 14-bit pipelined ADC featuring 83 dB SFDR. Analog Integrated Circuits and Signal Processing, 2010, 63(3): 503 doi: 10.1007/s10470-009-9451-2[14] Cai Hua, Li Ping, Cen Yuanjun, et al. A 14-bit 80 MS/s CMOS ADC with 84.8 dB SFDR and 72 dB SNDR. Journal of Semiconductors, 2012, 33(2): 025012 doi: 10.1088/1674-4926/33/2/025012[15] Reeder R, Green W, Shilito R. Analog-to-digital converter: clock optimization. Analog Dialogue 42-02, Feb. 2008[16] Treichler J, Huang Q. A 11.1-bit ENOB 50-MS/s pipelined A/D converter in 130-nm CMOS without S/H front end. Proc ESSCIRC, 2010: 374 http://ieeexplore.ieee.org/document/5619721/?reload=true&arnumber=5619721&sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A5619583%29%26rowsPerPage%3D100[17] Panigada A, Galton I. A 130 mW 100 MS/s pipelined ADC with 69 dB SNDR enabled by digital harmonic distortion correction. IEEE J Solid-State Circuits, 2009, 44(12): 3314 doi: 10.1109/JSSC.2009.2032637[18] Choi H C, Yoo P S, Ahn G C, et al. A 14b 150 MS/s 140 mW 2.0 mm2 0.13μm CMOS A/D converter for software-defined radio systems. Int J Circ Theor Appl, 2011, 39: 135 doi: 10.1002/cta.v39.2[19] Lee B, Min B, Manganaro G, et al. A 14 b 100 MS/s pipelined ADC with a merged active S/H and first MDAC. ISSCC Digest of Technical Papers, San Francisco, USA, 2008: 248[20] Wang Ke, Fan Chaojie, Zhou Jianjun, et al. A 14-bit 100-MS/s CMOS pipelined ADC with 11.3 ENOB. Journal of Semiconductors, 2013, 34(8): 085015 doi: 10.1088/1674-4926/34/8/085015 -

Proportional views

DownLoad:

DownLoad: