| Citation: |

Yan Lu, Guigang Cai, Junwei Huang. Favorable basic cells for hybrid DC–DC converters[J]. Journal of Semiconductors, 2023, 44(4): 040301. doi: 10.1088/1674-4926/44/4/040301

Y Lu, G G Cai, J W Huang. Favorable basic cells for hybrid DC–DC converters[J]. J. Semicond, 2023, 44(4): 040301. doi: 10.1088/1674-4926/44/4/040301

Export: BibTex EndNote

|

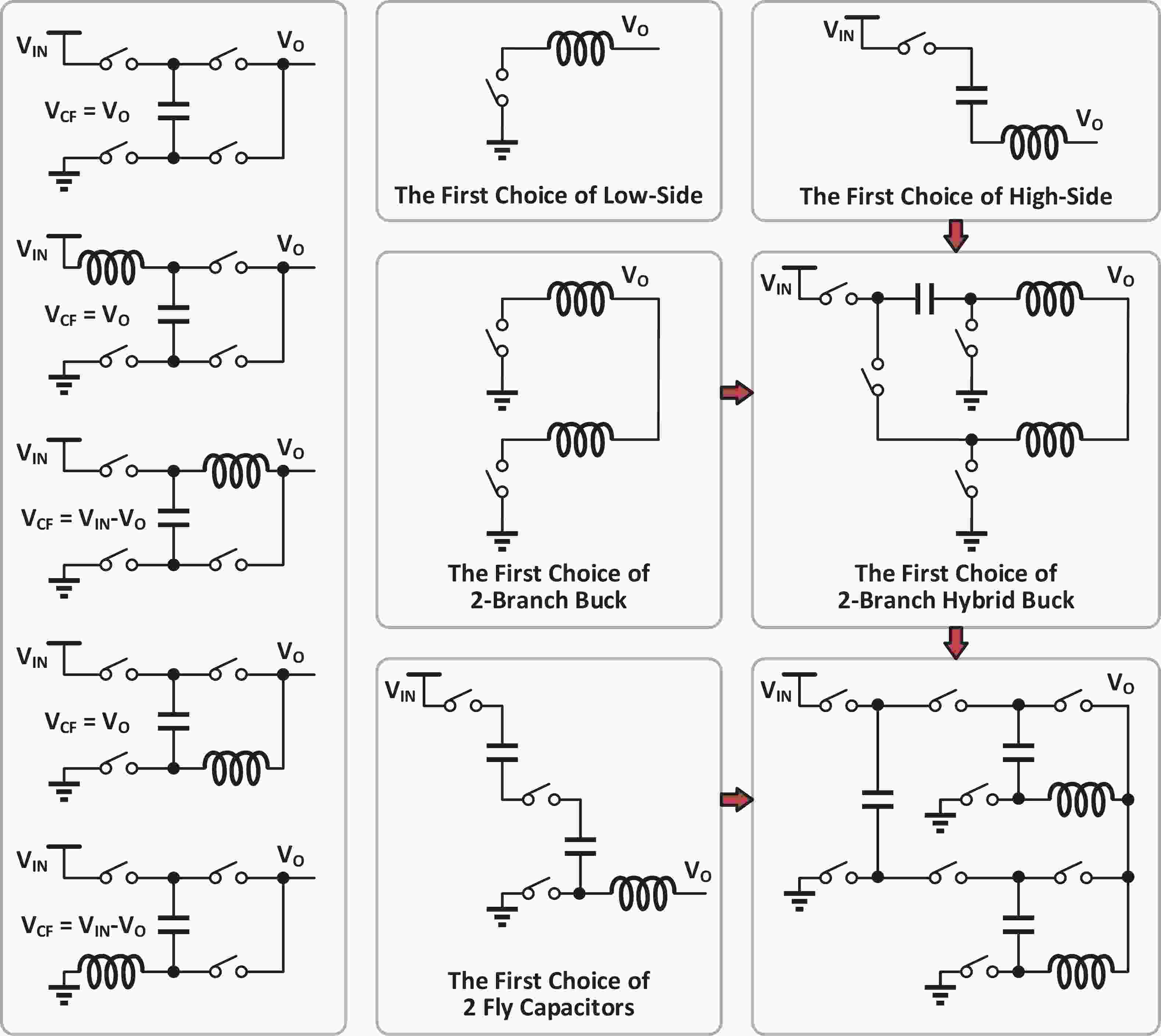

Favorable basic cells for hybrid DC–DC converters

doi: 10.1088/1674-4926/44/4/040301

More Information-

References

[1] Nishijima K, Harada K, Nakano T, et al. Analysis of double step-down two-phase buck converter for VRM. INTELEC 05 - Twenty-Seventh International Telecommunications Conference, 2005, 497 doi: 10.1109/INTLEC.2005.335149[2] Shenoy P S, Lazaro O, Ramani R, et al. A 5 MHz, 12 V, 10 A, monolithically integrated two-phase series capacitor buck converter. 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), 2016, 66 doi: 10.1109/APEC.2016.7467853[3] Abdulslam A, Mercier P P. A continuous-input-current passive-stacked third-order buck converter achieving 0.7W/mm2 power density and 94% peak efficiency. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 148 doi: 10.1109/ISSCC.2019.8662384[4] Hata K, Yamauchi Y, Sai T, et al. 48V-to-12V dual-path hybrid DC-DC converter. 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, 2279 doi: 10.1109/APEC39645.2020.9124077[5] Ye Z C, Abramson R A, Pilawa-Podgurski R C N. A 48-to-6 V multi-resonant-doubler switched-capacitor converter for data center applications. 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), 2020, 475 doi: 10.1109/APEC39645.2020.9124384[6] Xia Z Y, Stauth J. A two-stage cascaded hybrid switched-capacitor DC-DC converter with 96.9% peak efficiency tolerating 0.6V/μs input slew rate during startup. 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, 256 doi: 10.1109/ISSCC42613.2021.9365763[7] Tong Z, Huang J, Lu Y, et al. A 42W reconfigurable bidirectional power delivery voltage-regulating cable. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 192[8] Hardy C, Le H P. A 21W 94.8%-efficient reconfigurable single-inductor multi-stage hybrid DC–DC converter. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 190[9] Renz P, Kaufmann M, Lueders M, et al. A fully integrated 85%-peak-efficiency hybrid multi ratio resonant DC-DC converter with 3.0-to-4.5V input and 500μA-to-120mA load range. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 156 doi: 10.1109/ISSCC.2019.8662491[10] McLaughlin P H, Rentmeister J S, Kiani M H, et al. Analysis and comparison of hybrid-resonant switched-capacitor DC–DC converters with passive component size constraints. IEEE Trans Power Electron, 2021, 36, 3111 doi: 10.1109/TPEL.2020.3017123[11] Chan C H, Cheng L, Deng W, et al. Trending IC design directions in 2022. J Semicond, 2022, 43, 071401 doi: 10.1088/1674-4926/43/7/071401[12] Zhen S W, Yang R, Wu D M, et al. Design of hybrid dual-path DC-DC converter with wide input voltage efficiency improvement. 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021, 1 doi: 10.1109/ISCAS51556.2021.9401442[13] Yang X, Cao H X, Xue C K, et al. An 8A 998A/inch3 90.2% peak efficiency 48V-to-1V DC-DC converter adopting on-chip switch and GaN hybrid power conversion. 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, 466 doi: 10.1109/ISSCC42613.2021.9366005[14] Yang X et al. A 5A 94.5% peak efficiency 9~16V-to-1V dual-path series-capacitor converter with full duty range and low V·A metric. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 196[15] Zeng W, Cai G, Lee C, et al. A 12V-input 1V–1.8V-output 93.7% peak efficiency dual-inductor quad-path hybrid DC–DC converter. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 200[16] Schaef C, Weng S, Choi B, et al. A 93.8% peak efficiency, 5V-input, 10A max ILOAD flying capacitor multilevel converter in 22nm CMOS featuring wide output voltage range and flying capacitor precharging. 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, 146 doi: 10.1109/ISSCC.2019.8662475[17] Wei K, Ramadass Y, Ma D B. A direct 12V/24V-to-1V 3W 91.2%-efficiency tri-state DSD power converter with online VCF rebalancing and In-situ precharge rate regulation. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 190 doi: 10.1109/ISSCC19947.2020.9063087[18] Yamauchi Y, Sai T, Hata K, et al. 0.55 W, 88%, 78 kHz, 48 V-to-5 V fibonacci hybrid DC–DC converter IC using 66 mm3 of passive components with automatic change of converter topology and duty ratio for cold-crank transient. IEEE Trans Power Electron, 2021, 36, 9273 doi: 10.1109/TPEL.2021.3058207[19] Hu T X, Huang M, Lu Y, et al. A 4A 12-to-1 flying capacitor cross-connected DC-DC converter with inserted D>0.5 control achieving >2x transient inductor current slew rate and 0.73 × theoretical minimum output undershoot of DSD. 2022 IEEE International Solid- State Circuits Conference (ISSCC), 2022, 1 doi: 10.1109/ISSCC42614.2022.9731669[20] Ko J Y, Huh Y, Ko M W, et al. A 4.5V-input 0.3-to-1.7V-output step-down always-dual-path DC-DC converter achieving 91.5%-efficiency with 250mΩ-DCR inductor for low-voltage SoCs. 2021 Symposium on VLSI Circuits, 2021, 1 doi: 10.23919/VLSICircuits52068.2021.9492478[21] Cai G G, Lu Y, Martins R P. An SC-parallel-inductor hybrid buck converter with reduced inductor voltage and current. IEEE J Solid State Circuits, 2022, 1 doi: 10.1109/JSSC.2022.3213835[22] Kesarwani K, Sangwan R, Stauth J T. Resonant-switched capacitor converters for chip-scale power delivery: Design and implementation. IEEE Trans Power Electron, 2015, 30, 6966 doi: 10.1109/TPEL.2014.2384131[23] Cai G, Lu Y, Martins R P. A compact 12V-to-1V 91.8% peak efficiency hybrid resonant switched-capacitor parallel inductor (ReSC-PL) buck converter. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 198[24] Yang T H, Wen Y H, Ouyang Y J, et al. A 0.03mV/mA low crosstalk and 185nA ultra-low-quiescent single-inductor multiple-output converter assisted by 5-input operational amplifier for 94.3% peak efficiency and 3.0W driving capability. 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, 267 doi: 10.1109/ISSCC42613.2021.9365976[25] Han H, Ko M W, Cho J H, et al. A monolithic 48V-to-1V 10A quadruple step-down DC-DC converter with hysteretic copied on-time 4-phase control and 2 × slew rate all-hysteretic mode. 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2022, 182 doi: 10.1109/VLSITechnologyandCir46769.2022.9830233[26] Hu T, Huang M, Lu Y, et al. A 12V-to-1V quad-output switched-capacitor buck converter with shared DC capacitors achieving 90.4% peak efficiency and 48mA/mm3 power density at 85% efficiency. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 184[27] Hung W, Chen C, Huang Y, et al. A double step-down dual-output converter with cross regulation of 0.025mV/mA and improved current balance. IEEE International Solid-State Circuit Conference (ISSCC), 2023, 188 -

Proportional views

DownLoad:

DownLoad: