ARTICLES

## Enhancement of refresh time in quasi-nonvolatile memory by the density of states engineering

Zhaowu Tang<sup>1, ‡</sup>, Chunsen Liu<sup>1, 2, ‡, †</sup>, Senfeng Zeng<sup>1</sup>, Xiaohe Huang<sup>1</sup>, Liwei Liu<sup>1</sup>, Jiayi Li<sup>1</sup>, Yugang Jiang<sup>2</sup>, David Wei Zhang<sup>1</sup>, and Peng Zhou<sup>1, †</sup>

<sup>1</sup>State Key Laboratory of ASIC and System, School of Microelectronics, Fudan University, Shanghai 200433, China <sup>2</sup>School of Computer Science, Fudan University, Shanghai 200433, China

**Abstract:** The recently reported quasi-nonvolatile memory based on semi-floating gate architecture has attracted extensive attention thanks to its potential to bridge the large gap between volatile and nonvolatile memory. However, the further extension of the refresh time in quasi-nonvolatile memory is limited by the charge leakage through the p-n junction. Here, based on the density of states engineered van der Waals heterostructures, the leakage of electrons from the floating gate to the channel is greatly suppressed. As a result, the refresh time is effectively extended to more than 100 s, which is the longest among all previously reported quasi-nonvolatile memories. This work provides a new idea to enhance the refresh time of quasi-nonvolatile memory by the density of states engineering and demonstrates great application potential for high-speed and low-power memory technology.

Key words: quasi-nonvolatile memory; refresh time; density of states engineering

**Citation:** Z W Tang, C S Liu, S F Zeng, X H Huang, L W Liu, J Y Li, Y G Jiang, D W Zhang, and P Zhou, Enhancement of refresh time in quasi-nonvolatile memory by the density of states engineering[J]. *J. Semicond.*, 2021, 42(2), 024101. http://doi.org/10.1088/1674-4926/42/2/024101

Supplementary material

Zhaowu Tang and Chunsen Liu contribute equally to this work.

Correspondence to: C S Liu, chunsen\_liu@fudan.edu.cn; P Zhou, pengzhou@fudan.edu.cn

Received 8 JANUARY 2021; Revised 13 JANUARY 2021.

<sup>©2021</sup> Chinese Institute of Electronics

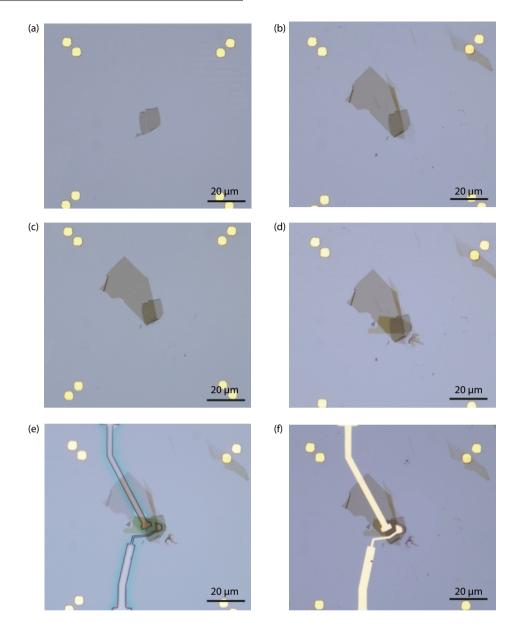

Fig. S1. (Color online) The optical microscope images of the device during the fabrication process. (a–d) The multilayer  $WSe_2$ ,  $MOS_2$ , hBN, and monolayer Gr were transferred on the  $Al_2O_3$ /Si substrate to form the heterostructure based on the dry transfer method using PDMS. (e) The source and drain were patterned by using electron-beam lithography. (f) The Cr/Au films (5 nm/30 nm) were deposited as the source and drain electrode by electron-beam evaporation.

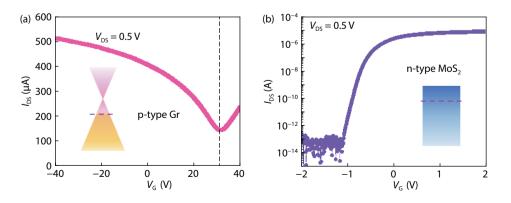

Fig. S2. (Color online) Doping type of Gr and MoS<sub>2</sub>. (a) The transfer characteristic of Gr FETs at  $V_{DS} = 0.5$  V by using 300 nm SiO<sub>2</sub> as the gate dielectric. The Dirac point voltage is around 30 V, indicating that the Gr is p-type. (b) The transfer characteristic of MoS<sub>2</sub> FETs at  $V_{DS} = 0.5$  V by using hBN as the gate dielectric, indicating that the MoS<sub>2</sub> is n-type.

## Z W Tang et al.: Enhancement of refresh time in quasi-nonvolatile memory by the density of states .....