# A Wide-Band Low Noise Amplifier for Terrestrial and Cable Receptions \*

Ma Desheng<sup>1,†</sup>, Shi Yin<sup>1</sup>, and Dai Fa Foster<sup>2</sup>

(1 Artificial Neural Network and High Speed Circuit Laboratory, Institute of Semiconductors,

Chinese Academy of Sciences, Beijing 100083, China)

(2 Department of Electrical & Computer Engineering, Auburn University, Auburn, AL 36849-5201, USA)

Abstract: We present the design of a wide-band low-noise amplifier (LNA) implemented in 0. 35µm SiGe BiC-MOS technology for cable and terrestrial tuner applications. The LNA utilizes current injection to achieve high linearity. Without using inductors, the LNA achieves 0. 1 ~ 1 GHz wide bandwidth and 18. 8dB gain with less than 1. 4dB of gain variation. The noise figure of the wideband LNA is 5dB, and its 1dB compression point is - 2dBm and IIP3 is 8dBm. The LNA dissipates 120mW of power with a 5V supply.

Key words: BiCMOS; wide band; noise figure; linearity; low-noise amplifier; SiGe

EEACC: 1205; 1220; 2570 K

**CLC number:** TN722 **Document code:** A **Article ID:** 0253-4177 (2006) 06-0970-06

# 1 Introduction

In modern integrated RF receivers, the low noise amplifier (LNA) is one of the most critical building blocks since its NF, gain, and linearity contribute significantly to the overall system performance. Wide-band LNAs are used in terrestrial, cable, and other applications in which the ratio between bandwidth and center frequency can be larger than two. For narrow-band LNAs, low noise figure, high gain, and impedance matching can be achieved at relatively low power consumption by exploiting the quality factor of coil-based matching networks[1]. However, this is not practical for wide-band receivers as in cable digital video reception (100 ~ 1000MHz bandwidth in China), satellite reception (950 ~ 2150MHz), and terrestrial reception  $(450 \sim 850 \text{MHz})$  due to the complexity of the required wide-band matching networks. For wide band reception, the wide-band nature of transistors and resistors is typically used. As the demand for increased bandwidth grows, designing wide-band LNAs becomes more difficult.

This paper presents the design of a wide-band LNA implemented in 0. 35µm SiGe BiCMOS technology for digital video broadcasting via cable

(DVB-C) and terrestrial (DVB-T) tuner applications. The LNA achieves an 18. 8dB gain ,5dB noise figure ,and - 2dBm  $P_{1dB}$  over a 0. 1 ~ 1 GHz bandwidth. The LNA dissipates less than 120mW of power with a 5V power supply.

# 2 Design of wide-band L NA circuit

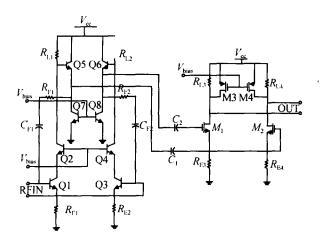

Traditional wide-band LNAs often use a single-end cascode architecture because of its high gain at high-frequency and superior reverse isolation. However, cascode LNAs suffer from limited linearity due to the stacking of two transistors, which reduces the available output swing. On the other hand, a differential architecture relaxes the requirement for a large output swing, which improves the linearity<sup>[2]</sup>. Therefore, a differential architecture is chosen in DVB-C and DVB-T tuner systems that requires high linearity. Figure 1 shows a simplified circuit schematic of the wideband LNA (biasing not shown). In our design, two-stage amplifiers are used.

#### 2.1 First stage amplifier

Low noise figure, high linearity, gain, and input matching are achieved in the first stage of the wide-band LNA. A differential cascode architecture

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 90207008)

<sup>†</sup> Corresponding author. Email:dsma @mail.semi.ac.cn

Fig. 1 Simplified circuit diagram of the wideband LNA

is chosen in the first stage for its excellent gain at high frequency and superior reverse isolation. When analyzing the small signal model of the circuit, a single input is used instead of differential inputs.

The transistors are biased close to the peak  $f_{\rm T}$  to achieve the minimum noise figure. Actually ,the current we chose is a little lower than the peak current because of manufacturing tolerance.

In our design, emitter degeneration resistors  $R_{\rm E}$  are required to meet the high linearity requirements. Using the small signal model, the third-order intercept voltage can be approximately determined by<sup>[3]</sup>

$$V_{IP3} = 2 \frac{k_{I}}{\sqrt{8 k_{3}}}$$

$$= 2 \frac{1}{\sqrt{3}} \times \frac{1}{|R_{E} + r_{e}|} \times \frac{6 I_{c}^{2} |R_{E} + r_{e}|^{5}}{|r_{e}| |2 R_{E} - r_{e}|}$$

$$= 2 \sqrt{2} v_{T} \frac{|R_{E} + r_{e}|^{2}}{\sqrt{r_{e}^{3} |2 R_{E} - r_{e}|}}$$

$$= 2 \sqrt{2} v_{T} \left(\frac{R_{E} + r_{e}}{r_{e}}\right)^{\frac{3}{2}}$$

(1)

where  $v_T$  is the thermal voltage and  $r_e$  and  $R_E$  are the emitter resistances of the transistor and the emitter degeneration resistor respectively. Thus the size of the emitter degeneration resistor  $R_E$  can be obtained from the IP3 requirement by the equation

$$R_{E1} = R_{E2} = R_E = r_e \left( \frac{V_{IP3}}{2 v_T} \right)^{\frac{2}{3}}$$

(2)

The output resistances  $R_{L1}$  and  $R_{L2}$  are used to obtain the first stage gain. Unlike the traditional LNA, the output resistances here must allow the

maximum signal that satisfies the high linearity requirement to pass the first stage without distortion.

For optimum NF, the LNA has to be matched to the optimum source impedance. Shana 'a *et al*. derived the relationship between optimum source impedance and the transistor size as<sup>[4]</sup>

$$R_{S opt} (M) = \frac{1}{MN} \times \left\{ \frac{f_{T}}{f} \left( \frac{n^{2} V_{T}}{2 J_{C}} + (r_{e} + r_{b})_{u} \right) \times \left( \frac{\int_{Q} V_{T}}{V_{T}} (r_{e} + r_{b})_{u} \left( 1 + \frac{f_{T}^{2}}{p_{C} f^{2}} \right) + \frac{n^{2} f_{T}^{2}}{4 p_{C} f^{2}} \right) \right\}$$

$$= \frac{1}{MN} A_{(J_{C}, f)}$$

(3)

where MN represents the device 's size, and  $A_{(J_C,f)}$  is a constant for fixed current density  $J_C$  and frequency f. Unfortunately, it is difficult to match the optimum source impedance to the cable input impedance for wide band. Thus, a shunt feedback has to be used, and then the transistors will have a much smaller bearing on the noise figure than in a tuned LNA, while matching the power.

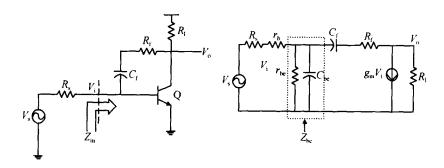

The simple shunt feedback circuit and its small signal model are shown in Fig. 2. Resistor  $R_f$  forms the feedback and capacitor  $C_f$  is added to allow for independent biasing of the base and collector<sup>[3]</sup>. Ignoring the Miller effect and assuming that  $C_f$  is a short circuit  $(1/C_f \ll R_f)$  and  $r_b$  is low compared to  $r_{be}$ , the input impedance can be given by

$$Z_{in} = \frac{Z_{be} (R_f + R_l)}{R_f + R_l + Z_{be} (1 + g_m R_l)}$$

$$R_f \quad Z_{be} \quad \frac{R_f + R_l}{g_m R_l} \quad \frac{R_f + R_l}{g_m R_l}$$

(4)

As a result , compared to the open-loop amplifier input impedance  $Z_{be}$ , the input impedance for the shunt feedback amplifier has less variation over wide band frequency and process. Then wide band match is achieved.

In our design, since the voltage gain is greatly affected by the feedback<sup>[3]</sup>, a buffer between the first stage and the second stage is added. The buffer can also provide some inductance to the input, which tends to make the match better and provide matching between the two stages. As shown in Fig. 1,  $R_{\rm Fl}$  and  $R_{\rm F2}$  are shunt-feedback resistors, and transistors Q5 ~ Q8 make up the buffer. The buffer is assumed to be lossless, and the input impedance

Fig. 2 Simple shunt feedback circuit and small signal model

becomes

$$Z_{in} = Z_{be} \left( 1 + \frac{Z_{be}}{R_{F}} + \frac{g_{m} R_{L} Z_{be}}{R_{F}} \right)^{-1}$$

$$= \frac{R_{F}}{1 + g_{m} R_{L} + \frac{R_{F}}{Z_{be}}} \frac{R_{F}}{g_{m} R_{L}} = \frac{R_{F}}{G_{O}}$$

(5)

Since input impedance of the LNA can be estimated by the feedback resistance  $R_F$  divided by the open loop gain<sup>[5,6]</sup>, the size of the feedback resistance can be determined:

$$Z_{in} \quad \frac{R_F}{G_O} = \frac{R_F}{R_L} \Rightarrow$$

$$R_{FL} = R_{F2} = R_F = \frac{Z_{in} R_L}{R_E + r_e}$$

(6)

With the addition of a buffer ,the voltage gain is no longer affected by the feedback ,and the gain of the first stage can be estimated by the open-loop gain minus the loss in the buffer:

$$G_1 - \frac{R_L}{R_E + r_e} G_{BO}$$

(7)

Here, G<sub>BO</sub> is the voltage gain of buffer.

The feedback also results in the reduction of the role transistors play in determining the gain, and it therefore improves linearity<sup>[3]</sup>, but the presence of feedback resistors  $R_{\rm Fl}$ ,  $R_{\rm F2}$  may degrade the noise.

# 2.2 Second stage amplifier

If the second stage of the common emitter amplifier were not used, the two transistors of the cascode and the emitter resistors in first stage would consume a large voltage, which would limit the headroom. Then it would be impossible to achieve high linearity. This is the reason why it is difficult to achieve high linearity and high gain simultaneously with traditional LNAs. Therefore the common source amplifier is added after first stage, which can broaden the headroom of the cas-

code and provide some gain.

Transistors M1  $\sim$  M4 and some resistors compose the second stage. Then the total voltage gain can be approximated as

$$G_{tot} = G_1 G_2 = \frac{R_L R_L}{(R_E + r_e)(R_E + r_e)} G_{BO}$$

(8)

where  $R_{\rm L}$  and  $R_{\rm L}$  represent the load resistors of the two stages, respectively,  $R_{\rm E}$  and  $R_{\rm E}$  represent the emitter degeneration resistors of the two stages,  $r_{\rm e}$  and  $r_{\rm e}$  are the emitter resistors of the transistors in the two stages, and  $G_{\rm BO}$  is the voltage gain of the buffer.

In the design, the method of current injection is introduced to improve the linearity in the second stage. In high frequency LNAs, the input third-order intercept point (IIP3) is relative to the collector current [4,7]. When a signal passes the first stage, it becomes large. Hence, a large collector current is needed to satisfy the high linearity. However, it is difficult to size the load resistor because of the large current. High linearity can be achieved, but at the expense of gain. The current injection technique is good at solving this problem, but this technique is rarely used in the design of low noise amplifiers because much noise results from adding a current source. However, this method can be used in the second stage. The noise factor of an N-stages connected system is [8]

$$F = F_1 + \frac{F_2 - 1}{A_1} + \frac{F_3 - 1}{A_1 A_2} + \dots + \frac{F_N - 1}{A_1 A_2 \dots A_{N-1}}$$

(9)

where  $F_i$  and  $A_i$  are the noise factor and gain of each stage, respectively. From Eq. (9), it can be seen that the noise of the current source in the second stage will contribute almost nothing to the total system. Thus, in our design, two current sources are added to the load in the second stage, which improves the headroom problem without

adding much noise to the system. In addition, high linearity and high gain can be obtained simultaneously. As shown in Fig. 1,pMOS transistors M3 and M4 make up the current sources, which afford a part of the current from transistors M1 and M2. The simulation result indicates that the NF of the LNA with current injection is 0. 3dB, which is larger than that for the same architecture LNA without current injection. But the IIP3 is increased by 3. 8dB.

#### 3 Measured and simulated results

The wide band LNA is implemented using standard 0. 35µm SiGe BiCMOS technology. All of the simulated results come from a Cadence Spectre simulator.

#### 3.1 Direct current analysis

The measured result shows that the DC power consumption  $P_{dc}$  is  $120 \, \text{mW}$ , which is below the design goal of  $200 \, \text{mW}$ , with a 5V voltage supply. This power consumption is suitable for DVB-C and DVB-T tuner systems, in which power consumption is not a concerned parameter.

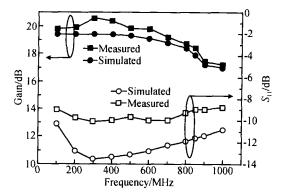

### 3.2 Gain analysis

In the simulation and testing, the frequency of the input signals was from 100M Hz to 1 GHz. The voltage gain ( $G_{00}$ ) here is defined as the output voltage divided by the input voltage. Measured and simulated results of the gain are shown in Fig. 3. The typical voltage gain of the wide band LNA is 18. 8dB with 1. 4dB gain flatness from 100M Hz to 1 GHz. The gain reaches its maximum of 20. 2dB at 300M Hz, and its minimum of 17. 5dB at 1 GHz.

Fig. 3 Measured and simulated results of LNA gain and  $S_{11}$

#### 3.3 S-parameter analysis

S-parameters are tested to verify the input matching. Figure 3 shows the measured and simulated results of  $S_{11}$ . As shown in Fig. 3,  $S_{11}$  is lower than - 9dB throughout the whole frequency band, showing a good broad band input match. But the measured result is a little worse than the simulation due to the parasitic effect on the testing board.

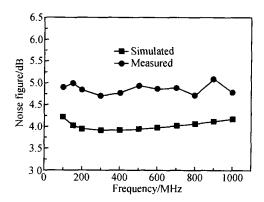

#### 3.4 Noise figure analysis

In Fig. 4, the measured result shows that in the whole frequency band, the typical noise figure (NF) is less than 5dB, which meets the design goal. It can be seen from Fig. 4 that the measured NF is about 1dB more than the simulation due to the noise coming from the balun in the testing.

Fig. 4 Measured and simulated LNA noise figures

#### 3.5 Linearity analysis

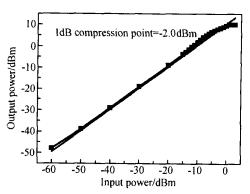

Power measurement is performed at 900M Hz to evaluate the high frequency behavior. As shown in Fig. 5, the measured input power - 1dB compression point is - 2dBm. This is a very high linearity, while its gain is almost 19dB.

Fig. 5 Measured LNA P1dB

# 4 Discussion

The circuit performances presented in this pa-

per are summarized and compared with other academic works and commercial products in Table 1.

| Table 1 | Performance comparison of | academic and commercial | wide-band LNA |

|---------|---------------------------|-------------------------|---------------|

|         | TD1: 1                    | A 1 1                   | ,             |

| ъ.                                   | This work   |                  | Academic work   |                  | Commercial work |

|--------------------------------------|-------------|------------------|-----------------|------------------|-----------------|

| Parameter                            | Design goal | Si Ge LNA        | LNA in Ref. [9] | LNA in Ref. [10] | LNA in Ref.[11] |

| Gain/dB                              | 17          | 18.8             | 18              | 13.7             | 13.4            |

| BW/MHz                               | 100 ~ 1000  | 100 ~ 1000       | 50 ~ 870        | 2 ~ 1600         | 100 ~ 1300      |

| NF/dB                                | 5           | 5                | 5               | 2.5              | 3.8             |

| $S_{11}/d\mathbf{B}$                 | - 10        | - 9              | - 11            | - 8              | - 18            |

| $P_{1 dB} / dB m$                    | 0           | - 2              | - 10            | - 9              | - 22            |

| $I_{\rm CC}$ / mA , $V_{\rm CC}$ / V | 40 ,5       | 24 ,5            | NA ,3.3         | 14 ,2.5          | 8 ,5            |

| Chip/ mm <sup>2</sup>                |             | 0.9 <b>x</b> 0.5 | NA              | 0.3 ×0.25        | NA              |

| Year                                 |             | 2005             | 2005            | 2004             | 2001            |

Compared with other works, the wide-band LNA in this paper has an excellent combination of gain, linearity, noise figure, power consumption and impedance matching. The circuit in Ref. [9] has superior gain, but its linearity would not fit our design goals. The LNAs in Refs. [10] and [11] have good noise figure and lower power dissipation, but poor gain and linearity. The NF of the LNA in this paper is worse than that in Ref. [10] due to the differential architecture, the presence of feedback resistors, and the use of current injection technology. But a 5dB noise figure in the whole frequency band is suitable for DVB tuner systems.

# 5 Conclusion

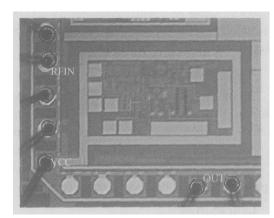

In this paper, a Si Ge wide band LNA with excellent gain, linearity, noise, impedance matching, and bandwidth for DVB-C and DVB-T tuner applications is presented. The wideband LNA achieves an 18. 8dB gain, - 2dBm  $P_{1d}$ B, 8dBm input IP3, and 5dB noise figure, which meet the requirements for DVB-C and DVB-T tuner applications. The proposed current injection demonstrates good performance for high linearity LNA design. The LNA occupies a 0.9mm  $\times$ 0.5mm die area as shown in Fig. 6 and consumes 120mW of power with a 5V supply.

**Acknowledgement** The authors gratefully acknowledge Yan Jun for valuable discussion and technical support.

Fig. 6 Die photo of Si Ge LNA prototype

#### References

- [ 1 ] Razavi B. RF micro electronics. Englewood Cliffs ,NJ : Prentice Hall 1998

- [2] Taddiken B, Ezell W, Mumper E, et al. Broadband tuner on a chip for cable modem, HDTV, and legacy analog standards. IEEE Frequency Integrated Circuit Symposium, 2000

- [3] Rogers J, Plett C. Radio frequency integrated circuit design. Norwood, MA: Artch House, Inc., 2003

- [4] Shana 'a O ,Linscott I ,Tyler L . Frequency scalable Si Ge bipolar RF front-end design. IEEE J Solid-State Circuits ,2001 ,36

(6):888

- [5] He Q, Feng M. Low-power, high-gain, and high-linearity Si Ge BiCMOS wide-band low-noise amplifier. IEEE J Solid-State Circuits, 2004, 39(6):956

- [6] Weiner J S, Leven A, Houtsma V, et al. SiGe differential transimpedance amplifier with 50-GHz bandwidth. IEEE J Solid-State Circuits, 2003, 38(9):1512

- [7] Fong K L, Meyer R G. High-frequency nonlinearity analysis of common-emitter and differential-pair transconductance stages. IEEE J Solid-State Circuits, 1998, 33:548

- [8] Gonzalez G. Microwave transistor amplifiers. Englewood Cliffs, NJ: Prentice Hall, 1984

- [9] Mehr I, Rose S, Nesterenko S, et al. A dual-conversion tuner for multi-standard terrestrial and cable reception. Sysmposium on VLSI Circuit, Kyoto Japan, 2005:340

- [10] Bruccoleri F, Klumperink E A M, Nauta B. Wide-band CMOS low-noise amplifier exploiting thermal noise canceling. IEEE J Solid-State Circuits, 2004, 39 (2):275

- [11] MAX 2 6 3 3 V HF-to-microwave, 3v, general-purpose amplifier. Maxim Intergrated. Products, Sunnyvale, CA. [Online].

Available: http://www.maximic.com

# 一种用于地面和有线接收机的宽带低噪声放大器 \*

#

(1 中国科学院半导体研究所 人工神经网络与高速电路实验室,北京 100083) (2 奥本大学电子工程与计算机科学系,奥本 36849-5201,美国)

摘要:提出并设计了一种用于数字电视接收调谐芯片的宽带低噪声放大器。该设计采用 0. 35μm SiGe BiCMOS 工艺,器件的主要性能为:增益等于 18. 8dB,增益平坦度小于 1. 4dB,噪声系数小于 5dB,1dB 压缩点为 - 2dBm,输入三阶交调为 8dBm.在 5V 供电的情况下,直流功耗为 120mW.

关键词: BiCMOS; 宽带; 噪声系数; 线性度; 低噪声放大器; SiGe

**EEACC:** 1205; 1220; 2570 K

中图分类号: TN722 文献标识码: A 文章编号: 0253-4177(2006)06-0970-06

<sup>†</sup>通信作者. Email:dsma @mail.semi.ac.cn 2006-01-17 收到,2006-02-16 定稿