# Analytical Model for the Piecewise Linearly Graded Doping Drift Region in LDMOS \*

Sun Weifeng<sup>†</sup>, Yi Yangbo, Lu Shengli, and Shi Longxing

(National ASIC System Engineering Research Center, Southeast University, Nanjing 210096, China)

**Abstract:** A novel 2D analytical model for the doping profile of the bulk silicon RESURF LDMOS drift region is proposed. According to the proposed model, to obtain good performance, the doping profile in the total drift region of a RESURF LDMOS with a field plate should be piecewise linearly graded. The breakdown voltage of the proposed RESURF LDMOS with a piecewise linearly graded doping drift region is improved by 58.8%, and the specific on-resistance is reduced by 87.4% compared with conventional LDMOS. These results are verified by the two-dimensional process simulator Tsuprem-4 and the device simulator Medici.

Key words: breakdown voltage; specific on-resistance; piecewise linearly graded doping drift region

**EEACC: 2560**

**CLC number:** TN710 **Document code:** A **Article ID:** 0253-4177 (2006) 06-0976-06

#### 1 Introduction

Reduced surface field (RESURF) technology<sup>[1]</sup> has been widely applied in high-voltage integrated circuit (HVIC) devices and smart power integrated circuits (SPICs) devices [2~4]. The main advantages of high-voltage devices with RESURF technology are the lowering of on-resistance and the reduction of chip size under high drain voltages. Lateral double-diffused MOS (LDMOS) is one of the most popular high voltage devices due to its easy integration with standard low-voltage CMOS. The breakdown voltage and the on-resis-tance are the two most important performance factors for LDMOS, but these two electrical parameters often conflict with each other in processing technology. In recent years, much research on how to improve the breakdown voltage and reduce the specific onresistance has been reported<sup>[5~12]</sup>. Linearly graded doping in the drift region of LDMOS was found to be one effective way to improve LDMOS performance [8~12]. References [8,9] predicted that a linear lateral doping profile in the drift region in SOI could yield the maximum breakdown voltage and the minimum specific on-resistance for SOI RE-SURF LDMOS. A computer program was developed to help realize a linear lateral doping profile, and experimental verifications were also performed<sup>[10]</sup>. However, References [8 ~ 10] apply only to SOI RESURF LDMOS. References [11,12] show that a linear lateral doping profile in the drift region in bulk-silicon also could improve the performance, but the model and simulated results are too simple—the thickness of the oxide above the drift region was assumed to be uniform, and the influence of the field plate on the performance of the BS RESURF LDMOS was not considered.

The purpose of this work is to develop a 2D analytical model for the doping profile of the drift region in LDMOS with a field plate in terms of Poisson's solution. According to the proposed model, the doping profile in the total drift region of a RESURF LDMOS with a field plate must be piecewise linearly graded in order to obtain the best performance. A RESURF LDMOS with a piecewise linearly graded doping drift region was simulated by the 2D semiconductor device simulators Tsuprem-4 and Medici. The simulation results show that the novel LDMOS has an improved trade-off

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China(No. 2004AA1Z1060), the Foundation of Graduate Creative Program of Jiangsu(No. XM04-30), and the Foundation of Excellent Doctoral Dissertation of Southeast University(No. YBJJ0413)

<sup>†</sup> Corresponding author. Email:swffrog@seu.edu.cn

between the breakdown voltage and the specific onresistance compared to conventional LDMOS. We think the model and the method will help designers improve the performance of high-voltage BS RE-SURF devices in practical LDMOS design.

### 2 Analytical models

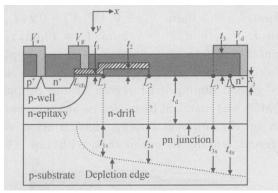

A schematic cross section of the BS RESURF LDMOS structure with a step oxide layer in the drift region is shown in Fig. 1, where x is the horizontal position relative to the left edge of the drift region and y is the vertical position relative to the surface of the drift region. The drift region is divid-

Fig. 1 Cross section of the BS RESURF LEDMOS structure

ed into four regions, the boundaries of which are denoted by  $L_1$ ,  $L_2$ ,  $L_3$ , and  $L_4$ . The p-substrate, whose doping concentration is  $N_{\text{sub}}$ , is assumed to be thick enough to deplete the substrate charge, and the width of the substrate depletion layers under  $L_i$  (i = 1, 2, 3, and 4) are  $t_{1s}$ ,  $t_{2s}$ ,  $t_{3s}$  and  $t_{4s}$ , respectively. Here  $t_1$  is the thickness of the gate oxide layer,  $t_2$  and  $t_3$  are the thicknesses of the field oxide layer under the poly gate-field-plate and the aluminum drain-field-plate, respectively. The relative dielectric constants of the oxide and the semiconductor are ox and si, respectively. The gate voltage is  $V_g$ , and the substrate and the source are grounded, while the drain is supplied with a positive voltage V<sub>d</sub>. The n-epitaxy layer thickness is  $t_d$  with a doping concentration profile of  $N_d(x)$ . The potential function (x, y) in silicon film must be satisfied by Poisson 's equation, yielding

$$\frac{d^{2}(x,y)}{dx^{2}} + \frac{d^{2}(x,y)}{dy^{2}} = -\frac{qN_{d}(x)}{0 \text{ si}}$$

(1)

Based on the theory in Ref. [13] we integrate Poisson's equation over the y-direction in the n-drift region, and obtain the following equation for 0

$$E_{1y}(x,t_d) = -\frac{qN_d(x)}{0 \text{ si}} t_d, \quad 0 \quad x \quad L_1$$

(2)

Assuming that the electrical flux along the  $SiO_2$  interface is continuous ,the following equation can be obtained by neglecting the influence of the fixed charge in the  $SiO_2$  material.

$$E_{1y}(x,0) = -\frac{ox[-1(x,0) - V_g]}{s_i t_1}$$

(3)

Here  $V_{\rm g} = V_{\rm g} - V_{\rm FB}$  is the applied voltage and  $V_{\rm FB}$  is the flat-band voltage. Assuming that the n-drift region is fully depleted we get

$$E_{1y}(x, t_{d}) = \frac{2[-1(x, 0) - -1(x, t_{d})]}{t_{d}}$$

$$= \frac{2[-1(x, t_{d}) - 0]}{t_{s1}}$$

$$= \frac{2[-1(x, 0)]}{t_{d} + t_{s1}}$$

(4)

Here  $t_{s1}$  can be defined as  $\frac{t_{1s}}{2}$  according to the assumption in Ref. [14]. According to the RESURF principle, the depletion approximation is suitable for the n-drift region. We can assume  $\frac{d^2 + (x, y)}{dx^2}$

$\frac{d^2_{-1}(x,0)}{dx^2}$  in the first-order approximation<sup>[15]</sup>.

From Eqs.  $(2 \sim 4)$ , we obtain

$$\frac{d^{2}_{1}(x,0)}{dx^{2}} - _{f1}(x,0) = _{f1}$$

(5)

where

$$_{f1} = \frac{_{ox}}{_{si} t_1 t_d} + \frac{2}{t_d (t_d + t_{s1})}$$

, and  $_{f1} = -[\frac{qN_d(x)}{_{0 \ si}} + \frac{_{ox}}{_{si} t_1 t_d} V_g]$ .

In the same way, we can obtain three similar equations under the conditions of  $L_1$  x  $L_2$ ,  $L_2$  x  $L_3$ , and  $L_3$  x  $L_4$ . The only difference is that  $E_{3y}(x,0)=0$  for  $L_2$  x  $L_3$  according to Ref. [16]. Then, we obtain the general expression

$$\frac{d^{2}_{i}(x,0)}{dx^{2}} - f_{i}(x,0) = f_{i}$$

(6)

where

$$_{f2} \; = \; \frac{_{ox}}{_{si}\;t_{2}\;t_{d}} \; + \; \frac{2}{t_{d}\left(\;t_{d}\;+\;t_{s2}\right)}$$

$$_{f2} \; = \; - \; \left[\; \frac{qN_{d}\left(\;x\right)}{_{0\;\;si}} \; + \; \frac{_{ox}}{_{si}\;t_{2}\;t_{d}}\;V_{g}\;\right]$$

$$f_{3} = \frac{2}{t_{d}(t_{d} + t_{s3})}, \quad f_{3} = -\frac{qN_{d}(x)}{0 \text{ si}}$$

$$f_{4} = \frac{0x}{s_{i}t_{3}t_{d}} + \frac{2}{t_{d}(t_{d} + t_{s4})}$$

$$f_{4} = -\left[\frac{qN_{d}(x)}{0 \text{ si}} + \frac{0x}{s_{i}t_{3}t_{d}}V_{d}\right]$$

$$V_{d} = V_{d} - V_{FB}$$

Neglecting the influence of the junction depth of the drain region, according to Ref. [15],  $t_{4s}$  can be defined by the following equation, which follows from the 1D Poisson's equation.

$$t_{4s} = \frac{t_d}{2} \times \left[ \sqrt{\frac{8_{si} - 0}{qN_{sub} t_d^2}} - 1 \right]$$

(7)

According to the RESURF principle, if the n-drift region is fully depleted and the concentration of the p-substrate is uniform, then  $t_{is}$  can be approximately defined as  $t_{is} = \frac{L_{\cdot i}}{L_{\cdot 4}} \, t_{\cdot d} \, (\, i = 1 \, , 2 \, , and \, 3)$ . Based on the assumption in Ref. [14],  $t_{si}$  can be defined as  $t_{si} = \frac{t_{\cdot is} + t_{\cdot (i-1)s}}{2}$ , where  $i = 2 \, , 3 \, , and \, 4$ .

According to Ref. [12], in order to attain the maximum breakdown voltage, the surface potential distribution should follow the equation

$$(x,0) = \frac{V_d}{L_4}x$$

(8)

Substituting Eqs. (8) and (7) into Eq. (6), we obtain the following equations:

$$N_{d1} \, ( \, x ) \ = \ M_{f1} \, x \, - \, \frac{_{0 \ ox}}{q t_1 \, t_d} \, V_g \, , \quad 0 \qquad x \qquad L_1 \eqno(9)$$

$$N_{d2}(x) = M_{f2}x - \frac{0 - ox}{qt_2 t_d} V_g, L_1 x L_2$$

(10)

$$N_{d3}(x) = M_{f3} x, L_2 x L_3$$

(11)

$$N_{d4}(x) = M_{f4}x - \frac{0 \text{ ox}}{qt_3 t_d} V_d, L_3 x L_4$$

(12)

where  $M = \frac{0-si}{qL_4} V_d$ .

From Eqs. (9~12), we can draw a very useful conclusion. To obtain the maximum breakdown voltage, an improved trade-off between the breakdown and the specific on-resistance, the doping profile in the total drift region in an LDMOS with a field plate must be piecewise linearly graded. The following sections provide some results from Tsuprem-4 and Medici to show that the piecewise

linearly graded doping drift region is very effective for improving the performance of BS RESURFLDMOS.

#### 3 Simulation and discussion

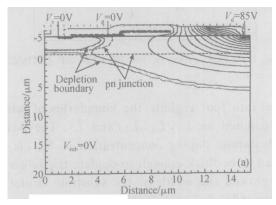

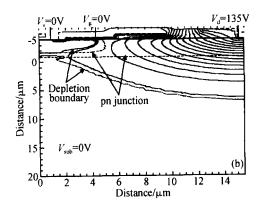

The cross sections of the proposed and the conventional BS RESURF LDMOS structures are uniform, as can be seen in Fig. 1. Figure 2 shows the equipotential contour lines of the conventional (a) and the proposed (b) BS RESURF LDMOS at their breakdown voltages. The simulation results of the conventional LDMOS are obtained with  $N_{\text{sub}} = 1 \times 10^{15} \text{ cm}^{-3}$ ,  $N_{\text{d}} = 3 \times 10^{14} \text{ cm}^{-3}$ ,  $t_{\text{d}} = 3 \cdot 1 \mu \text{m}$ ,  $t_{\text{ch}} = 3 \cdot 0 \mu \text{m}$ ,  $t_{\text{BB}} = 0.1 \text{V}$ ,  $t_{\text{g}} = 0 \text{V}$ ,  $t_{\text{l}} = 1 \mu \text{m}$ ,  $t_{\text{l}} = 4 \cdot 5 \mu \text{m}$ ,  $t_{\text{l}} = 7 \cdot 5 \mu \text{m}$ ,  $t_{\text{l}} = 10 \mu \text{m}$ ,  $t_{\text{l}} = 30 \text{nm}$ ,  $t_{\text{l}} = 630 \text{nm}$ ,  $t_{\text{l}} = 1630 \text{nm}$ , and the supplied breakdown voltage  $t_{\text{l}} = 85 \text{V}$ . The piecewise linearly graded doping drift region of the proposed LDMOS was matched by piecewise stepwise variation of the uniform doping concentration with different lengths in

Fig. 2 Equipotential contour lines of the conventional (a) and the proposed (b) BS RESURF LDMOS at their breakdown voltages

accordance with Eqs.  $(9 \sim 12)$ . In the practical process, the piecewise linearly graded drift region doping profile can be fabricated using a single phosphorus implant through a mask with a series of openings of different sizes<sup>[17]</sup>. The other parameters of the proposed LDMOS are the same as the conventional structure except for the applied breakdown voltage in the simulations. The contour lines along the drift region of the conventional LD-MOS is not symmetrical, and the contour lines crowd at the drain region, which results in an avalanche breakdown, as can been seen in Fig. 2 (a). However, from Fig. 2(b) we find that the contour lines along the drift region of the proposed RE-SURF LDMOS with a piecewise linearly graded doping drift region are very symmetrical, which improves the breakdown voltage. If the ionization integral is equal to 1, an avalanche breakdown will occur. In this way, the breakdown voltage of the conventional LDMOS is limited to 85V, but the breakdown voltage of the proposed RESURF LD-MOS with piecewise linearly graded doping drift region can reach 135V, which can be seen in Fig. 3. The breakdown voltage of the proposed RESURF LDMOS is improved by 58. 8 % compared with that of conventional LDMOS.

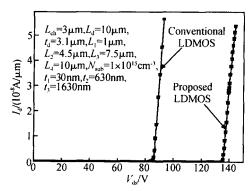

Fig. 3 Breakdown characteristic curves of the proposed and the conventional LDMOSs

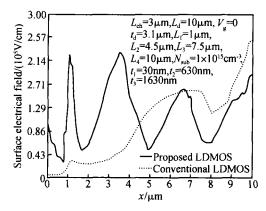

Figure 4 shows the surface electrical field distribution along the drift region of the proposed and the conventional LDMOS at their breakdown voltages. There are five electrical field peaks in the surface electrical field distribution of the proposed LDMOS with the piecewise linearly graded doping drift region, and each electrical field peak value is less than that of the critical electrical field. This kind of surface electrical field distribution can greatly reduce the maximum peak electrical field so

as to obtain the maximum breakdown voltage, which agrees with the theoretical analysis we introduced earlier in Ref. [18]. In contrast, there are only two electrical field peaks in the surface electrical field distribution of the conventional LDMOS, and the maximum electrical field peak reaches a magnitude of 2.  $5 \times 10^5 \, \text{V/cm}$  at the drain edge. The nonuniform electrical field will greatly reduce the breakdown voltage.

Fig. 4 Surface electrical field distribution along the drift region of the proposed and the conventional LD-MOSs at their breakdown voltages

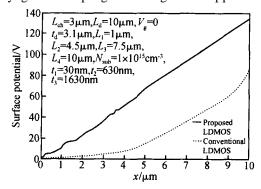

Figure 5 shows the surface potential distribution along the drift region of the proposed and the conventional LDMOS at their breakdown voltages. One can see from Fig. 5 that the potential distribution of the proposed LDMOS with the piecewise linearly graded doping drift region is approxima-

Fig. 5 Surface potential distribution along the drift region of the proposed and the conventional LDMOSs at their breakdown voltages

tively linear, which is in agreement with Eq. (8) and thus can attain the maximum breakdown voltage. The linear distribution of the surface potential also leads to the optimal electrical field distribution

in the drift region of the piecewise linearly graded doping drift region LDMOS (seen in Fig. 4). In contrast, the potential distribution of the conventional LDMOS shows a large curvature in the whole drift region, which leads to a non-uniform electrical field profile (seen in Fig. 4). Consequently, the breakdown voltage suffers a considerable degradation.

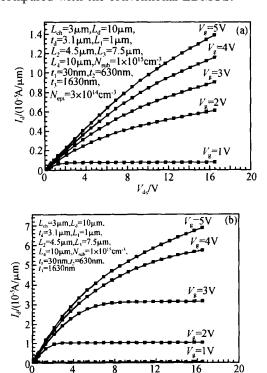

Figure 6 shows the FV curves of the conventional (a) and the proposed (b) BS RESURF LD-MOS. One can see that the saturation characteristic of the proposed LDMOS with the piecewise linearly graded doping drift region is better than that of the conventional LDMOS. The specific on resistance  $R_{\rm on}$  can be extracted from the simulated FVcurves in the linear region and the channel length of the LDMOS. The numerically calculated values of  $R_{\rm on}$ are 27. 7 and 3. 5m  $\cdot$  cm<sup>2</sup> at  $V_g = 5$ V for the conventional and the proposed RESURF LDMOS, respectively, yielding a reduction of 87. 4 %. Here, we think the concentration of the proposed LDMOS with piecewise linearly graded doping drift region is higher than that of the conventional LDMOS, so the proposed LDMOS allows a significant reduction of the specific on resistance compared with the conventional LDMOS.

Fig. 6 FV curves of the conventional (a) and the proposed (b) BS RESURF LDMOS

#### 4 Conclusion

A novel 2D analytical model for the doping profile of the bulk silicon RESURF LDMOS drift region has been proposed. The influence of the field plate and the variation of oxide layer thickness on the breakdown voltage and the specific on-resistance is taken into account in the model. According to the presented model, in order to obtain the maximum breakdown and the minimum specific on-resistance, the drift region doping profile of a RE-SURF LDMOS with a field plate must be piecewise linearly graded. In this way, a novel RESURF LD-MOS with a piecewise linearly graded doping drift region is proposed, for which the breakdown voltage is improved by 58.8 %, and the specific on-resistance is reduced by 87. 4 % compared to those of conventional LDMOS.

#### References

- [1] Appels J A, Vaes H M L. High voltage thin layer devices (RESURF devices). IEEE IEDM Tech Digest ,1979:238

- [2] Ludikhuize A W. A review of RESURF technology. ISPSD, 2000:11

- [3] Chang M F, Pifer G, Yilmaz H, et al. Lateral HVIC with 1200V bipolar and field-effect devices. IEEE Trans Electron Devices, 1986, 33:1992

- [4] Baliaga B J. An overview of smart power technology. IEEE Trans Electron Devices, 1991, 38:1568

- [5] Charitat G,Bouanane M A,Rossel P. A new junction termination technique for power devices: RESURF LDMOS with SI-POS layers. ISPSD, 1992:213

- [6] Zhu Y Z, Liang Y C, Xu S M, et al. Folded gate LDMOS transistor with low on-resistance and high transconductance. IEEE Trans Electron Devices, 2001, 48(12):2917

- [7] Kim S L, Yang H Y, Choi Y I. A low on-resistance SOI LD-MOS using a recessed source and a trench drain. 22nd International Conference on Microelectronics, 2000, 2:641

- [8] Paul K,Leung Y K,Plummer J D, et al. High voltage LDMOS transistors in sub-micron SOI films. ISPSD, 1996:89

- [9] Kim H W, Choi Y I, Chung S K. Linearly graded surfacedoped SOILDMOSFET with recessed source. Microelectronics Engineering, 2000, 51/52:547

- [10] Zhang S D, Sin J K O, Lai T M L, et al. Numerical modeling of linear doping profiles for high-voltage thin-film SOI devices. IEEE Trans Electron Devices, 1999, 46(5):1036

- [11] He Jin, Zhang Xing, Wang Yangyuan. Linearly varying surface implanted in layer used for improving trade-off between breakdown voltage and or resistance of RESURF LDMOS transistor. Microelectronics Journal, 2001, 32:969

- [12] He Jin, Xi Xuemei, Chan Mansun, et al. Linearly graded doping drift region: a novel lateral voltage-sustaining layer used for improvement of RESURF LDMOS transistor performances. Semicond Sci Technol, 2002, 17:721

- 第6期

- [13] Porter D , Stirling D S G. Integration equations. Cambridge University Press ,1990

- [14] Han S Y, Kim H W, Chung S K. Surface field distribution and breakdown voltage of RESURF LDMOSFETs. Microelectronics Journal, 2000, 31:685

- [15] He Jin ,Zhang Xing. Quasi-2-D analytical model for the surface field distribution and optimization of RESURF LDMOS transistor. Microelectronics Journal ,2001 ,32:655

- [16] Chung S K, Han S Y. Analytical model for the surface field

- distribution of SOI RESURF devices. IEEE Trans Electron Devices ,1998 ,45:1374

- [17] Schulze H J, Kunhnert R. Realization of a high-voltage planar junction terminations for power devices. Solid-State Electron, 1989, 32:175

- [18] Sun W F, Shi L X. Analytical models for the surface potential and electrical field distribution of bulk-silicon RESURF devices. Solid-State Electron .2004 .48:799

## 体硅 LDMOS 漂移区杂质分段线性注入模型研究\*

孙伟锋 易扬波 陆生礼 时龙兴

(东南大学国家 ASIC 系统工程技术研究中心,南京 210096)

摘要:提出了体硅 LDMOS 漂移区杂质浓度分布的一种二维理论模型,根据该模型,如果要使带有场极板的 LDMOS 得到最佳的性能,那么 LDMOS 漂移区的杂质浓度必须呈分段线性分布. 用半导体专业软件 Tsuprem-4 和 Medici 模拟证明了该模型十分有效,根据该模型优化得到的新型 LDMOS 的击穿电压和导通电阻分别比常规 LDMOS 增加 58.8%和降低 87.4%.

关键词: 击穿电压; 导通电阻; 分段线性

**EEACC: 2560**

中图分类号: TN710 文献标识码: A 文章编号: 0253-4177(2006)06-0976-06

<sup>\*</sup>国家高技术研究发展计划(批准号:2004AA1Z1060),江苏省高等学校研究生创新计划(批准号:XM04-30)及东南大学优秀博士学位论文基金(批准号:YBJJ0413)资助项目

<sup>†</sup>通信作者. Email:swffrog @seu.edu.cn 2006-01-18 收到,2006-03-02 定稿