# 多电流路径抑制片上电感电流拥挤效应

# 刘 珂 黄洪彦 黄晨灵 唐长文 闵 昊

(复旦大学专用集成电路与系统国家重点实验室,上海 201203)

摘要:从电磁理论出发解释了片上电感电流分配的原因,得出小横界面积金属的趋肤效应弱,大的金属线宽和相邻金属间距比的偶耦合临近效应小的结论.采用 4 层金属的 0. 35µm 标准 CMOS 工艺制造片上电感,将差分电感的单电流路径,分成多电流路径并联,在保持了电感的电学对称性的前提下,抑制了电感的电流拥挤效应,电感的最大品质因数提高了 40 %,同时降低了其自谐振频率.

关键词:片上电感;品质因数;趋肤效应;临近效应;多电流路径;自谐振频率;串联电阻;寄生电容

**EEACC:** 2140; 1205; 1350

中图分类号: TN3 文献标识码: A 文章编号: 0253-4177(2006)09-1690-05

# 1 引言

在过去十几年里,寻呼机、无绳电话、模拟及数字蜂窝电话等个人通信系统以及数字电视、广播及全球定位导航系统得到了迅猛发展,这些消费类电子产品的成功主要依赖于它们的成本控制、电池的使用寿命、功能和重量.集成射频模块和基带数字信号处理单元在一个单硅片上可以满足上述要求.传统的射频、微波电路往往采用 GaAs 等工艺,随着CMOS 的迅猛发展,使用标准的 CMOS 工艺设计高性能的射频、微波电路成为可能.比如最近兴起的CMOS 工艺设计数字电视调谐器[1]、蓝牙[2]等,射频 CMOS 工艺的使用会大大降低芯片的成本.标准CMOS 工艺片上电感的研究成为了热点问题.

早在 1960 年就有人研究过在硅片上做平面电感,当时得出的结论是:在硅集成电路中集成电感是不实际的. 直到 1990 年,Nguyen 和 Meyer 首次发现能够利用硅工艺制作集成电路电感. 与 GaAs 半绝缘衬底不同,硅衬底是半导体,衬底的损耗比较大,很难获得高的品质因数[3.4].最近,很多研究人员对依靠非标准工艺的方法提高电感的性能比较感兴趣,比如使用高电阻率(150~200 ·cm)的硅衬底、将线圈下面的硅腐蚀掉等方法[5.6].

还有一个限制标准 CMOS 工艺片上电感品质 因数的重要原因是由电流拥挤效应引起的片上电感 高频电阻<sup>[7,8]</sup>. 在几个 GHz 范围以内,高频金属的高 频电阻是片上电感品质因数低的主要原因. 因此提高射频频率的标准 CMOS 工艺片上电感的主要任务是降低金属互连线的电流拥挤效应(包括趋肤效

应和临近效应)<sup>[9,10]</sup>.由于电路和元件设计人员不能改变标准工艺,本文的重点就是在详细分析电流拥挤效应的物理机制下,在标准工艺下通过多电流路径结构的优化设计降低电感的电流拥挤效应,从而提高电感的品质因数.多电流路径的方法已经有文献提及<sup>[11]</sup>.但是该文采用的是多电流路径内外缠绕的方法,需要较多的金属层次,采用了更多的通孔,使得该方法在通孔和互连线的电阻率不一致的工艺下增大了电感的电阻,同时使电感失去了对称性.而保证电学对称的差分电感是保证差分电路高性能的前提条件<sup>[12]</sup>.本文将差分电感的单一电流路径分成多路径,在降低电流拥挤效应的同时,保证了电感的对称性.在电流流入流出电感的位置简单地将多路径并联,所以该方法结构简单,通孔电阻低,可以适用于较少金属层次的工艺.

# 2 电流拥挤效应

电感是由金属互连线缠绕而成. 随着频率的增加,金属中的电流不再是均匀地流动,而是随着工作频率以及电感的形状、结构等不同在金属的某些部位集中,进而增大电感的电阻. 这个效应称为电流拥挤效应,它又可细分为趋肤效应和临近效应.

#### 2.1 趋肤效应

在直流电路中,均匀导线横截面上的电流是均匀的.当交变电流通过导体时,由于导线周围存在电磁场,导线本身就会产生涡流,涡流的磁场会引起高频交变电流趋向导线表面,使导线横截面上电流的分布不均匀,即表面层上的电流密度最大,随着进入

导体深度的增大而减小. 这种现象称为趋肤效应. 趋肤效应使有效的横截面积减小了,从而使它的等效电阻增加了.

对长方形导体的趋肤效应问题的研究可以追溯到 1916 年<sup>[13]</sup>,直到今天仍旧是集成电路研究人员的热门话题. Faraji-Dana 和 Chow 在解析基础上拟合得到了可缩放的趋肤效应公式<sup>[14]</sup>,被证明具有可靠的精度<sup>[15,16]</sup>. 该公式中的导线宽度和厚度是可缩放的,比较适合片上电感的趋肤电阻分析,本文采用该模型进行片上电感的趋肤电阻计算. 金属导体的趋肤阻抗表示为<sup>[16]</sup>:

$$Z_{skin}() = \sqrt{(1/wt)^2 + (kZ_{hf}()/(w+t))^2}$$

(1)

其中 ,w,t分别为金属的电导率,宽度和厚度;k是拟合系数,其值为 1.2; Zhf是在频率高到一定程度,趋肤深度远小于金属厚度,金属内部没有载流子时的阻抗.此时的电阻与厚度无关,只与频率和电导率有关,这时的阻抗表示为:

$$Z_{\rm hf}() = \sqrt{j \mu/4} \tag{2}$$

长方形导体的电阻就是公式(1)的实部. 该方程的虚部可以用来分析线圈高频时电感值的变化. 趋肤电阻系数等于趋肤电阻与直流电阻之比:

$$k_{skin} = \frac{\text{real}(Z_{skin}(\cdot))}{R_{dc}}$$

$$= (1 + ((kwt/(2(w+t)))^2 | \mu |)^2)^{0.25} \times \cos\left[\frac{1}{2}\arctan((kwt/(2(w+t)))^2 | \mu |)\right]$$

(3)

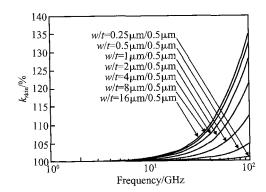

式中的 w 和 t 可以互换. 图 1 是通过(3)式计算得到的不同横截面积导体的趋肤电阻系数. 由(3)式和图 1 可以得出: k<sub>skin</sub>随着金属横截面积(w x t)的增大以及频率的提高而增大.

图 1 不同的横截面积导体趋肤电阻系数

Fig. 1 Skin resistance coefficients of the different crossing area of the conductor

#### 2.2 临近效应

由于临近金属的电流流动,产生的交变磁场通

过该金属,根据楞次定律该金属会产生涡电流来抑制磁场的变化,该现象称为临近效应.临近效应在本质上也是由于涡流引起的,与趋肤效应不同的是,趋肤效应是流过电流的金属自身的电磁场引起的,而临近效应是由于临近的金属流过电流,在无论有无电流流过的临近金属产生的电磁场引起的涡流.涡流的产生改变了电感临近线圈的电流分布和电流密度,增大了电感的等效串联电阻,该部分电阻称为临近效应电阻.

下面的分析集中在一次涡流,就是原线圈电流产生的交变磁场激励的涡流,由于涡流相对于原线圈的电流较弱,不再考虑涡流再次激励的涡流,尽管该涡流与电感的原电流方向一致.

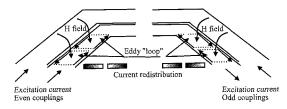

从图 2 可见,当两个导体靠近的时候,一个有电流流动的导体产生的磁场通过临近的导体,在该导体上产生涡流.如果两个导体都有电流,电流方向相同称为偶耦合,电流方向相反称为奇耦合.在奇耦合的时候,在两个导体相邻边缘的涡流方向是和导体原电流方向相反,在非相邻导体边缘的涡流方向和导体原来的电流方向相同;而偶耦合的电流分布恰好与奇耦合相反.这样在涡流与原导体电流同向的地方,时间平均来看,导体的电流增大;在涡流与原导体电流反向的地方,时间平均来看,导体的电流降低.表现为整体电感的有效截面积降低,电感的电阻增大,即临近效应.

图 2 两个相邻导体的临近效应示意图

Fig. 2 Illustration of the proximity effect of two conductors

衬底涡流的电流方向与电感线圈的电流方向相反,电感和衬底的涡流之间的耦合是奇耦合方式。电感和衬底之间的奇耦合临近效应使得电感和衬底的电流分别向下和顶层聚集;为了增大互感,在片上电感中相邻的两个线圈的电流是同向的,就是偶耦合方式,使得电流向相邻金属的外边缘聚集;线圈是环路,对面的线圈电流方向相反,使得以电感中心对称的线圈之间是奇耦合,促使电流向线圈的内半径方向聚集,尤其是在奇耦合渐强的内圈。叠层电感线圈之间是偶耦合,电流会向上下分散。这就是电感线圈电流分布的趋势和原因。

Faraji-Dana 等人[17]的文章给出这样的结论:

(1) 临近效应会随电感工作频率的增大而加强;

(2)临近效应随着相邻金属的宽度和间距之比(w/s)的增大而加强;(3)相同的条件下,奇耦合的临近效应效果强于偶耦合的临近效应效果.

#### 2.3 多电流路径抑制电流拥挤效应

金属之间的最大距离是受工艺的设计规则限制的,采用最近的间距后,为了降低临近效应而降低金属宽度和间距比值,就要降低金属宽度。这样同时就会降低金属的趋肤效应,但是会增大金属的直流电阻,为此可以将多根金属并联来降低金属的直流电阻,同时能够抑制电流拥挤效应.

# 3 实验与讨论

为了验证多电流路径是否能够降低片上电感的电流拥挤效应,采用新加坡特许(Charted)半导体的4层金属的射频和模拟工艺分别设计了中空的以及非中空的多电流路径电感.使用 GSG探针台以及网络分析仪进行了在片测试.

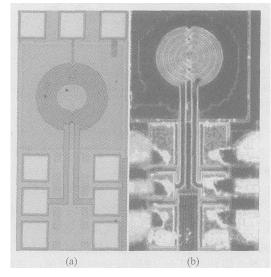

### 3.1 中空的多电流路径电感

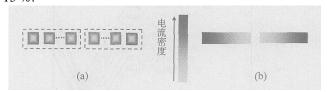

图 3(b)是 4 电流路径 3 圈差分电感的版图照片.将一个电感线圈分成 4 股,在电流流入和流出电感的位置并联.电感保持了对称结构.结构的对称意味着电学的对称,这样的电感用在差分电路中,可以提高自身以及电路的性能,同时能够降低芯片的面积[12,18].由于距电感中心的距离越近,临近效应越明显,为此电感设计为中空结构.

图 3 0.35µm 两多晶硅四铝工艺的射频(a)和模拟(b)工艺设计的电流多路径片上电感芯片版图照片

Fig. 3 Die photos of the inductor with multi-current-path in 0.  $35\mu m$  2p4m RF (a) and analog (b) technology

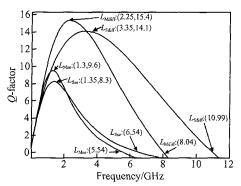

图 4 是单圈金属线宽相同的多电流路径电感和单电流路径电感品质因数的比较. 图中下标 M 和 S 分别代表多电流路径和单电流路径; diff 和 se 分别表示差分和单端.

图 4 多电流路径和单电流路径电感的品质因数

Fig. 4 Q-factor of the inductors with multi-current-path and single-current-path

由于电流拥挤效应使得线圈内的电流更加集 中,而加大线圈的自感;但是由于临近效应使得电流 的再分布,在外圈电流趋向该圈的外边缘,内圈电流 趋向内边缘,如图 5 所示,使得不同线圈之间的线圈 耦合系数降低,互感减小,对于互感大于自感的线圈 而言,临近效应会降低线圈的电感值,临近效应使得 线圈的有效电流面积减小,同时增大了相邻线圈电 流的有效距离. 电感线圈与衬底之间的耦合电容与 电感的有效电流面积成正比. 而相邻线圈之间的寄 生电容与两者的有效电流的间距成反比. 因此临近 效应降低了电感的寄生电容. 所以多电流路径电感 的自谐振频率和最大品质因数所在的频率都比单电 流路径的电感低,如图 4 所示. 多电流路径抑制电流 拥挤效应的作用是明显的,对于中空的电感而言,多 电流路径的最大品质因数比单电流路径电感高 15 %.

图 5 多电流路径(a) 和单电流路径(b) 的偶耦合导体的电流分布示意图

Fig. 5 Current distribution of the even coupling conductors with multi-current-path (a) and single current path (b)

#### 3.2 不同电流路径的电感

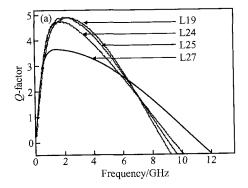

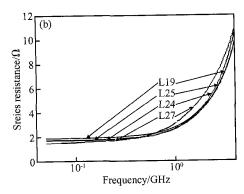

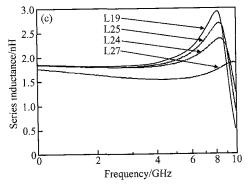

图 6 为非中空的不同电流路径的电感性能对比. 其中L19,L25,L24和L27分别为 5,4,3,1 电流路径,电感的单电流路径金属线宽等于多电流路径

金属线宽之和. 这样电流路径越多,电感的直流电阻越大.

图 6 不同路径电感的品质因数(a) ,串联电阻(b)和串联电感

Fig. 6 Q,  $R_s$  and  $L_s$  of the inductors with different current paths

显然,尽管多电流路径电感的直流电阻大,其最大品质因数仍明显高于单电流路径电感,其最大品质因数高出该频率处的单电流路径电感的品质因数近40%,如图6(a)所示.这说明多电流路径对高频电阻的抑制作用是明显的.越是内圈电感的电流拥挤效应越强,所以本次实验中多电流路径抑制电流拥挤的效果比图4的中空电感结构明显.在单圈金属线宽相同时,电流路径越多,电感的直流电阻越大.所以低频时少电流路径的电感的串联电阻小;随着频率的增大,电流拥挤效应使得电流路径少的电

感串联电阻增大的速率大于电流路径多的电感,使得多电流路径电感的电阻相对较小,如图 6(b)所示.电流拥挤效应加大了有效的电感线圈电流的间距,因此电流的路径越少,相邻电感线圈之间有效电流的间距就越大,使得相邻线圈之间的耦合系数降低,电感值下降,寄生电容减小.这种效应随着频率的增大而加强,如图 6(c)所示.所以在到达自谐振频率之前,水平电流路径越多电感值越大,还有其寄生电容大,使其自谐振频率低,如图 6(a)所示.

# 4 结论

本文详细分析了电流拥挤效应的物理原因,给 出了电感的电流分布趋势. 推导了趋肤电阻系数公 式,进而分析得出小横截面积金属的趋肤效应低,通 过分析临近效应得出:偶耦合情况下临近效应随着 相邻金属的宽度和间距之比的降低而减小. 但是宽 度小的金属直流电阻大,为此采用在电流流入流出 电感的时候单圈电感并联相对窄的多电流线圈,来 降低金属的直流电阻的同时降低电感的高频电阻. 采用 4 层金属的标准 CMOS 工艺进行了不同电流 路径电感流片测试. 射频工艺的中空电感的 4 电流 路径电感的品质因数高于单电流路径的中空电感 15 %. 模拟工艺的非中空电感的多电流路径电感的 最大品质因数高于单电流路径电感 40 %. 将差分电 感的单电流路径,分成多电流路径并联,在保持了电 感的电学对称性的前提下,抑制了电感的电流拥挤 效应,提高了电感的最大品质因数,多电流路径电感 线圈之间的耦合系数大,进而相对的电感值比少电 流路径的电感值大,同时由于临近效应少电流路径 的寄生电容小于多电流路径,因此多电流路径的自 谐振频率低,多电流路径的方法是用来抑制高频电 流拥挤的,但是在高频的时候,这种结构的品质因数 却低于单电流路径. 还有由于不同路径线圈之间的 最小距离要满足工艺要求,使得相同总体宽度的单 圈电感而言,其直流电阻增大,因此,多电流路径电 感要仔细设计,使得电感的最大品质因数的频率出 现在电路的工作频率,其电感数值满足电路的要求. 这样就能确保多电流路径电感对单电流路径电感的 优势.

致谢 作者非常感谢杭州电子科技大学的孙玲玲教授、胡江博士,南京五十五所的李拂晓研究员在电感测试方面给予的无私帮助.

#### 参考文献

[1] Tang Zhangwen, He Jie Jian Hongyan, et al. Accurate 1. 08-

- GHz CMOS LC VCO. Chinese Journal of Semiconductors, 2005.26(5):867

- [2] Hussein A I. A 2. 4-GHz bluetooth CMOS transceiver for wireless LANs. IEEE International Midwest Symposium on Circuits and Systems, 2003, 3:1251

- [3] Niknejad A M, Meyer R G. Analysis, design, and optimization of spiral inductors and transformers for Si RF ICs. IEEE J Solid-State Circuits, 1998, 33:1470

- [4] Burghartz J N. Progress in RF inductors on silicon-understanding substrate losses. International Electron Devices Meeting, 1998, 6~9:523

- [5] Chen K J, Hon W C, Zhang Jinwen, et al. CMOS-compatible micromachined edge-suspended spiral inductors with high Qfactors and self-resonance frequencies. IEEE Electron Device Lett, 2004, 25:363

- [6] Chen P Q, Chan Y J. Improved microwave performance on low-resistivity Si substrates by Si<sup>+</sup> ion implantation. IEEE Trans Microw Theory Tech, 2000, 48 (9):1582

- [7] Kuhn W B, Ibrahim N M. Analysis of current crowding effects in multiturn spiral inductors. IEEE Microw Theory Tech, 2001, 49:31

- [8] Ooi B L, Xu D X, Kooi P S, et al. An improved prediction of series resistance in spiral inductor modeling with eddy-current effect. IEEE Trans Microw Theory Tech, 2002, 50:2202

- [ 9 ] Sia C B ,Ong B H ,Chan K W ,et al. Physical layout design optimization of integrated spiral inductors for silicon-based RFIC applications. IEEE Trans Electron Devices ,2005 ,52:2559

- [10] Lopez-Villegas J M, Samitier J, Cane C, et al. Improvement of the quality factor of RF integrated inductors by layout optimization. IEEE Trans Microw Theory Tech, 2000, 48:76

- [11] Tiemeijer L F, Leenaerts D. Record Q spiral inductors in standard CMOS. IEDM Technical Digest of International Electron Devices Meeting, 2001, 2 ~ 5:40.7.1

- [12] Jian Hongyan, Tang Zhangwen, He Jie, et al. Analysis and optimum design of differential inductors using the distributed capacitance model. Chinese Journal of Semiconductors, 2005, 26(6):1077

- [13] Cockcroft J D. Skin effect in rectangular conductor at high frequency. Proc Royal Soc ,1929 ,122:533

- [14] Faraji-Dana R, Chow Y. Edge condition of the field and ac resistance of a rectangular strip conductor. Proc Inst Elect Eng, 1990, 137 (2):133

- [15] Stracca GB. A simple evaluation of losses in thin microstrips. IEEE Trans Microw Theory Tech, 1997, 45 (2):281

- [16] Tiemeijer L F, Havens R J, Bouttement Y, et al. The impact of an aluminum top layer on inductors integrated in an advanced CMOS copper backend. IEEE Electron Device Lett, 2004,25(11):722

- [17] Faraji-Dana R, Chow Y L. AC resistance of two coupled strip conductors. IEE Proceedings-H Microwaves, Antennas and Propagation, 1991, 138(1):37

- [18] Danesh M, Long J R. Differentially driven symmetric microstrip inductors. IEEE Trans Microw Theory Tech, 2002, 50(1):332

# Suppressing of On-Chip Inductor Current Crowding by a Multi-Current-Path Method

Liu  $\mathrm{Ke}^{\dagger}$ , Jian Hongyan, Huang Chenling, Tang Zhangwen, and Min Hao

(State Key Laboratory of ASIC & System, Fudan University, Shanghai 201203, China)

Abstract: From the view of the electromagnetic theory, we examine the current redistributions of an inductor. We conclude that metal with a small cross-section has a weak skin effect and that inductors with a smaller ratio of the turn width to the space between turns have a weak proximity effect. The inductors are fabricated in 0. 35µm four-metal CMOS technology. A turn of the differential inductor is divided into multi-shunt tracks, which keep the symmetry of the two ports of the inductor. Compared with a single-current-path configuration, the multi-current-path inductor offers a 40 % greater maximum quality factor and a narrower range of operating frequencies, which we interpret here in detail.

Key words: on-chip inductor; quality factor; skin effect; proximity effect; multi-current-path; self-resonant frequency

**EEACC:** 2140; 1205; 1350

**Article ID**: 0253-4177 (2006) 09-1690-05

<sup>†</sup>Corresponding author. Email:keliu @fudan.edu.cn