# 高增益调节系数硅单电子晶体管的输运特性\*

陈杰智1, 前 毅1 濮 林1 龙世兵2 刘 明2 郑有料1

(1 南京大学物理系 江苏省光电信息功能材料重点实验室,南京 210093) (2 中国科学院徽电子研究所 纳米技术与新器件集成技术实验室,北京 100029)

摘要:为了增强单电子晶体管中栅极和沟道量子点之间的耦合度,提高增益调节系数,发展了结合预制控制栅、电子束直写、各向异性腐蚀和热氧化的制备工艺.在室温下对器件的电学特性进行测量,观察到了典型的库仑振荡效应和负微分电导效应.基于量子点能级分立模型,分析了器件的输运原理,重点研究了强耦合作用对器件输运性质的影响.研究表明,通过控制量子点的热氧化时间,将器件量子点尺寸减小到7.6nm,增益调节系数提高到0.84.

关键词:单电子晶体管;库仑阻塞;库仑振荡;负微分电导

**PACC**: 7335C; 7340G

中图分类号: TN321 文献标识码: A 文章编号: 0253-4177(2007)01-0069-04

#### 1 引言

随着纳电子学研究的不断深入和量子信息领域 的兴起,单电子晶体管(SETs)作为一种基于量子隧 穿和库仑阻塞效应的纳米器件,逐渐得到广泛的关 注[1~7]. 为了将 SETs 应用于逻辑电路,一方面要提 高器件的工作温度和热稳定性,而实现这一点的关 键在于量子点尺寸的减小和可控,例如结合电子束 直写工艺和各向异性湿法腐蚀工艺方法制备的在室 温下工作的硅单电子晶体管[4];另一方面,要改进器 件性能提高电压增益以期将其应用于逻辑电路,也 即增强栅极和沟道量子点耦合度,提高增益调节系 数  $\alpha(\alpha = C_g/C_{dot})$ , 栅极电容  $C_g$  与量子点总电容  $C_{dot}$ 的比值). 据最新研究进展表明,在硅衬底上采用 6nm 薄层栅氧层可以将  $\alpha$  值提高到  $0.6^{[5]}$ ; 而基于 SOI 衬底制备的硅基单电子晶体管则将 α 值提高到 了 0.82<sup>[6]</sup>.为了进一步提高电压增益,NTT 实验室 基于 V-PADOX 制备的硅基 SETs 对此做了深入的 研究[7].从  $\alpha$  物理定义可知,在增大栅极电容  $C_g$  的 同时需要减小量子点和电极之间的电容( $C_s$ 和  $C_d$ ) 才能提高 $\alpha$ 值,然而对于目前所制备的常规单电子 晶体管结构,在减小量子点尺寸以提高其工作温度 的同时, $C_g$  和  $C_s(C_d)$  是同步变化的.为解决这个矛 盾,原理上可以通过固定栅极绝缘介质厚度,使栅极 电容 $C_g$ 的减小程度低于量子点和电极间电容 $C_g$  $(C_d)$ ,以此来提高器件增益调节系数,但就常规器 件制备方法而言是难以实现的.

文中,我们提出了预制栅绝缘层和多晶硅栅的方法,结合电子束直写、各向异性湿法腐蚀和热氧化等工艺技术,制备了量子点结构的硅单电子晶体管,并获得了小于 10nm 的量子点,其中增益调节系数提高到 0.84.在室温下对器件进行电学特性测量,观测到了显著的库仑振荡和负微分电导效应,文中深入探讨了其输运机制.

#### 2 器件结构和工艺制备

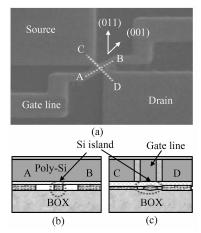

实验中器件衬底采用的是 p型(001) 晶面 SOI (silicon-on-insulator)材料,其初始表层硅厚度为 50nm. 首先,通过热氧化方法将 SOI 表层硅的厚度 减薄至 15nm,并保留 15nm 二氧化硅作为栅绝缘介 质层,然后采用 LPCVD 工艺先后沉积 200nm 的多 晶硅栅层和 50nm 的氮化硅掩膜层,其中,沉积氮化 硅前对多晶硅材料进行磷离子注入并高温热退火. 其次,用电子束直写曝光工艺将设计的器件版图图 形转移到电子束抗蚀剂上(如图 1(a)所示),并进行 ICP 干法刻蚀将图形转移到多晶硅层;同时利用图 形结构特点,通过氧化使多晶硅在点接触区域隔断, 从而使多晶硅栅仅斜跨过所设计量子点的上方;第 二次干法刻蚀去除栅绝缘层,即将图形转移到衬底 的表层硅上. 利用各向异性湿法腐蚀液 TMAH 对 硅的腐蚀特性使量子点结构自然形成,并通过轻微 热氧化进一步减小沟道中量子点的尺寸[8~11].此后 的工艺步骤与标准 MOSFET 工艺类似: 光学光刻 开源漏注入窗口;磷离子注入(注入能量为 25keV,

<sup>\*</sup>国家自然科学基金(批准号:60225014)和江苏省自然科学基金(批准号:DK2004211)资助项目

<sup>†</sup>通信作者.Email:chenjiezhi@sohu.com

剂量为 5×10<sup>15</sup> cm<sup>-2</sup>);氮气氛围中快速热退火;LPCVD 沉积二氧化硅绝缘层;光学光刻开接触窗口;用缓冲氢氟酸腐蚀去除窗口中的二氧化硅;电子束蒸铝金属;光学光刻电极图形;最后采用剥离的方法制备铝金属电极.图 1(a)是电子束直写后器件结构的 SEM 图像,源漏电极边缘沿〈011〉晶向.由于热氧化作用,〈001〉晶向多晶硅与源漏电极上多晶硅断开成为独立的斜跨多晶硅栅,同时其下方的衬底表层硅因各向异性湿法腐蚀的作用被去除,量子点与源漏电极之间则形成了点接触结构(如图 1(b),(c)).

图 1 制备的单电子晶体管示意图 (a)电子東直写后所设计器件结构的扫描电镜图像;(b) A-B 方向器件结构剖面图;(c) C-D 方向器件结构剖面图 量子点与源漏区域是点接触结构. Fig. 1 Schematic view of fabricated SETs (a) SEM image of the EBL patterned structure; (b) Side-view along A-B orientation; (c) Side-view along C-D orientation The quantum dot is formed with point-contact to the source/drain.

为了研究量子点热氧化减小过程对增益调节系数的影响,在湿法腐蚀形成量子点之后,我们改变量子点的热氧化时间制备了两类器件,Device A(1h)和 Device B(1.5h).采用 Agilent HP4156C 半导体精密参数分析仪对器件的电学特性进行了测量.

#### 3 结果与讨论

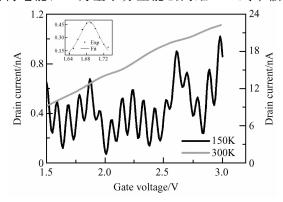

图 2 是不同温度下 Device A 中源漏电流  $I_{cs}$ 随 栅压  $V_{cs}$  变化的库仑振荡曲线,源漏偏压  $V_{cs}$  固定为  $10 \, \text{mV}$ . 量子点中由于量子尺寸限制效应而形成了分立能级,当分立能级位于源漏电极费米能级之间也即输运窗口时,该分立能级参与电子输运;当没有能级位于输运窗口时,由于库仑荷电作用电子不能 隧穿通过量子点,输运无法进行,此时在电学特性上表现为源漏电流为零,即库仑阻塞. 固定  $V_{cs}$  改变  $V_{cs}$ ,量子点分立能级便一个个顺序进入输运窗口然

后离开,当能级位于输运窗口中时参与电子输运过程,在电学特性上则表现为一个电流峰.从图 2 可以看到,由于热涨落能量的减小,在室温下观测不到的库仑振荡现象在温度降低到 150K 时变得非常明显,其峰间距为 90meV,由此计算得到的栅极电容 $C_g$  为 1.8aF. 我们在下面计算量子点尺寸的同时考虑了量子能级分立与库仑荷电能,因为当量子点尺寸较小时这两种能量是可比拟的.

$$e \Delta V_{\rm g} = \frac{e^2}{\alpha C_{\rm dot}} + \frac{\Delta E}{\alpha}$$

(1)

$$C_{\text{dot}} = 4\pi\varepsilon_{r}\varepsilon_{0} r \tag{2}$$

式中  $\alpha$  为增益调节系数,即栅极和量子点之间电容  $C_g$  相对量子点总电容  $C_{dot}$  的比值;  $e^2/C_{dot}$  为库仑荷电能;  $\Delta E$  为量子分立能级间距. (2)式中假设

图 2 室温下 Device A 的  $I_{ds}$ - $V_g$  特性曲线  $V_{ds} = 10 \text{mV}$ ;插图:库仑振荡曲线拟合

Fig. 2  $I_{ds}$ - $V_g$  characteristics of Device A  $V_{ds} = 10$  mV; Inset; fit curve of one typical CB oscillation

量子点是被氧化硅包围的球形硅量子点,r 是量子点半径大小.考虑到量子共振隧穿宽度 150K 温度下相对于热涨落能量 kT 很小,我们采用洛仑兹共振隧穿模拟公式对实验数据进行拟合,并得到了很好的拟合结果,如图 2 中插图所示[1.12].可以得到Device A 的  $\alpha$  值为 0.76,由此计算量子点尺寸为12nm,其库仑荷电能为 62meV,量子分立能级间距为11meV.由于 12nm 量子点能级分立不足以使其在室温下克服热涨落能量 kT,所以室温测量结果中库仑振荡现象基本被湮没.另外,温度升高使热涨落能量增大,相应电荷通过隧穿势垒的几率增大,当温度升高到一定程度的时候器件的输运机制还会发生转变,从单一量子隧穿转变为量子隧穿和热激发输运相结合的形式,从电学特性上看即器件源漏电流迅速提高[1.12].

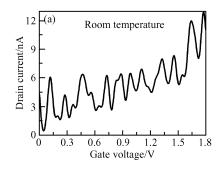

图 3 是 Device B 的电学特性曲线,其中(a)图 是在固定源漏偏压下( $V_{ds} = 100 \text{mV}$ )测量得到的  $I_{ds}$ - $V_{g}$  曲线,其峰间距平均为 150 meV,相应栅极电

容 Cg 为 1. 1aF. 对处于 0.7V 和 0.8V 之间的库仑 振荡进行模拟,可以导出器件α值为0.84,量子点 尺寸大小为 7.6nm,库仑荷电能为 98meV,量子分 立能级间距为 28meV. 值得注意的是,由于纳米结 构的氧化比较复杂,长时间氧化容易使输运沟道形 成多量子点结构,因此我们计算得到的是在输运过 程中起主要作用的量子点[13]. 相比 Device A,氧化 时间较长的 Device B 的量子点尺寸和栅极电容  $C_{\mathfrak{g}}$ 都减小了,但α值得到了提高.考虑到栅极电容的两 个关键因素是量子点尺寸大小(即接触面积)和栅绝 缘层厚度,虽然我们所设计的结构使得量子点氧化 时间的增加基本不改变栅绝缘层厚度,然而随量子 点尺寸的减小栅极电容  $C_g$  也会相应减小,但因量 子点与电极间电容的迅速减小,α值反而得到了提 高.α值的提高意味着电压增益的增大,而在逻辑器 件中大的电压增益可以有效改善逻辑器件输出端带 负载的能力[10]. 当然,如果在器件中制备更薄的栅 绝缘层,α值还可以得到进一步提高.

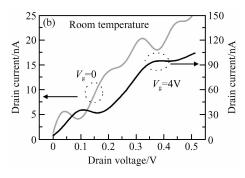

图 3 室温下 Device B 的电流-电压测量曲线 (a)  $I_{d}$ - $V_{g}$ 特性曲线,  $V_{ds}$  = 100m $V_{f}$ (b)  $I_{d}$ - $V_{g}$ 特性曲线, 不同栅压下观测到负微分电导特性

Fig. 3 I-V characteristics of Device B measured at RT (a)  $I_{\rm d}$ - $V_{\rm g}$  curve,  $V_{\rm ds} = 100\,{\rm mV}$ ; (b)  $I_{\rm d}$ - $V_{\rm g}$  curve, the NDC are obtained at different gate voltages

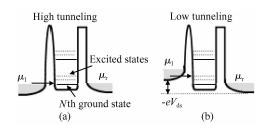

为了进一步分析栅极与量子点间强耦合作用对单电子晶体管的电学输运特性的影响,在固定栅压条件下,我们对 Device B 源漏电流随源漏偏压变化的特性进行了测量,如图 3(b)所示.曲线中具有明

显的负微分电导 NDC 效应( $V_g = 0$  时,  $V_{ds} = 0$ . 04 和 0.32V;  $V_g = 4V$  时,  $V_{ds} = 0.1V$ ). 固定外加栅极 偏压, 当源漏偏压很小时(图 4(a))输运窗口中仅出 现量子点的一个基态能级;增大源漏偏压,由于对应 隧穿能级势垒部分宽度的增加使隧穿几率下降,电 导降低,电流减小,因此出现 NDC 效应,如图 4(b) 所示[7].同时,改变栅压时也观测到了电流平台效应  $(V_g = 0, V_{ds} = 0.18 \text{ ft } 0.45 \text{V}; V_g = 4 \text{V}, V_{ds} =$ 0.35V),这是由于当源漏偏压增大,输运窗口变宽, 当激发态能级进入输运窗口而基态能级依然处于输 运窗口中的时候,输运通道的增加使电子隧穿的总 几率增大,电导增加,在基态能级和激发态能级共同 作用的时候即出现电流平台现象.对比不同栅压下 的 NDC 效应,我们发现栅压的增大使 NDC 峰的位 置正向偏移,同时峰谷比也迅速下降.这是由于在强 耦合作用下,栅压的改变不但强烈影响着量子点的 能级位置,也降低了量子点隧穿势垒的高度,这将直 接增大量子点与电极间的耦合度.此时量子点的电 子输运机制不再单纯是量子隧穿过程,而逐渐转变 为跨越隧穿势垒的热激发过程,最明显的即是源漏 电流会迅速增大,如图 3(b)所示[14].

图 4 量子点能级分立示意图 (a) 低源漏偏压,隧穿几率大,电导大;(b) 增大源漏偏压,隧穿几率减小,电导降低<sup>[12]</sup> Fig. 4 Profiles of quantized energy levels (a) Low bias;(b) High-bias Part of barrier aligned with transport channel become thinner when the bias is increased<sup>[12]</sup>.

### 4 结论

本文发展了一种单电子晶体管制备的新工艺方法和思路以提高栅极和量子点的耦合度.采用一次电子束直写曝光将源、漏、栅以及量子点结构同时光刻出来,并结合各向异性湿法腐蚀和干法热氧化两种工艺使多晶硅栅与输运沟道交叠处位于量子点的上方.实际器件中得到了7.6nm的量子点和高增益调节系数0.84,并在室温下测量观测到明显的库仑振荡效应和负微分电导效应.同时,我们就栅极和量子点间强耦合作用对单电子晶体管输运性质的影响进行了分析和讨论.

#### 参考文献

- [1] Grabert H, Devoret M H. Single charge tunneling. New York; Plenum, 1992

- [2] Shen Bo, Jiang Jianfei. Numerical analysis of amplifier based on SETT. Chinese Journal of Semiconductors, 1997, 18(8); 626 (in Chinese) [沈波,蒋建飞.单电子晶体管放大器的数值研究.半导体学报,1997,18(8);626]

- [3] Sun Jinpeng, Wang Taihong. Coulomb blockade three-valued single-electron memory. Acta Physica Sinica, 2003, 52(10): 2563 (in Chinese) [孙劲鹏,王太宏.基于库仑阻塞原理的多值存储器.物理学报,2003,52(10);2563]

- [4] Saitoh M, Harata H, Hiramoto T. Room-temperature operation of current switching circuit using integrated silicon single-hole transistors. Jpn J Appl Phys, 2005, 44(11): L338

- [5] Wan Y M. Huang K D. Hu S F, et al. Coulomb blockade oscillations in ultrathin gate oxide silicon single-electron transistors. J Appl Phys. 2005. 97:116106

- [6] Miyaji K, Saitoh M, Hiramoto T. Voltage gain dependence of the negative differential conductance width in silicon single-hole transistors. Appl Phys Lett, 2006, 88:143505

- [7] Ono Y, Yamazaki K, Takahashi Y. Si single-electron transistors with high voltage gain. IEICE Trans Electron, 2001, E84-C(8);1061

- [8] Hiramoto T, Ishikuro H, Saito K, et al. Fabrication of Si nanostructures for single electron device applications by ani-

- sotropic etching. Jpn J Appl Phys, 1996, 35 (part 1, 12B): 6664

- [ 9 ] Liu J L, Shi Y, Wang F, et al. Study of dry oxidation of triangle-shaped silicon nanostructures. Appl Phys Lett, 1996, 69 (12):1761

- [10] Ono Y, Takahashi Y, Yamazaki K, et al. Fabrication method for IC-oriented Si twin-island single-electron transistors. International Electron Devices Meeting, 1998, 98:123

- [11] Lu Gang, Chen Zhiming, Wang Jiannong, et al. Fabrication and characteristics of a Si-based single electron transistor. Chinese Journal of Semiconductors, 2002, 23(3): 246 (in Chinese)[卢刚,陈治明,王建农,等. 硅单电子晶体管的制造及特性.半导体学报,2002,23(3):246]

- [12] Foxman E B, McEuen P L, Meirav U, et al. Effects of quantum levels on transport through a Coulomb island. Phys Rev B, 1993, 47(15):10020

- [13] Saitoh M, Murakami T, Hiramoto T. Effects of oxidation process on the tunneling barrier structures in room-temperature operating silicon. IEEE Trans Nanotechnology, 2003, 2 (4):241

- [14] Morgen N Y, Abusch-Magder D, Kastner M A, et al. Evidence for activated conduction in a single electron transistor. J Appl Phys, 2001, 89(1):410

- [15] Fujiwara A, Inokawa H, Yamazaki K, et al. Single electron tunneling transistor with tunable barriers using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl Phys Lett, 2006, 88:053121

## Transport Characteristics of Si-Based Single-Electron Transistors Having a High Gate Modulation Factor\*

Chen Jiezhi<sup>1,†</sup>, Shi Yi<sup>1</sup>, Pu Lin<sup>1</sup>, Long Shibing<sup>2</sup>, Liu Ming<sup>2</sup>, and Zheng Youdou<sup>1</sup>

(1 Key Laboratory of Advanced Photonic and Electronic Materials, Department of Physics,

Nanjing University, Nanjing 210093, China)

(2 Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

Abstract: To enhance the coupling strength between the gate and the quantum dot (QD) confined in the transport channel and improve the gain modulation factor, we develop a novel type of Si single-electron transistor (SET). Clear coulomb blockade oscillations and negative differential conductance (NDC) are observed at room temperature (RT). Based on the model of quantized energy levels of QDs, we analyze the transport mechanism of the fabricated devices, especially the effect of strong gate-dot coupling on the transport characteristics. The results demonstrate that 7.6nm QDs and a large gain modulation factor of 0.84 by controlling the thermal oxidation are achieved.

**Key words:** single-electron transistor; coulomb blockade; coulomb oscillations; NDC **PACC:** 7335C; 7340G

**Article ID**: 0253-4177(2007)01-0069-04

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60225014), and the Natural Science Foundation of Jiangsu Province (No. DK2004211)

<sup>†</sup> Corresponding author. Email: chenjiezhi@sohu.com