## 2. 5Gb /s /ch 0. 18µm CMOS Data Recovery Circuit

Liu Yongwang<sup>†</sup>, Wang Zhigong, and Li Wei

(Institute of RF- and OE-ICs, Southeast University, Nanjing 210096, China)

**Abstract:** A 2.5Gb/s/ch data recovery (DR) circuit is designed for an SFI-5 interface. To make the parallel data bit-synchronization and reduce the bit error rate (BER), a delay locked loop (DLL) is used to place the center of the data eye exactly at the rising edge of the data-sampling clock. A single channel DR circuit was fabricated in TSMC's standard 0.18 $\mu$ m CMOS process. The chip area is 0.46mm<sup>2</sup>. With a  $2^{31} - 1$  pseudorandom bit sequence (PRBS) input, the RMS jitter of the recovered 2.5Gb/s data is 3.3ps. The sensitivity of the single channel DR is less than 20mV with  $10^{-12}$  BER.

Key words: data recovery; delay locked loop; bit-synchronization

**EEACC:** 1200

#### 1 Introduction

A 40Gb/s optical-link communication system requires electrical interface technology with bit rates of 2.488  $\sim$  3.125Gb/s/ch and 17 parallel channels between the SerDes device and the framer IC<sup>[1]</sup>. The manifestation of this technology is called SFI-5 (SerDes framer interface level 5)<sup>[1]</sup>. One of the technical challenges posed by SFI-5 is how to recover the 17-channel parallel data. Some approaches to developing a data recovery (DR) circuit have been proposed for such a multi-bit interface<sup>[2,3]</sup>. To reduce the bit error rate (BER), these circuits adjust the rising edge of the 2.5GHz clock to the data eye center by selecting a right clock-phase<sup>[2]</sup> or interpolating two quad-phase clocks<sup>[3]</sup>.

For multi-channel data recovery applications, a problem exists for the conventional data recovery approaches. Corrupted by low-frequency wander and high-frequency jitter, the input parallel data of the multi-channel DR circuit may not be bit-synchronous. In the conventional way, each channel adjusts a local clock to its data eye center so that the recovered data are not bit-synchronous. This means that each channel should have its individual clock output so that an alignment circuit is needed in the following digital system. The alignment circuit would transfer all 17 data lanes,

which have individual clocks to a common clock domain [2].

To synchronize the parallel recovered data so that the following alignment circuit is unnecessary, we design a 2.5Gb/s/ch DR circuit. In contrast to the conventional approaches, a voltage controlled delay line (VCDL) is used to adjust the data eye center to the rising edge of the 2.5GHz reference clock. For multi-channel data recovery application, the recovered data of each channel is synchronized with the global reference clock so that all the recovered data are bit-synchronous. Used in an SFI-5 interface, all the 17-channel recovered data share a global clock output so that the alignment circuit in the following digital system<sup>[2]</sup> can be avoided.

## 2 Circuit techniques

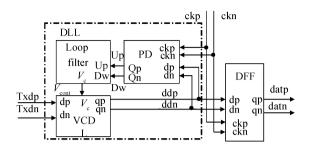

As shown in Fig. 1, the DR circuit consists of a delay-locked loop (DLL) and a D-flip-flop (DFF). To synchronize the input data with the reference clock, a VCDL is used in the DLL to adjust the data eye center to the rising edge of the reference clock. For parallel data recovery, the DR circuits of each channel share a common reference clock, so that the clock is called a global reference clock. The clock should be provided at the system level by some specific devices<sup>[2,3]</sup>. The DFF is used to regenerate the synchronized data.

<sup>†</sup> Corresponding author. Email: lywang@seu.edu.cn

Fig. 1 Block schematic of the DR circuit

#### 2.1 Delay locked loop

The DLL is used to synchronize the input data with a reference clock. As shown in Fig. 1, the DLL consists of a VCDL, a phase detector (PD), and a loop filter. The delayed data (ddp,ddn) and the reference clock (ckp, ckn) are connected to the input terminals of the phase detector (PD). When the data eye center leads the rising edge of the clock, the PD output 'Up' will be high and 'Dw' will be low, so that the capacitor in the loop filter will be charged to a higher level. For a higher loop filter output, the delay of the VCDL will be larger. On the other hand, when the data eye center lags the rising edge of the clock, the PD output 'Up' will be low and 'Dw' will be high, so that the capacitor in the loop filter will be discharged to a lower level. Then the delay of the VCDL will be smaller. When the loop is in-lock, the data eye center will be located exactly at the rising edge of the clock.

#### 2.1.1 Dynamic bang-bang PD

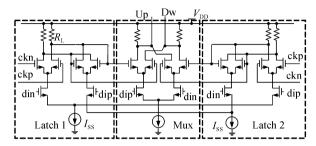

To compare random data transitions to the clock to provide a signal that represents the phase error, a phase detector (PD) is needed in the DLL. As shown in Fig. 2, the PD is a double-edge-triggered D-flip-flop (DFF), which consists of two latches and a multiplexer. The reference clock (ckp,ckn) is sampled alternately by two latches. The multiplexer will alternatively select the regenerated signal of the two latches for the PD's output. Assuming a gain of 1 for the multiplexer, the output of the PD will be equal to one of the regenerated signals of the two latches, and the output will change only when a data transition occurrs.

At every transition of the input data, the reference clock is sampled by the input NRZ data. When the data eye center leads the rising edge of the clock, the PD output (Qp, Qn) will be high.

On the other hand, when the data eye center lags the rising edge of the clock, the PD output (Qp, Qn) will be low. The output of the PD indicates a clear DC component driving the loop towards lock.

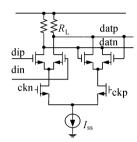

Fig. 2 Circuit diagram of the dynamic PD

#### 2.1.2 Loop filter

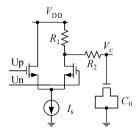

As shown in Fig. 3, the PD outputs (Qp, Qp) are used to control a current source. The loop filter is charged or discharged according to the polarity of the PD output. The DC component of the loop filter's output drives the loop towards lock. All the components are fully integrated on chip.

Fig. 3 Circuit diagram of the loop filter

#### 2.1.3 Voltage controlled delay line (VCDL)

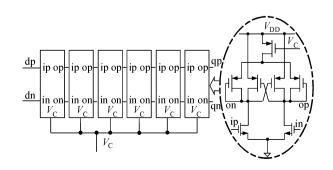

For continuous delay adjustment, an analog VCDL is used in the DLL. As shown in Fig. 4, the VCDL consists of six delay stages. The bandwidth of the delay cell is designed to be larger than the data rate to avoid serious signal distortion.

Fig. 4 Circuit diagram of the VCDL

#### 2. 2 Data decision circuit

The synchronized data is sampled by the reference clock in the data decision circuit. The circuit is implemented with a conventional D-flip-flop that consists of master-slave latches. Figure 5 shows a schematic of one latch. It is a modified source-coupled FET logic (SCFL) latch where the conventional two source followers are removed to save power.

Fig. 5 Circuit diagram of the latch

### 3 Application: used in SFI-5

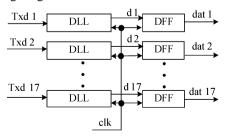

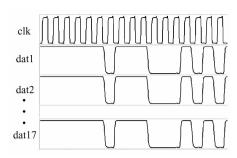

There are 16 parallel data channels and a 17th deskew channel between the SerDes device and the framer IC in SFI-5. A parallel DR circuit is needed to recover the 17-channel parallel data. The DR circuit in this design could be conveniently used for SFI-5. As shown in Fig. 6, seventeen identical 2.5Gb/s/ch DR circuits are integrated together to realize the parallel data recovery. For parallel data recovery, a reference clock is provided at the system level, so that the clock is called a global reference clock. In each channel, the input data is synchronized with the global reference clock. Figure 7 shows the simulation waveform of the global clock output and the 17-channel recovered data. Compared with the conventional approaches<sup>[2,3]</sup>, the parallel recovered data of this parallel DR circuit are bit-synchronous so that the following alignment circuit<sup>[2]</sup> can be avoided.

Fig. 6 Block diagram of the 17-channel DR

Fig. 7 Simulation waveform of the 17-channel DR

# 4 Measurement results of the single channel 2. 5Gb/s/ch DR IC

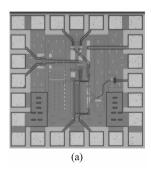

A single channel 2. 5Gb/s/ch DR IC was fabricated in TSMC 0. 18 $\mu$ m CMOS technology. Figure 8(a) shows a photograph of the IC. The chip area is  $675\mu$ m  $\times 675\mu$ m.

The circuit was measured on chip. The main testing instruments include an Advantest D3186 pulse pattern generator, an Advantest D3286 error detector, and an Agilent 86100A oscilloscope.

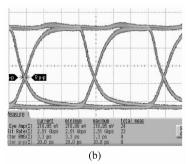

With a 1.8V supply, the power consumption is about 60mW. With input bit rates of  $2.3 \sim 2.8 \text{Gb/s}$ , the DLL can lock and the DR circuit can recover the input data with low RMS jitter. With  $2^{31}-1$  PRBS input data and a 2.5GHz reference clock, the eye diagram of the recovered 2.5Gb/s

Fig. 8 Photograph of the IC (a) and eye diagram of the recovered 2.5Gb/s data (b)

data is shown in Fig. 8 (b). The RMS jitter of the recovered 2.5 Gb/s data is 3.3 ps and the peak-to-peak (p-p) jitter is 20 ps. Using an Advantest D3186 and D3286 for BER testing, the sensitivity of the single channel DR was found to be less than  $20\,\mathrm{mV}$  with  $10^{-12}$  BER. The BER performance is guaranteed by the inherited DLL in the DR.

Compared with the DR circuits reported in previous papers, the jitter performance of this design is better. In Ref. [5], the p-p jitter was 60ps with 2.3Gb/s input data. In Ref. [6], the RMS jitter of the recovered 2.5Gb/s data was 10ps. In Ref. [7], a simulated eye diagram of the 2.5Gb/s CDR indicated that the jitter was larger than this design. The better jitter performance is achieved in this design because a reference clock is used and the center of the input data eye is aligned to the rising edge of the reference clock by the DLL.

#### 5 Conclusions

A 2.5Gb/s/ch data recovery circuit was designed for an SFI-5 interface. A DLL was used to place the center of the data eye exactly at the rising edge of the data-sampling clock. For parallel data recovery applications, all the parallel recov-

ered data are synchronized with the global reference clock so that they are bit-synchronous. Simulation and test results indicate that this design is suitable for parallel data recovery application in an SFI-5 interface.

#### References

- [1] Dartneil P. Serdes framer interface level 5 (SFI-5); implementation agreement for 40Gb/s interface for physical layer devices. Optical Internetworking Forum, 2002

- [2] Xu Min. An SFI-5 compliant 16:4 multiplexer for OC-768 systems. IEEE International Solid-State Circuits Conference, 2003, 1:283

- [3] Yang Fuji. A 1.5-V 86-mW/ch 8-channel 622-3125Mb/s/ch CMOS SerDes macrocell with selectable Mux/Demux ratio. ISSCC Digest of Technical Papers, 2002:48

- [4] Pottbacker A. A Si bipolar phase and frequency detector IC for clock extraction up to 8Gb/s. IEEE J Solid-State Circuits, 1992, 27(12):1747

- Soyuer M. A monolithic 2.3-Gb/s 100-mW clock and data recovery circuit in silicon bipolar technology. IEEE J Solid-State Circuits, 1993, 28(12):1310

- [6] Pallotta A. A low-power clock and data recovery circuit for 2.5Gb/s SDH receivers. Low Power Electronics and Design, 2000:67

- [7] Muller P. Top-down design of a low-power multi-channel 2.5-Gbit/s/channel gated oscillator clock-recovery circuit. Design, Automation and Test in Europe, Proceedings, 2005: 258

# 2. 5Gb/s/ch 0. 18μm CMOS 数据恢复电路

刘永旺\* 王志功 李 伟

(东南大学射频与光电集成电路研究所,南京 210096)

摘要:设计了一个应用于 SFI-5 接口的 2.5 Gb/s/ch 数据恢复电路.应用一个延迟锁相环,将数据的眼图中心调整为与参考时钟的上升沿对准,因而同步了并行恢复数据,并降低了误码率.采用 TSMC 标准的 0.18 $\mu$ m CMOS 工艺制作了一个单通道的 2.5 Gb/s/ch 数据恢复电路,其面积为 0.46mm².输入  $2^{31}-1$  伪随机序列,恢复出 2.5 Gb/s 数据的均方抖动为 3.3 ps. 在误码率为  $10^{-12}$  的条件下,电路的灵敏度小于 20 mV.

关键词:数据恢复;延迟锁相环;位同步

**EEACC:** 1200

中图分类号: TN929 文献标识码: A 文章编号: 0253-4177(2007)05-0692-04