## Bandgap Reference Design by Means of Multiple Point Curvature Compensation

Jiang Tao† and Yang Huazhong

(Department of Electronics Engineering, Tsinghua University, Beijing 100084, China)

Abstract: A new method, namely multiple point curvature compensation (MPCC), is proposed for the design of a bandgap reference, and its design principles, theoretical derivation, and one feasible circuitry implementation are presented. Being different from traditional techniques, this idea focuses on finding multiple temperatures in the whole range at which the first order derivatives of the output reference voltage equal zero. In this way, the curve of the output reference voltage is flattened and a better effect of curvature compensation is achieved. The circuitry is simulated in ST Microelectronics  $0.18\mu m$  CMOS technology, and the simulated result shows that the average temperature coefficient is only 1ppm/°C in the range from -40 to 125°C.

Key words: bandgap reference; curvature compensation; sub-threshold circuit

**EEACC:** 2570D

#### 1 Introduction

Bandgap voltage references (BGR) have wide applications in various analogue and digital systems, such as analogue-to-digital (ADC) and digital-to-analogue converters (DAC), voltage regulators, and phase-locked loops. The performance and accuracy of these circuits depends directly on the BGR characteristics, i. e. nominal voltage reference value ( $V_{\text{REF}}$ ), temperature coefficient (TC), and temperature range (TR). Generally, first-order compensated BGR can achieve a TC of about  $20 \sim 60 \mathrm{ppm/C}$ , while in some high-performance applications, such as high-resolution ADC and DAC, the curvature-compensation technique is required to further reduce the TC of the BGR. Traditionally, such techniques include quadratic temperature compensation[1], exponential temperature compensation[2], linearization of VBE<sup>[3]</sup>, piecewise-linear curvature correction<sup>[4]</sup>, resistor temperature compensation[5], and the NPN-and-PNP-generated current compensation[6], most of which concentrate on cancelling the high-order T terms of the Taylor series of the base-emitter voltage  $V_{\rm BE}$  ( T ) of a bipolar transistor at a single reference temperature  $T_r$  over the whole temperature range, and have such drawbacks as more complicated circuits, larger chip area and more complex fabrication processes.

A new idea for curvature compensation of BGRs and a kind of practical circuitry with its simulation results realizing the idea are proposed in this paper. The idea focuses on finding multiple temperatures in the whole range at which the first order derivatives of the output voltage with respect to temperature equal zero. In this way, the curve of the output voltage is flattened, and a better effect of curvature compensation is achieved.

## 2 General principles of bandgap references

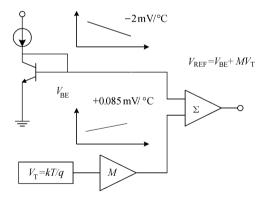

The basic idea of a BGR is to compensate the negative TC of the base-emitter voltage  $V_{\rm BE}(T)$  with the positive one of  $\Delta V_{\rm BE}(T)$ , which is the difference in junction potential between two junctions operating at different current densities. The output voltage, which is actually a weighted sum of  $V_{\rm BE}(T)$  and  $\Delta V_{\rm BE}(T)$ , can attain a zero TC by proper weighting(Fig.1).

Suppose two bipolar transistors Q1 and Q2, whose saturation currents are  $I_{\rm S1}$  and  $I_{\rm S2}$ , are injected with collector currents of  $I_{\rm 1}$  and  $I_{\rm 2}$ , respectively. The difference of their base-emitter voltages can be written as<sup>[8]</sup>

<sup>†</sup> Corresponding author. Email: jiangtao00@ mails. tsinghua. edu. cn Received 24 October 2006, revised manuscript received 18 November 2006

$$\Delta V_{\rm BE}(T) = \frac{kT}{q} \left( \ln \frac{I_1}{I_{\rm S1}} - \ln \frac{I_2}{I_{\rm S2}} \right) = V_{\rm T} \ln \left( \frac{I_1}{I_2} \times \frac{I_{\rm S2}}{I_{\rm S1}} \right)$$

(1)

where k is the Boltzmann's constant, T is the absolute temperature, and q is the charge of an electron. Therefore,  $\Delta V_{\rm BE}$  (T) is proportional to the absolute temperature (PTAT).

On the other hand, the relationship of base-emitter voltage to temperature can be expressed  $as^{\llbracket 9 \rrbracket}$

$$V_{\text{BE}}(T) = V_{\text{G0r}} \left( 1 - \frac{T}{T_{\text{r}}} \right) + \frac{T}{T_{\text{r}}} V_{\text{BE}}(T_{\text{r}}) -$$

$$\eta V_{\text{T}} \ln \frac{T}{T_{\text{r}}} + V_{\text{T}} \ln \frac{I_{\text{C}}}{I_{\text{C}}(T_{\text{r}})}$$

(2)

Here,  $V_{\rm G0r}$  is the bandgap voltage of silicon extrapolated from a reference temperature  $T_{\rm r}$  to  $0{\rm K}$ ,  $\eta$  is a temperature constant depending on the technology, and  $I_{\rm C}$  is the collector current injected into the bipolar transistor.

Therefore the bandgap reference voltage can be given by

$V_{\rm REF}(T) = V_{\rm BE}(T) + M \Delta V_{\rm BE}(T) \qquad (3)$  If the ratio M is carefully selected,  $\Delta V_{\rm BE}(T)$  can compensate the first-order T term in  $V_{\rm BE}(T)$ , which is the principle of conventional first-order compensated BGRs.

Fig. 1 Hypothetical bandgap reference circuit<sup>[7]</sup>

# 3 Traditional high-order curvature compensation techniques

Conventional first-order compensated BGRs fail to compensate the high-order T terms, especially the  $V_{\rm T} \ln T$  term in  $V_{\rm BE}(T)$ , which can lead to an extra TC of about  $10 \sim 40 {\rm ppm/^{\circ}C}$ . To solve this problem, several techniques have been proposed.

The quadratic temperature compensation

technique<sup>[1]</sup> involves canceling the second-order T term of the Taylor series of  $V_{\rm BE}$  at  $T_{\rm r}$  by adding a PTAT<sup>2</sup> term to the reference voltage of a first-order BGR, while exponential temperature compensation<sup>[2]</sup> involves canceling or reducing the second- or higher-order T terms of  $V_{\rm BE}$  by adding an exponential function of temperature. As for the resistor temperature compensation<sup>[5]</sup>, it also demands a Taylor series of reference voltage at  $T_{\rm r}$  in which the second-order T terms of  $V_{\rm BE}$  are compensated by the temperature characteristic of different types of resistors.

However, the Taylor formula of finite terms can only guarantee a relatively high accuracy in a very small neighborhood around the reference temperature  $T_{\rm r}$ . That is, the error between the actual and the polynomial value can be large when the temperature T is far from  $T_{\rm r}$ . Unfortunately, in most applications the TR concerned can reach as high as one hundred or more degrees, but the compensation for the Taylor polynomial of  $V_{\rm BE}$  is usually to a second-order T term in such circuits. Apparently, the accuracy of such curvature compensation techniques is not so high at some temperatures, i.e. the ends of the temperature range.

### 4 Multi-point curvature compensation technique

Most conventional first-order and traditional high-order BGRs limit their focus to a single reference point  $T_r$  in a relatively large temperature range, hoping that at this temperature the first- or even second-order derivative of reference voltage respect to T could be made zero. However, this can still lead to a fairly large error at other temperatures far away from  $T_r$ . Consider, if we properly design the circuit and find several local extrema (peak or valley) of the curve of reference voltage in the whole temperature range, the curve versus temperature will certainly be flattened and the accuracy be improved.

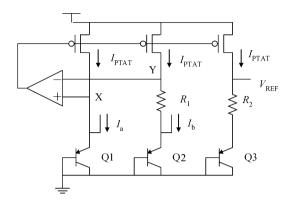

The idea of the proposed curvature-compensation technique is illustrated in Fig. 2. All the pMOS transistors have the same size so that they provide the same drain current, if the channel-length modulation effect is neglected. The bipolar transistor Q2 has an area that is N times that of Q1 and Q3 so that the saturation current of Q2 is

also N times higher. The ratio of resistor  $R_2$  to  $R_1$  is M. We denominate the emitter currents of Q1, Q2, and Q3 by  $I_{Q1}$ ,  $I_{Q2}$ , and  $I_{Q3}$ , respectively.

Fig. 2 Structure of the proposed MPCC BGR

The output reference voltage can be expressed according to Eqs. (2) and (3) by

$$V_{\text{REF}}(T) = V_{\text{GOr}} \left( 1 - \frac{T}{T_{\text{r}}} \right) + \frac{T}{T_{\text{r}}} V_{\text{BE}}(T_{\text{r}}) - \eta V_{\text{T}} \ln \frac{T}{T_{\text{r}}} + V_{\text{T}} \ln \frac{I_{\text{Q3}}}{I_{\text{O2}}(T_{\text{r}})} + M V_{\text{T}} \ln \left( \frac{I_{\text{Q1}}}{I_{\text{O2}}} N \right) (4)$$

Considering currents  $I_{\rm Ql}$ ,  $I_{\rm Q2}$  and  $I_{\rm Q3}$ , and neglecting the channel-length modulation effect of transistors and the thermal effect of resistors, we have

$$I_{Q1} = I_{PTAT} + I_a$$

$$I_{Q2} = I_{PTAT} + I_b$$

$$I_{O3} = I_{PTAT}$$

(5)

The potentials at nodes X and Y are guaranteed to be equal by negative feedback of an operational amplifier. In the design, currents  $I_{\rm a}$  and  $I_{\rm b}$  can be made much smaller than  $I_{\rm PTAT}$ , and therefore  $I_{\rm Ol}$   $\approx I_{\rm O2}$  and the PTAT current is given by

$$I_{\text{PTAT}} = \frac{\Delta V_{\text{BE}}}{R_1} = \frac{V_{\text{T}}}{R_1} \ln \left( \frac{I_{\text{Q1}}}{I_{\text{Q2}}} \times \frac{I_{\text{S2}}}{I_{\text{S1}}} \right) \approx \frac{V_{\text{T}}}{R_1} \ln N$$

(6)

Computing the first-order derivative of the reference voltage respect to temperature and substituting  $I_{Q1}$ ,  $I_{Q2}$  and  $I_{Q3}$  in Eq. (5) for those in Eq. (4), we have

$$\frac{\partial V_{\text{REF}}}{\partial T} \approx \frac{-V_{\text{GOr}} + V_{\text{BE}}(T_{\text{r}})}{T_{\text{r}}} - (\eta - 1) \frac{k}{q} \left( 1 + \ln \frac{T}{T_{\text{r}}} \right) + \frac{k}{q} M \ln N + MV_{\text{T}} \left( \frac{1}{I_{\text{Cl}}} \times \frac{\partial I_{\text{Ql}}}{\partial T} - \frac{1}{I_{\text{Cl}}} \times \frac{\partial I_{\text{Ql}}}{\partial T} \right) \tag{7}$$

Notice that currents  $I_{\rm a}$  and  $I_{\rm b}$  are part of currents  $I_{\rm Ol}$  and  $I_{\rm O2}$ , respectively, and we can safely assume that they have a relationship to temperature as below by design:

$$I_{a} = a_{0} + a_{1}T + a_{2}T^{2} + a_{3}T^{3}$$

$$I_{b} = b_{1} + b_{1}T + b_{2}T^{2} + b_{3}T^{3}$$

(8)

To make Eq. (6) hold, we must make sure that

$$\mid I_a \mid \ll \mid I_{\text{PTAT}} \mid$$

,  $\mid I_b \mid \ll \mid I_{\text{PTAT}} \mid$  (9)

Thus the first-order derivatives respect to temperature can be written as

$$\frac{\partial I_{a}}{\partial T} = a_{1} + 2a_{2}T + 3a_{3}T^{2}$$

$$\frac{\partial I_{b}}{\partial T} = b_{1} + 2b_{2}T + 3b_{3}T^{2}$$

(10)

Therefore we have

$$f(T) = \frac{\partial V_{\text{REF}}}{\partial T} \approx \frac{-V_{\text{GOr}} + V_{\text{BE}}(T_{\text{r}})}{T_{\text{r}}} - \frac{(\eta - 1) \frac{k}{q} \left(1 + \ln \frac{T}{T_{\text{r}}}\right) + \frac{k}{q} M \ln N + \frac{V_{\text{T}}}{I_{\text{PTAT}}} \left(\frac{\partial I_{\text{a}}}{\partial T} - \frac{\partial I_{\text{b}}}{\partial T}\right)$$

$$= \frac{-V_{\text{GOr}} + V_{\text{BE}}(T_{\text{r}})}{T_{\text{r}}} - (\eta - 1) \frac{k}{q} \left(1 + \ln \frac{T}{T_{\text{r}}}\right) + \frac{k}{q} M \ln N + M \frac{R_{1}}{\ln N} \left[(a_{1} - b_{1}) + 2(a_{2} - b_{2})T + 3(a_{3} - b_{3})T^{2}\right]$$

(11)

Now our target is to set up proper  $a_i$  and  $b_i$  (i = 1,2,3) so that we can find three points in the whole temperature range  $[T_L, T_H]$  satisfying  $T_1 < T_r < T_3$  and  $f(T_1) = f(T_r) = f(T_3) = 0$ . Assume

$$f_{1}(T) = \frac{-V_{G0r} + V_{BE}(T_{r})}{T_{r}} - (\eta - 1) \frac{k}{q} \left( 1 + \ln \frac{T}{T_{r}} \right) + \frac{k}{q} M \ln N$$

$$f_{2}(T) = K \frac{R_{1}}{\ln N} [(a_{1} - b_{1}) + 2(a_{2} - b_{2})T + 3(a_{3} - b_{3})T^{2}]$$

(12)

To make  $f(T_r) = 0$ , we just need to assure that

$$\frac{-V_{G0r} + V_{BE}(T_r)}{T_r} + (1 + M \ln N - \eta) \frac{k}{q} = 0$$

$$(13)$$

$$(a_1 - b_1) + 2(a_2 - b_2) T_r + 3(a_3 - b_3) T_r^2 = 0$$

(14)

In fact, Equation (13) is what returns to the conventional first-order BGR circumstances and can be easily satisfied by carefully selecting M and N. On the other hand, Equation (14) gives one more

Another two constraints are that at selected  $T_1$  and  $T_3$ , we must make sure that  $f_1$  ( $T_1$ ) =  $-f_2$ ( $T_1$ ) and  $f_1$ ( $T_3$ ) =  $-f_2$ ( $T_3$ ), that is

constraint that  $a_i$  and  $b_i$  (i = 1, 2, 3) must meet.

$$K \frac{R_1}{\ln N} [(a_1 - b_1) + 2(a_2 - b_2) T_1 + 3(a_3 - b_3) T_1^2] =$$

$$(\eta - 1) \frac{k}{q} \ln \frac{T_1}{T_r}$$

$$K \frac{R_1}{\ln N} [(a_1 - b_1) + 2(a_2 - b_2) T_3 + 3(a_3 - b_3) T_3^2] = (\eta - 1) \frac{k}{q} \ln \frac{T_3}{T_r}$$

(15)

Given a certain  $\eta$  determined by technology and having obtained M and N from Eq. (13), and being aware of the precondition given by Eq. (9), we can certainly find  $a_i$  and  $b_i$  (i = 1, 2, 3) from Eqs. (14) and (15).

Now that we have proved the existence of a certain circuit in which the reference voltage can have several first-order derivative zeros in the whole temperature range, in the practical design we can replace the polynomial temperature-related current in the derivation with an exponential temperature-related one. With the help of circuit simulation software, the accurate sizes of transistors in the circuit can be determined.

## 5 Circuit design and simulation results

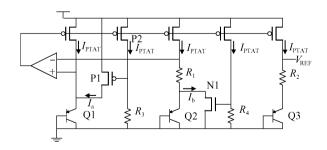

The schematic of our MPCC BGR is given in Fig. 3. In this circuit, currents  $I_a$  and  $I_b$  are produced by MOS transistors operating in the subthreshold region, and the pMOS transistor of the current source for the bipolar transistor Q1 is 4 times larger than the others. pMOS transistor P1 is to inject current into Q1, while nMOS transistor N1 is to extract current from bipolar transistor Q2, that is, a negative injection of current. As for

Fig. 3 Schematic of the proposed MPCC BGR

a transistor operating in the sub-threshold region, its drain current can be expressed as [8]

$$I_{\rm D} \cong \frac{W}{L} I_{\rm D0} \exp\left(\frac{V_{\rm GS}}{V_{\rm T}}\right) \tag{16}$$

in which  $I_{\rm D0}$  is a parameter determined by the

process, and  $V_T$ , W and L are the threshold and the dimensions of the transistor, respectively. Now we can write  $I_a$  and  $I_b$  as

$$I_{a} \cong \frac{W_{\text{Pl}}}{L_{\text{Pl}}} I_{\text{Do,Pl}} \exp\left(\frac{V_{\text{DD}} - R_{3} I_{\text{PTAT}}}{V_{\text{T}}}\right)$$

$$I_{b} \cong -\frac{W_{\text{Nl}}}{L_{\text{Nl}}} I_{\text{Do,Nl}} \exp\left(\frac{R_{4} I_{\text{PTAT}}}{V_{\text{T}}}\right)$$

(17)

and then we can safely write Eq. (17) as a Taylor series within the allowable accuracy, so the parameters  $a_i$  and  $b_i$  (i = 1, 2, 3) in Eq. (8) are functions of the transistors' dimensions and resistors' values.

$$a_i = g_i(W_{P1}, L_{P1}, R_3)$$

$b_i = h_i(W_{N1}, L_{N1}, R_4)$ ,  $i = 1, 2, 3$  (18)

Taking Eq. (18) into Eq. (15), we can conclude that in theory any arbitrary  $T_1$  and  $T_3$  can be obtained by choosing  $W_{\rm Pl}$ ,  $L_{\rm Pl}$ ,  $W_{\rm Nl}$ ,  $L_{\rm Nl}$ ,  $R_1$ ,  $R_3$  and  $R_4$ , and the solutions might not be unique. Therefore, the circuit in Fig. 3 can successfully realize the function demonstrated in Fig. 2. However, the required caculation is rather complicated, and simulation by EDA tools is a must.

Compared to the proposed circuit in Ref. [10], the part of this circuit formed by pMOS transistors P1 and P2 and resistor  $R_3$  can generate one more zero of the first-order derivative of the reference voltage respect to temperature, at a lower temperature, and therefore our MPCC BGR can further achieve a much lower TC over a wide temperature range.

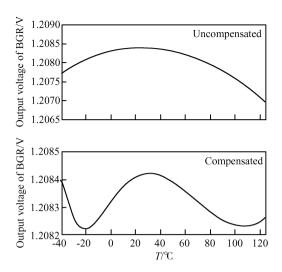

The circuit is simulated in ST microelectron-simulator. The supply voltage is 3.3V and the total current dissipated is about  $90\mu$ A. The OPA employed in this bandgap is a simple two-stage one that can achieve a gain of about 100dB with a phase margin of about 64°. Choosing a typical model, in a temperature range between - 40 and 125°C, the TC of the compensated BGR can achieve a value as low as 1ppm/°C, as shown in Fig. 4. We can see that before compensation the difference between the largest and smallest output voltages over the temperature range is about 1.5mV, while the same value is reduced to only about 200 µV after compensation. Meantime, for the topology in Ref.  $\lceil 10 \rceil$  the same quantity is about 700 µV. Besides, when choosing FF and SS models respectively, this value can reach about 700 and  $600\mu V$ , which also improve the temperature characteristic of the BGR a lot.

Fig. 4 Reference voltage before and after compensation

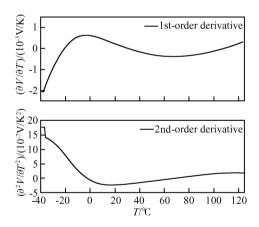

If we check the curve of the first- and second-order derivatives of the reference voltage respect to temperature, we can observe that there are three and two zeros in the whole temperature range, respectively. Remember that in most traditional high-order curvature compensation techniques there is only one zero of the derivative.

Fig. 5 First- and second-order derivatives of reference voltage with respect to temperature

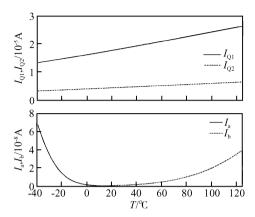

Finally, we check the curve of currents  $I_a$  and  $I_b$  with respect to temperature, and their values are really much less than those of  $I_{\rm Ql}$  and  $I_{\rm Q2}$ , which fit the assumption we made before. In fact, the realization of  $I_a$  and  $I_b$  is one of the most important factors in this circuit. Were we to find a better circuit realizing such currents, we may find even more than three zeros of the first-order derivative of the reference voltage respect to tem-

perature, and the temperature performance of the BGR may be further improved.

Fig. 6 Current  $I_{Q1}$  and  $I_{Q2}$  versus  $I_a$  and  $I_b$

#### 6 Conclusion

A new multiple-point curvature-compensated CMOS BGR has been proposed. Temperature compensation is achieved by setting more than one zero of first-order derivatives of the reference voltage respect to temperature in the whole temperature range. Compared to the traditional curvature compensation technique, this method is a kind of innovation of the design methodology. The proposed BGR can achieve a fairly small TC and is very simple, requiring only four more MOS transistors and two more resistors.

The circuit is simulated in ST Microelectronics  $0.18\mu m$  technology and under typical conditions the compensated BGR can achieve a temperature coefficient of 1ppm/°C over the temperature range of -40 to 125°C. Simulations results convinced us of the feasibility of the MPCC method for BGR design, and in the future the circuit will be taped out and tested.

#### References

- [1] Song B S, Gray P R. A precision curvature-compensated CMOS bandgap voltage reference. IEEE J Solid-State Circuits, 1983, SC-18(6):634

- [2] Lee I, Kim G, Kim W. Exponential curvature-compensated BiCMOS bandgap voltage references. IEEE J Solid-State Circuits, 1994, 29(11):1396

- [3] Malcovati P, Maloberti F, Pruzzi M, et al. Curvature compensated BiCMOS bandgap with 1V supply voltage. IEEE J Solid-State Circuits, 2001, 36(7):1076

- Rincon-Mora G A, Allen P E. A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap voltage refer-

ence. IEEE J Solid-State Circuits, 1998, 33(10): 1551

- [5] Leung K N, Moke K T, Leung C Y. A 2V 23A curvature compensated CMOS bandgap voltage reference. IEEE J Solid-State Circuits, 2003, 38(3):561

- [6] Ker M D, Chen J S. New curvature-compensation technique for CMOS bandgap voltage reference with sub-1V operation. IEEE Trans Circuits Syst II: Express Briefs, 2006, 53 (8):667

- [7] Gray P, Meyer R. Analysis and design of analog integrated

- circuit. 4th ed. New York; Wiley, 2001; ch4

- [8] Razavi B. Design of analog CMOS integrated circuits. New York, McGraw-Hill, 2001; ch11

- [10] Wu Guoping, Huang Nianya, Liu Guizhi. Second-order curvature compensation bandgap reference. Chinese Journal of Electron Devices, 2005, 28(3), 696

### 多点曲率补偿的带隙基准电压源设计方法

姜 韬 杨华中

(清华大学电子工程系, 北京 100084)

摘要:提出了一种对带隙基准电压进行多点曲率补偿的新思路,给出了它的设计原理、推导过程和一种实现电路.与传统的曲率校正方法不同,分布式曲率补偿着眼于在整个温度范围内寻找多个基准输出电压对温度的一阶导数的零点,从而限定基准输出电压随温度变化曲线的幅度,使曲线更平缓,达到提高曲率补偿效果的目的.采用 ST 公司的  $0.18\mu m$  CMOS 工艺对实现电路进行了电路模拟,结果表明,在  $-45\sim120$  C 的温度范围内,采用该方法设计的带隙基准电源的温度系数仅为 1ppm/C.

关键词:带隙基准;曲率补偿;亚阈值区

**EEACC:** 2570D

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2007)04-0490-06