## **Back-Gate Effect of SOI LDMOSFETs\***

Bi Jinshun<sup>†</sup>, Song Limei, Hai Chaohe, and Han Zhengsheng

$(\textit{Institute of Microelectronics}\,,\,\,\textit{Chinese Academy of Sciences}\,,\,\,\textit{Beijing}\quad 100029\,,\,\,\textit{China})$

Abstract:  $0.5\mu\text{m}$ -gate-length lateral double-diffused metal-oxide-semiconductor field-effect transistors (LDMOSFETs) with low barrier body contact (LBBC) and body tied to the source (BTS) were fabricated on silicon-on-insulator (SOI) substrates. The back-gate effects on front-channel subthreshold characteristics, on-resistance, and off-state breakdown characteristics of these devices are studied in detail. The LDMOSFETs with the LBBC structure show less back-gate effect than those with the BTS structure due to better control of the floating body effect and suppression of the parasitic back-channel leakage current. A model for the SOI LDMOSFETs has been given, including the front- and back-channel conductions as well as the bias-dependent series resistance.

Key words: SOI; LDMOSFET; back-gate effect

**EEACC**: 2560

### 1 Introduction

Power lateral double-diffused transistors (LD-MOSFETs) on silicon-on-insulator (SOI) substrates have attracted considerable interest for applications in high performance RF power amplifiers [1~3]. The advantages of SOI technology include the superior isolation, reduced parasitic capacitances, less leakage current, and better high temperature performance compared to the traditional junction isolation in bulk technology [4.5]. Moreover, SOI technology uses a high resistivity silicon substrate to reduce substrate RF power loss and noise crosstalk [6.7].

Breakdown voltage and on-resistance are key parameters of SOI LDMOSFETs, as discussed in Refs. [8  $\sim 10$ ]. However, the impact of the back-gate, an additional terminal introduced by the buried oxide to the LDMOSFETs, on breakdown voltage and on-resistance is seldom studied. In practice, if two SOI LDMOSFETs are used in series, the potential of the source and body of the top device in the stack is raised with respect to the back-gate. Thus, this device is biased by the back-gate although the back-gate is not biased intentionally. So it is necessary for the designers to understand the back-gate effect of SOI LD-MOSFETs.

This paper discusses the back-gate effect of SOI LDMOSFETs and presents a model of SOI LDMOSFETs.

### 2 Device fabrication

The  $40\mu\text{m}/0.5\mu\text{m}$  LDMOSFETs were fabricated on 100mm SIMOX (separated by implanted oxygen) wafers from Simgui Corp, with material parameters as follows: p(100),  $15\sim25\Omega$  · cm, 198nm-thick top silicon film, and a 382nm-thick buried oxide layer. Device A is a BTS (body tied to the source) structure LDMOSFET with a 0.5 $\mu$ m drift region length, and device B is a LBBC (low barrier body contact) structure LDMOSFET with a 0.3 $\mu$ m drift region length.

LOCOS (local oxidation of silicon) isolation was used. The gate oxide thickness is 6nm. The p<sup>+</sup> implantation for devices A and B was to implant boron with a dose of  $1 \times 10^{14}$  cm<sup>-2</sup> and an energy of 25keV. The ndrift region was created by a phosphorous implant of dose  $8 \times 10^{12} \, \text{cm}^{-2}$  and energy  $30 \, \text{keV}$ . The n-LDD region (body contact region and drift region were masked) was implanted by arsenic with a  $3 \times 10^{14}$  cm<sup>-2</sup> dose and 25keV of energy. The n<sup>+</sup> source and drain regions were formed by a masked implant of  $5 \times 10^{15}$ cm<sup>-2</sup> and 25keV of energy. The n<sup>+</sup> implant mask defines the length of the drift region. The dopants were activated by a 6s,1030°C RTA process. In order to reduce the sheet resistance of the source, gate, and drain of the RF LDMOSFETs and improve the RF performance, a salicidation technique<sup>[11]</sup> based on SiO<sub>2</sub>/ Si<sub>3</sub>N<sub>4</sub> dual sidewalls was developed and applied to thin-film SOI LDMOSFETs with thin gate oxide. The

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60576051) and the State Key Development Program for Basic Research of China (No. 2006CB3027-01)

<sup>†</sup> Corresponding author. Email: bravehawk@126.com

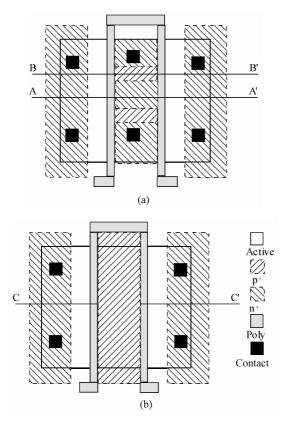

Fig. 1 (a) Layout of the BTS structure LDMOSFET for device A;(b) Layout of the LBBC structure LDMOSFET for device B

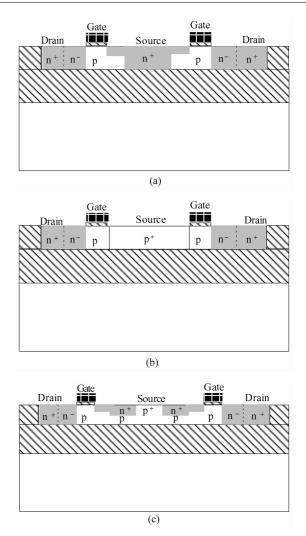

layouts of devices A and B are shown in Fig. 1, and their cross-sections along lines A-A', B-B' and C-C' are illustrated in Fig. 2.

The LBBC structure LDMOSFET is close to that of a BTS structure LDMOSFET with two main exceptions; (1) The source does not extend completely through the top silicon film and the region below the source is heavily p<sup>+</sup> doped; (2) Next to the source is a heavily doped p-type region that acts as the body contact.

# 3 Experimental results and discussion

After the formation of the SOI LDMOSFETs, their front-channel and back-channel properties have been characterized by a Keithley 4200SCS semiconductor characteristics system. Subscripts 1 and 2 indicate the front- and back-channels.

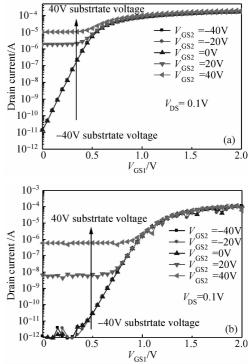

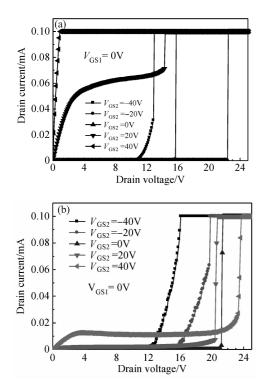

The front-channel subthreshold characteristics of devices A and B are shown in Fig. 3. The front-gate ( $V_{\rm GS1}$ ) and back-gate ( $V_{\rm GS2}$ ) voltages varied while maintaining a low drain bias ( $V_{\rm DS}=0.1\rm V$ ). The drain current versus front-gate voltage curves are functions of back-gate voltage both in devices A and B. When  $V_{\rm GS2}{<}0\rm V$ , the front-channel subthreshold characteristics almost remain the same as when the back-channel is off. When  $V_{\rm GS2}{>}0\rm V$ , the front-channel current increases with the back-gate voltage. In Fig. 3, the off-

Fig. 2 Cross-sections of devices A and B along lines A-A' (a), B-B' (b), and C-C' (c)

Fig. 3 Front-channel subthreshold characteristics of device A (a) and device B (b)

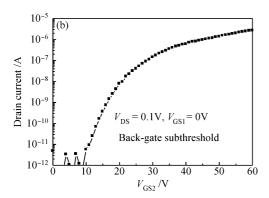

Back-channel subthreshold characteristics of device A (a) and device B (b)

state current of device A is greater than that of device B. When  $V_{GS2} = 20 \text{ V}$ , the off-state current of device A is 1.86  $\times$  10<sup>-6</sup> A, but that of device B is only 7.35  $\times$  $10^{-9}$  A. When  $V_{GS2} = 40$  V, the off-state current of device A is  $1.04 \times 10^{-5}$  A, but that of device B is only 5.  $89 \times 10^{-7}$  A.

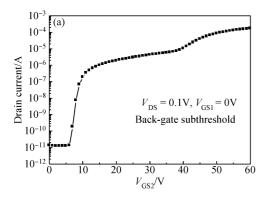

Figure 4 shows the back-channel subthreshold characteristics of devices A and B. The drain current  $1 \times 10^{-9}$  A/ $\mu$ m is defined as the back-channel threshold voltage point. The back-channel threshold voltages of devices A and B are 9 and 25V, respectively.

Device B has front-channel and back-channel subthreshold characteristics superior to device A because the LBBC structure keeps the floating body effects under better control and suppresses the backchannel from turning on effectively. Because the source region does not go completely through the top silicon film to the back-channel Si/SiO2 interface, a parasitic conducting path between the source and drain does not exist, even if the back-channel interface is inverted by the back-gate bias. The body contact barrier height and body resistance play key roles in suppressing floating body effects. The body contact barrier height of devices A and B is considered identical for the same p<sup>+</sup> implantation. For a one-sided BTS body contact structure device, the body resistance is given by

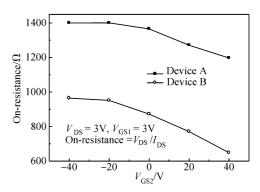

Fig. 5 On-resistance of devices A and B as they vary with backgate voltage

$$R_{\text{body}} = \frac{W_{\text{eff}}}{N_{\text{A}} q \mu_{\text{P}} L_{\text{eff}} \left( t_{\text{Si}} - \sqrt{\frac{4 \varepsilon_{0} \varepsilon_{\text{Si}} \phi_{\text{F}}}{q N_{\text{A}}}} \right)}$$

(1)

where  $N_A$  is the p-type doping concentration,  $\mu_p$  is the hole mobility,  $t_{Si}$  is the top silicon film thickness,  $W_{eff}$ and  $L_{\rm eff}$  are the effective channel width and length, and  $\phi_F$  is the Fermi potential. The body resistance greatly increases as device width increases and as gate length shrinks. The body resistance along the width direction is different. This conclusion is applicable to two-sided BTS body contact structure devices in this paper.

For the LBBC body contact structure device, the body resistance is given by

$$R_{\text{body}} = \frac{L_{\text{S}}}{N_{\text{A}} q \mu_{\text{P}} W_{\text{eff}} (t_{\text{Si}} - x_{\text{js}} - x_{\text{ds}})}$$

(2)

$$x_{\text{ds}} = \sqrt{\frac{2 \epsilon_{0} \epsilon_{\text{Si}} (2 \phi_{\text{F}} + V_{\text{sb}})}{q N_{\text{A}}}}$$

(3)

$$x_{\rm ds} = \sqrt{\frac{2\varepsilon_0\varepsilon_{\rm Si}(2\phi_{\rm F} + V_{\rm sb})}{qN_{\rm A}^{\prime}}}$$

(3)

where  $L_s$  is the source length,  $x_{js}$  is the source junction depth,  $x_{ds}$  is the source depletion width, and  $V_{sb}$  is the source/body voltage. The body resistance along the width direction is the same and proportional to the inverse of the device width.

Figure 5 shows that the back-gate voltage modifies the on-resistance of devices A and B, which is a critical parameter for LDMOSFETs. When  $V_{\rm GS2}$  < -20V, the on-resistance of devices A and B remains unchanged. In this region, the back-channel is accumulated and the bottom of the drift region is inverted, as shown in Fig. 6. The depletion width in the drift region reaches the maximum. When  $V_{GS2} > -20 \text{V}$ , the on-resistance of devices A and B decreases when the back-gate voltage increases. In this region, the backchannel leaks more current and the drift region becomes less resistive.

Figure 7 gives the breakdown characteristics of devices A and B. The back-channel turns on and becomes leakier when  $V_{\rm GS2}{>}20{

m V}$  in device A and  $V_{\rm GS2}$ = 40V in device B. It is common in both devices A and B that  $BV_{(V_{GS2} = 0V)} > BV_{(V_{GS2} = -20V)} >$

Fig. 6 Back Si/SiO $_2$  interface situation of device A (a) and device B (b)  $V_{\rm GS2} < -20 {\rm V}$

BV<sub>(V<sub>GS2</sub> = -40V)</sub>. When  $V_{GS2}$  = 20V in device B, the back-channel is in the off-state because the threshold voltage of the back-channel is 25V. But the bottom of the drift region is in accumulation, so the resistance of the drift region is lowered. The total on-resistance  $R_{ON}$  is the combined series resistance of source resistance  $R_{S}$ , channel resistance  $R_{CH}$ , drift region resistance  $R_{DF}$ , and drain resistance  $R_{D}$ . Thus,  $R_{ON}$  =  $R_{S}$  +  $R_{CH}$  +

Fig. 7 Breakdown characteristics of device A (a) and device B (b)

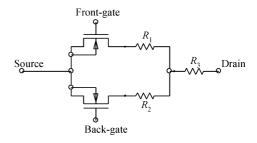

Fig. 8 SOI LDMOSFET circuit model

$R_{\rm DF}$  +  $R_{\rm D}$ . The drain voltage is divided among these resistors. Because  $R_{\rm DF}$  ( $V_{\rm GS2}=20{\rm V}$ )  $< R_{\rm DF}$  ( $V_{\rm GS2}=0{\rm V}$ ), the breakdown voltage at  $V_{\rm GS2}=20{\rm V}$  is a bit less than that at  $V_{\rm GS2}=0{\rm V}$  in device B.

An equivalent SPICE circuit is used to model the SOI LDMOSFETs, including the front-channel, backchannel, and all associated resistances in Fig. 8. The SPICE model for the LDMOSFETs is achieved by characterization of the front-channel for both bulk and SOI. Only the SOI LDMOSFET requires the characterization of a parasitic back-channel device.  $R_1$ and  $R_2$  are the unavoidable series resistance associated with front-channel and back-channel, while  $R_3$  is their common resistance, dominated by the drift region.  $R_3$  can be modulated by the back-gate voltage. The model is applicable to both the LBBC structure LDMOSFET and the BTS structure LDMOSFET. Because the source of device B does not extend completely through the top silicon film, the  $G_{\rm D2}$  of the LBBC structure LDMOSFET is smaller than that of the BTS structure LDMOSFET, which can be derived from Fig. 4.

These transistors are represented by their conductances  $G_{\mathrm{D1,2}}$ :

$$G_{\text{D1},2} = \frac{\mu_{1,2}^{0} C_{\text{ox1},2} W/L}{1 + \theta_{1,2}^{0} (V_{\text{G1},2} - V_{\text{T1},2})} (V_{\text{G1},2} - V_{\text{T1},2})$$

(4)

where W is the gate width,  $C_{\rm ox1}$  and  $C_{\rm ox2}$  are the gate oxide and BOX capacitances per unit area,  $V_{\rm T1,2}$  are the threshold voltage,  $\mu_{1,2}^0$  are the pure mobilities, and  $\theta_{1,2}^0$  are the mobility degradation factors at high vertical field.

Without series resistance effects, the intrinsic transconductance of the front- and back-channel is given by

$$g_{\text{m1,2}}^{0} = \frac{\mu_{1,2}^{0} C_{\text{ox1,2}} W / L V_{\text{D}}}{\left[1 + \theta_{1,2}^{0} (V_{\text{G1,2}} - V_{\text{T1,2}})\right]^{2}}$$

(5)

For single-channel operation mode, the influence of series resistances can be taken into account by replacing the coefficient  $\theta_{1,2}^0$  in Eqs. (4) and (5) with  $\theta_{1,2}^{[12]}$ :

$$\theta_{1,2} = \theta_{1,2}^0 + \mu_{1,2}^0 C_{\text{ox}1,2} W/L(R_{1,2} + R_3)$$

(6)

For double-channel operation mode, the total drain current is given by [13]

$$I_{\rm D} = \frac{G_{\rm D1} + G_{\rm D2} + G_{\rm D1}G_{\rm D2}(R_1 + R_2)}{1 + G_{\rm D1}G_{\rm D2}(R_1R_2 + R_1R_3 + R_2R_3) + G_{\rm D1}(R_1 + R_3) + G_{\rm D2}(R_2 + R_3)}V_{\rm D}$$

(7)

So the front gate transconductance is obtained as:

$$g_{m1} = \frac{(1 + R_2 G_{D2})^2 \frac{\partial G_{D1}}{\partial V_{G1}}}{\left[1 + G_{D1} G_{D2} (R_1 R_2 + R_1 R_3 + R_2 R_3) + G_{D1} (R_1 + R_3) + G_{D2} (R_2 + R_3)\right]^2} V_D$$

(8)

### 4 Conclusion

In summary, we presented the impact of the back-gate bias of SOI LDMOSFETs with LBBC and BTS structure on the front-channel subthreshold characteristics, on-resistance, and breakdown characteristics. LBBC structure LDMOSFETs have front-channel and back-channel characteristics superior to BTS structure LDMOSFETs for better control of floating body effects and suppression of back-channel leakage. A model for SOI LDMOSFETs has been conceived, including front- and back-channel conduction and bias-dependent series resistance.

Acknowledgments The authors would like to thank Yang Rong for his previous work, and Liu Mengxin and Fan Xuemei for their support in measurement.

### References

- [ 1 ] Shenai K, McShane E, Leong S K. Lateral RF SOI power MOSFETS with  $f_{\rm t}$  of 6. 9GHz. IEEE Electron Device Lett, 2000, 21 (10), 500

- [2] Tan Y, Kumar M, Sin J, et al. A SOI LDMOS technology compatible with CMOS, BJT, and passive components for fully-integrated RF power amplifiers. IEEE Trans Electron Devices, 2001, 48 (10):2428

- [3] McShane E, Shenai K. The design, characterization, and modeling

of RF LDMOSFETs on silicon-on-insulator material. IEEE Trans Electron Devices, 2002, 49(4):643

- [4] Kuo J B, Lin S C. Low-voltage SOI CMOS VLSI devices and circuits. John Wiley & Sons. Inc, 2001:4

- [5] Groeseneken G, Colinge J P, Maes H E, et al. Temperature dependence of threshold voltage in thin-film SOI MOSFET's. IEEE Electron Device Lett, 1990, 11, 329

- [6] Fiorenza J G, del Alamo J A. RF power performance of an LD-MOSFET on high-resistivity SOI. IEEE Electron Device Lett, 2005,26(1):29

- [7] Scholvin J, Fiorenza J G, del Alamo J A. Impact of substrate-surface potential on the performance of RF power LDMOSFETs on high-resistivity SOI. IEEE Trans Electron Devices, 2006, 53(7): 1705

- [8] Muller D, Giry A, Judong F, et al. High-performance 15-V novel LDMOS transistor architecture in a 0. 25-μm BiCMOS process for RF-power applications. IEEE Trans Electron Devices, 2007, 54 (4).861

- [ 9 ] Napoli E, Udrea F. Substrate engineering for improved transient breakdown voltage in SOI lateral power MOS. IEEE Electron Device Lett, 2006, 27(8):678

- [10] Conley J F, Vandooren A, Reiner L, et al. Radiation induced degradation of SOI n-channel LDMOSFETs. IEEE International SOI Conference, 2001:125

- [11] Yang R, Li J F, Qian H, et al. A short-channel SOI RF power LD-MOS technology with TiSi<sub>2</sub> salicide on dual sidewalls with cutoff frequency  $f_T \sim 19.3 \text{GHz}$ . IEEE Electron Device Lett, 2006, 27 (11).917

- [12] Cristoloveanu S, Li S S. Electrical characterization of SOI materials and devices. Norwell, MA, Kluwer, 1995

- [13] Ouisse T. Cristoloveanu S. Borel G. Influence of series resistances and interface coupling on the transconductance of fully depleted silicon-on-insulator MOSFET. Solid-State Electron, 1992, 35:141

### SOI LDMOSFET 的背栅特性\*

毕津顺\* 宋李梅 海潮和 韩郑生

(中国科学院微电子研究所,北京 100029)

摘要:在绝缘体上硅衬底上,制备了栅长为  $0.5\mu$ m 的低势垒体接触结构和源体紧密接触结构的横向双扩散功率晶体管.详细研究了器件的背栅特性.背栅偏置电压对横向双扩散功率晶体管的前栅亚阈值特性、导通电阻和关态击穿特性均有明显影响.相比于源体紧密接触结构,低势垒体接触结构横向双扩散功率晶体管的背栅效应更小,这是因为低势垒体接触结构更好地抑制了浮体效应和背栅沟道开启.还介绍了一种绝缘体上硅横向双扩散功率晶体管的电路模型,其包含前栅沟道,背栅沟道和背栅偏置决定的串联电阻.

关键词: 绝缘体上硅; 横向双扩散功率晶体管; 背栅效应

**EEACC**: 2560

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2008)11-2148-05

<sup>\*</sup> 国家自然科学基金(批准号:60576051) 及国家重点基础研究发展规划(批准号:2006CB3027-01)资助项目

<sup>†</sup>通信作者.Email:bravehawk@126.com