# SBH adjustment characteristic of the dopant segregation process for NiSi/n-Si SJDs

Shang Haiping(尚海平)<sup>†</sup> and Xu Qiuxia(徐秋霞)

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract:** By means of analyzing the I-V characteristic curve of NiSi/n-Si Schottky junction diodes (NiSi/n-Si SJDs), abstracting the effective Schottky barrier height ( $\phi_{B, eff}$ ) and the ideal factor of NiSi/n-Si SJDs and measuring the sheet resistance of NiSi films ( $R_{NiSi}$ ), we study the effects of different dopant segregation process parameters, including impurity implantation dose, segregation annealing temperature and segregation annealing time, on the  $\phi_{B, eff}$  of NiSi/n-Si SJDs and the resistance characteristic of NiSi films. In addition, the changing rules of  $\phi_{B, eff}$  and  $R_{NiSi}$  are discussed.

Key words: NiSi/n-Si SJD; effective Schottky barrier height; dopant segregation process DOI: 10.1088/1674-4926/31/5/056001 PACC: 2560H

## 1. Introduction

As the feature dimensions of MOSFETs are scaling into the nanometer regime, metal S/D MOSFETs (SB MOSFETs) have been considered as the most promising candidate for conventional MOSFETs with impurity highly doped S/D. However, due to the high  $\phi_{B,eff}$  at the source/channel interface, SB MOSFETs still do not achieve the same current characteristics as conventional MOSFETs<sup>[1]</sup>. So, intensive research on  $\phi_{B,eff}$  tuning techniques has been done, in order to enhance SB MOSFET performance.

Among the many  $\phi_{B,eff}$  tuning techniques, the post-silicide dopant segregation process<sup>[2]</sup> is not only compatible with the conventional CMOS technology, but also acquires good adjustment results. In this paper, we will investigate the effects of different dopant segregation process parameters, including impurity implantation dose, segregation annealing temperature and segregation annealing time, on the  $\phi_{B,eff}$  of NiSi/n-Si SJDs and the resistance characteristic of NiSi films. Furthermore, by comprehensive consideration of  $\phi_{B,eff}$  and  $R_{NiSi}$ , an optimization technique for the dopant segregation process is proposed.

## 2. Experiment

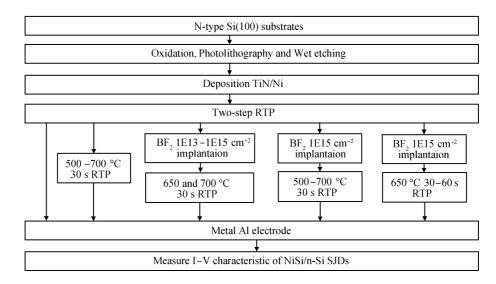

Blanket n-type (2–4  $\Omega$ -cm) Si(100) substrates were used in this work. Following oxidation, photolithography and the wet etching process, many circle windows with diameters of 250  $\mu$ m were formed. Then, TiN/Ni double-layer metal films were prepared on these wafers by alternate sputtering deposition of Ni film and TiN film. The Ni-silicide formation process was carried out *ex situ* by two-step rapid thermal processing (RTP) in high pure nitrogen ambient. The two-step Ni silicide formation process consists of the procedure of low temperature RTP, selective etching and higher temperature RTP<sup>[16]</sup>. Then the wafers were treated with different process conditions. Finally, Al was metalized on both sides of wafer to form a metal electrode. Figure 1 shows the experimental procedure diagram of this experiment. A four-point probe (FPP) was used to measure the sheet resistance of the formed Ni-silicide films. A Keithley-4200-SCS was used to measure the I-V characteristic of NiSi/n-Si at room temperature (300 K) under the conditions of avoiding light.

## **3.** Abstraction method of $\phi_{\text{B,eff}}$

According to one dimension thermionic emission theory<sup>[3]</sup>, the current transport equation for the practical SJD is given by Eq. (1).

$$I = AA^*T^2 \exp\left(-\frac{\phi_{\rm B,eff}}{V_{\rm T}}\right) \left[\exp\frac{V - IR}{nV_{\rm T}} - 1\right], \quad (1)$$

where A is the area of SJD,  $A^*$  is the effective Richardson constant for thermionic emission, T is the thermodynamic temperature in Kelvin,  $V_{\rm T} = kT/q$  is the thermal voltage, n is the ideality factor, R is the series resistance, and  $\phi_{\rm B,eff}$  is  $\phi_{\rm Bn,eff}$  or  $\phi_{\rm Bp,eff}$ , where  $\phi_{\rm Bn,eff}(\phi_{\rm Bp,eff})$  is the effective Schottky barrier height between metal and n-Si (p-Si) substrate. When  $V \ge V_{\rm T}$ and  $IR \le V$ , Equation (1) is reduced to

$$I = AA^*T^2 \exp\left(-\frac{\phi_{\rm B,eff}}{V_{\rm T}}\right) \exp\left(\frac{V - IR}{nV_{\rm T}}\right).$$

(2)

Then, taking  $\phi_{\text{Bn,eff}}$ , *n* and *R* as parameter variables and substituting all the constants, which are taken from Ref. [3], into Eq. (2) will give the relationship:

$$\exp\left[16.937 - \frac{\phi_{\text{B,eff}}}{0.026} + \frac{V - J \times 3.14 \times 0.000625R}{0.026n}\right] -J = 0,$$

(3)

where

$$J = I/A. \tag{4}$$

Using Eq. (3) as the fitting equation and selecting a proper fitting range, we can deduce *n* and  $\phi_{Bn,eff}$ , then  $\phi_{Bp,eff}$  can be calculated using

$$\phi_{\rm Bn,eff} + \phi_{\rm Bp,eff} = E_{\rm g}^{[3]},\tag{5}$$

where  $E_{\rm g}$  is the band gap of Si<sup>[3]</sup>.

Received 16 December 2009, revised manuscript received 7 January 2010

© 2010 Chinese Institute of Electronics

<sup>†</sup> Corresponding author. Email: erchou0028@163.com

Fig. 1. Experimental procedure diagram.

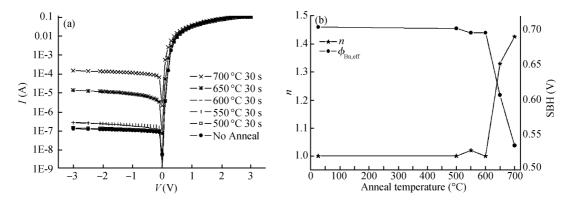

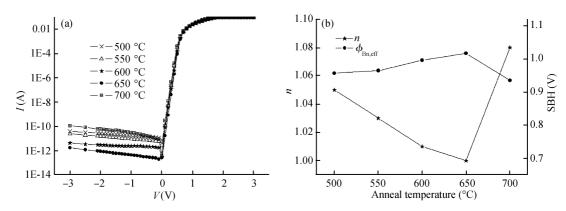

Fig. 2. Without and with various annealing temperatures of RTP for NiSi/n-Si SJDs. (a) I-V characteristic curve. (b)  $\phi_{Bn,eff}$  and *n* as a function of annealing temperature.

## 4. Results and analysis

In order to investigate the adjustment mechanism of the dopant segregation process, wafers were dealt with under different process conditions and  $\phi_{Bn,eff}$  and *n* were abstracted with the above mentioned method.

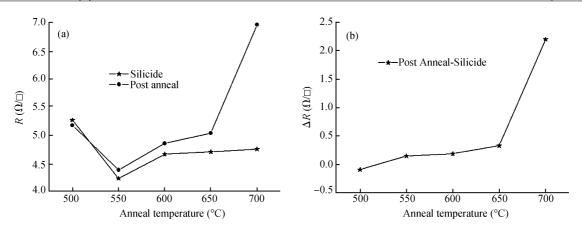

One group of wafers was treated with various annealing temperatures from 500 to 700 °C for 30 s. When the annealing temperature is lower than 600 °C, compared with the untreated NiSi/n-Si SJD, Figures 2 and 3 show that the reverse current has a little increase,  $\phi_{Bn,eff}$  has a small decrease,  $R_{NiSi}$ remains invariant when taking into account measurement error, and *n* is about 1. According to the measurement result of *n* and  $R_{NiSi}$ , we conclude that the interface characteristic of NiSi/n-Si is good and the NiSi film is stable after 500–600 °C 30 s annealing.  $\phi_{Bn,eff}$  is usually affected by the Fermi level pinning effect, and the interface trap density will decrease after RTP in high purity N<sub>2</sub>, resulting in a decrease in  $\phi_{Bn,eff}$  and an increase in the reverse current<sup>[4]</sup>.

However, when the annealing temperature reaches 650 and 700 °C, *n* and  $R_{\text{NiSi}}$  show a dramatic increase. These results show that there is a high resistance state Ni-silicide phase formation at the NiSi/n-Si interface<sup>[5]</sup>, which not only results in the increase in  $R_{\text{NiSi}}$  but also results in NiSi/n-Si interface

roughness<sup>[6, 7]</sup>. The rough NiSi/n-Si interface causes the reverse current to increase and  $\phi_{Bn,eff}$  to decrease, and finally degrades the electrical characteristics of NiSi/n-Si SJDs. These results coincide well with the experimental values as shown in Figs. 2 and 3.

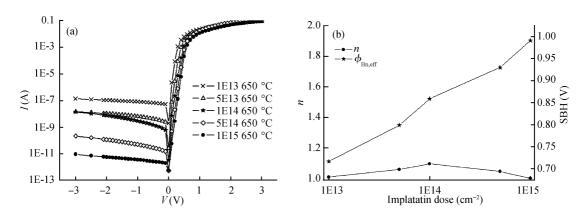

Another group of wafers was treated with various ion implantation doses  $(1 \times 10^{13} - 1 \times 10^{15} \text{ cm}^{-2})$  of BF<sub>2</sub> at the same implantation energy and segregation annealing with 650 °C 30 s and 700 °C 30 s. Figures 4(a) and 4(b) respectively show the I-V characteristic curve and the  $\phi_{Bn,eff}$  and n of NiSi/n-Si SJDs as a function of implantation dose, treated with various implantation doses and 650 °C 30 s segregation annealing. Figure 4 shows that the reverse current is decreased and  $\phi_{Bn,eff}$  is increased with increasing implantation dose, and *n* still stays at about 1. The main reason for this phenomenon is the impurity segregation effect in the post-silicide process. A mass of B atoms segregates at the NiSi/Si interface, shapes a thin spike with high doping concentration and the concentration increases with increasing implantation dose<sup>[8, 12]</sup>. This high concentration range of B accumulated at the NiSi/n-Si interface induces the  $\phi_{\text{Bn,eff}}$  increase<sup>[7, 17]</sup>. Furthermore, some of the segregated B atoms replace Si atoms at the Si side of interface, generating an electric dipole layer across the interface. Moreover, the B electric dipole layer is expected to be negatively charged

Fig. 3. With various annealing temperatures of RTP for NiSi/n-Si SJDs. (a)  $R_{\text{NiSi}}$  change curve. (b) NiSi sheet resistance ( $\Delta R_{\text{NiSi}}$ ) change curve.

Fig. 4. With various doses of dopant segregation process for NiSi/n-Si SJDs. (a) I-V characteristic curve. (b)  $\phi_{Bn,eff}$  and *n* as a function of implantation dose.

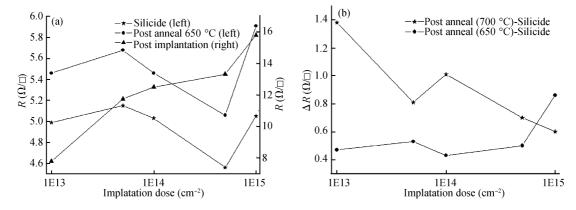

Fig. 5. With various doses of dopant segregation process for NiSi/n-Si SJDs. (a)  $R_{\text{NiSi}}$  and (b)  $\Delta R_{\text{NiSi}}$  as a function of implantation dose.

and to deform the energy band upward leading to an increased  $\phi_{Bn,eff}^{[4,9-11]}$ . So, the reverse current decreases with increasing  $\phi_{Bn,eff}$ . Because the decrement of the reverse current with increasing implantation dose is obvious, changing the implantation dose is more efficient in tuning  $\phi_{Bn,eff}$  when other dopant segregation process parameters remain invariant.

In Fig. 5(a),  $R_{\text{NiSi}}$  after implantation is increased with increasing implantation dose. Ion implantation damage is an inevitable result of the ion implantation process, which is increased with increasing implantation dose. The ion implanta-

tion damage enhances the electron scattering, resulting in increasing resistance. Although segregation annealing can repair part of the implantation damage, because the impurity and the implantation damage are introduced into NiSi films,  $\Delta R_{\text{NiSi}}$  still exists between the pre- and post-segregation processes<sup>[13]</sup>.

In Fig. 5(b), when the segregation annealing is 650 °C 30 s,  $\Delta R_{\text{NiSi}}$  between pre-implantation and the post-segregation process is increased with increasing implantation dose. However, when the segregation annealing is 700 °C 30 s,  $\Delta R_{\text{NiSi}}$  is decreased with increasing implantation dose. In addition, when

Fig. 6. With various segregation annealing temperatures of dopant segregation process for NiSi/n-Si SJDs with a fixed BF<sub>2</sub> dose of  $1 \times 10^{15}$  cm<sup>-2</sup>. (a) *I*–*V* characteristic curve. (b)  $\phi_{\text{Bn,eff}}$  and *n* as a function of annealing temperature.

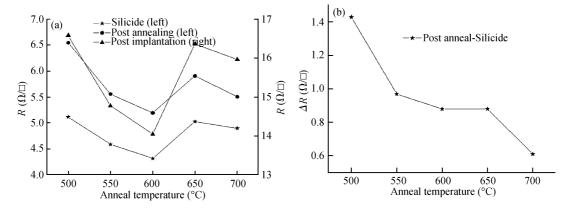

Fig. 7. With various segregation annealing temperatures of dopant segregation process for NiSi/n-Si SJDs. (a)  $R_{NiSi}$  and (b)  $\Delta R_{NiSi}$  as a function of annealing temperature.

the implantation dose is less than  $1 \times 10^{15}$  cm<sup>-2</sup>,  $\Delta R_{\text{NiSi}}$  after 700 °C 30 s segregation annealing is obviously higher than that after 650 °C 30 s segregation annealing. Comparing Fig. 3(b) with Fig. 5(b) and combining with the value of n in Fig. 4(b), we draw some conclusions as below: One is that B implantation can improve the thermal stability of NiSi films, and this is increased by increasing the implantation dose<sup>[13]</sup>. So  $\Delta R_{\text{NiSi}}$ after 700 °C 30 s segregation annealing is decreased with increasing implantation dose, and it is obviously lower than that after 700 °C 30 s segregation annealing without B implantation. Another is that, after 650 °C 30 s segregation annealing, the interface characteristic of NiSi/n-Si is good and the NiSi film is stable. So *n* stays at 1 and  $\Delta R_{\text{NiSi}}$  stays at the same value when the implantation dose is less than  $1 \times 10^{15}$  cm<sup>-2</sup>. When the implantation dose reaches  $1 \times 10^{15}$  cm<sup>-2</sup>, even after 650 °C 30 s segregation annealing, there is still much implantation damage in the NiSi film, which results in increasing  $R_{\text{NiSi}}$ . The other is that there must be a high resistance state Ni-silicide phase formation after 700 °C 30 s segregation annealing<sup>[5]</sup>, and high temperature annealing can enhance the repair of implantation damage. So, when the implantation dose is less than  $1 \times 10^{15}$  cm<sup>-2</sup>,  $\Delta R_{\text{NiSi}}$  after 700 °C 30 s segregation annealing is obviously higher than that after 650 °C 30 s segregation annealing. When the implantation dose reaches  $1 \times 10^{15}$  cm<sup>-2</sup>,  $\Delta R_{\rm NiSi}$  after the segregation process with 700°C 30 s segregation annealing is lower than that after the segregation process

with 650 °C 30 s segregation annealing.

Another group of wafers was treated with a dose of  $1 \times 10^{15}$  cm<sup>-2</sup> BF<sub>2</sub> ion implantation at the same implantation energy and various segregation annealing temperatures (500–700 °C) for 30 s. Figure 6 shows that the reverse current is decreased and  $\phi_{Bn,eff}$  is increased with increasing segregation annealing temperature from 500 to 650 °C, and *n* is about 1. The main reason for this phenomenon is that the concentration of B at the NiSi/n-Si interface increases as the temperature rises<sup>[10, 14, 15]</sup>, which then induces increasing  $\phi_{Bn,eff}$  <sup>[3, 4, 10, 11, 13]</sup> and decreasing reverse current. Because the decrement of the reverse current with increasing segregation annealing temperature is tiny, changing the segregation annealing temperature only can finely adjust  $\phi_{Bn,eff}$  when other dopant segregation process parameters remain invariant.

For the wafer after 700 °C 30 s segregation annealing, the previous research told us that there is high resistance state Nisilicide phase formation at the NiSi/n-Si interface, which results in an abnormal increase of the reverse current and slightly larger n.

In Fig. 7(b),  $\Delta R_{\text{NiSi}}$  decreases with increasing segregation annealing temperature. This phenomenon further illustrates that, even after segregation annealing, there is still much implantation damage in the NiSi film, and high temperature annealing can enhance the repair of implantation damage.

The last group of wafers was treated with a dose of  $1 \times 10^{15}$

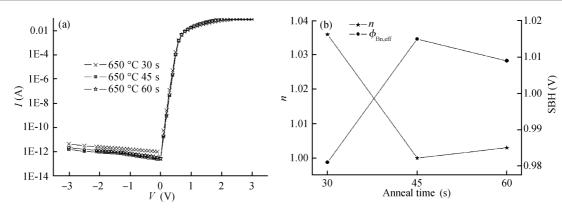

Fig. 8. With various segregation annealing times of dopant segregation process for NiSi/n-Si SJDs. (a) I-V characteristic curve. (b)  $\phi_{Bn,eff}$  and n as a function of annealing time.

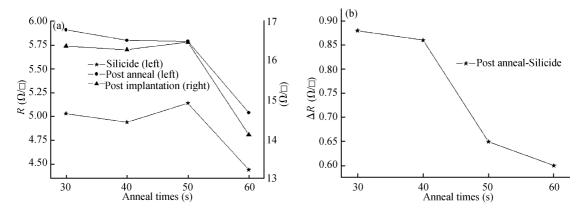

Fig. 9. With various segregation annealing times of dopant segregation process for NiSi/n-Si SJDs. (a)  $R_{\text{NiSi}}$  and (b)  $\Delta R_{\text{NiSi}}$  as a function of annealing time.

cm<sup>-2</sup> BF<sub>2</sub> ion implantation at the same implantation energy and the same segregation annealing temperature of 650 °C for various times from 30 to 60 s. Figures 8 and 9 show that the changes of segregation annealing time have a small effect on the electrical characteristics of NiSi/n-Si SJDs, but can obviously decrease  $R_{\text{NiSi}}$ . Therefore, by optimization of segregation annealing time, the resistance characteristic of NiSi films can be improved.

## 5. Summary

In this paper, the effects of different dopant segregation process parameters, including impurity implantation dose, segregation annealing temperature and segregation annealing time, on the  $\phi_{B,eff}$  of NiSi/n-Si SJDs and the resistance characteristic of NiSi films have been studied. According to the results, we draw some conclusions as below. One is that the implantation dose plays a major role in tuning  $\phi_{Bn,eff}$  and the adjustment range increases with increasing implantation dose when the segregation annealing temperature is above 500 °C, but a high implantation dose will cause high  $R_{\text{NiSi}}$ . Another is that the segregation annealing temperature only can finely adjust  $\phi_{Bn,eff}$  when other dopant segregation process parameters remain invariant. The last is that the segregation annealing time has little effect on the electrical characteristics of NiSi/n-Si SJDs, but can obviously optimize the resistance characteristic of NiSi films. So, the optimum process conditions of the dopant segregation process for NiSi/n-Si SJDs are  $1 \times 10^{15}$  cm<sup>-2</sup> of BF<sub>2</sub> ion implantation and 650 °C, 60 s of segregation annealing.

### References

- Swirhun S E, Sangiorgi E, Weeks A J, et al. A VLSI-suitable Schottky-barrier CMOS process. EEE Trans Electron Devices, 1985, 32(2): 194

- [2] Chen B S, Chen M C. Formation of cobalt silicided shallow junction using implant into/through silicide technology and low temperature furnace annealing. IEEE Trans Electron Devices, 1996, 43(2): 258

- [3] Sze S M, Ng K K. Physics of semiconductor devices. 3rd ed. Wiley, 2007

- [4] Zhang Zhen, Qiu Zhijun, Liu Ran, et al. Schottky-barrier height tuning by means of ion implantation into preformed silicide films followed by drive-in anneal. IEEE Electron Device Lett, 2007, 28(7): 565

- [5] Nagahiro K, Tsutsui K, Shiozawa T, et al. Thermal stability of NiSi controlled by post silicidation metal doping method. 8th International Conference on Solid-State and Integrated Circuit Technology, 2006: 466

- [6] Huang Yifei, Jiang Yulong, Ru Guoping, et al. Electrical properties study of Ni (Pt)-silicide/Si contacts. 8th International Conference on Solid-State and Integrated Circuit Technology, Oct 2006: 475

- [7] Oh S Y, Lee H D, Wang J S. Influence of the annealing ambient on the thermal stability of Ni silicide for nano-scale CMOSFETs.

International Workshop on Junction Technology, May 2006: 196

- [8] Zhao Q T, Zhang M, Knoch J, et al. Tuning of Schottky barrier heights by silicidation induced impurity segregation. International Workshop on Junction Technology, May 2006: 147

- [9] Yamauchi T, Nishi Y, Tsuchiya Y, et al. Novel doping technology for a 1 nm NiSi/Si junction with dipoles comforting Schottky (DCS) barrier. IEEE International Electron Devices Meeting, Dec 2007: 963

- [10] Qiu Z, Zhang Z, Ostling M, et al. A comparative study of two different schemes to dopant segregation at NiSi/Si and PtSi/Si interfaces for Schottky barrier height lowering. IEEE Trans Electron Devices, 2008, 55(1): 396

- [11] Shenai K, Sangiorgi E, Saraswat K C, et al. Accurate barrier modeling of metal and silicide contacts. IEEE Electron Device Lett, 1984, 5(5): 145

- [12] Zhang M, Knoch J, Zhao Q T, et al. Schottky barrier height modulation using dopant segregation in Schottky-barrier SOI-MOSFETs. Proceedings of 35th European Solid-State Device Re-

search Conference, 2005: 457

- [13] Ru G P, Jiang Y L, Qu X P, et al. Annealing process influence and dopant-silicide interaction in self-aligned NiSi technology. Proceedings 7th International Conference on Solid-State and Integrated Circuits Technology, Oct 2004, 1: 451

- [14] Larrieu G, Dubois E, Valentin R, et al. Low temperature implementation of dopant-segregated band-edge metallic S/D junctions in thin-body SOI p-MOSFETs. IEEE International Electron Devices Meeting, 2007: 147

- [15] Zhang Z, Qiu Z, Hellstrom P E, et al. SB-MOSFETs in UTB-SOI featuring PtSi source/drain with dopant segregation. IEEE Electron Device Lett, 2008, 29(1): 125

- [16] Shang Haiping, Xu Qiuxia. Two-step Ni silicide process and influence of protective N<sub>2</sub> gas. Journal of Semiconductors, 2009, 30(9): 096002

- [17] Shang Haiping, Xu Qiuxia. Adjustment of NiSi/n-Si SBH by post-silicide of dopant segregation process. Journal of Semiconductors, 2009, 30(10): 106001