# Simulation of a Monolithic Integrated CMOS Preamplifier for Neural Recordings \*

Sui Xiaohong, Liu Jinbin, Gu Ming, Pei Weihua, and Chen Hongda

(State Key Laboratory of Integrated Optoelectronics, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China)

**Abstract:** A monolithic integrated CMOS preamplifier is presented for neural recording applications. Two AC-coupled capacitors are used to eliminate the large and random DC offsets existing in the electrode-electrolyte interface. Diode-connected nMOS transistors with a negative voltage between the gate and source are candidates for the large resistors necessary for the preamplifier. A novel analysis is given to determine the noise power spectral density. Simulation results show that the two-stage CMOS preamplifier in a closed-loop capacitive feedback configuration provides an AC imband gain of 38. 8dB, a DC gain of 0, and an input-referred noise of 277 nV<sub>rms</sub> integrated from 0. 1 Hz to 1kHz. The preamplifier can eliminate the DC offset voltage and has low input-referred noise by novel circuit configuration and theoretical analysis.

**Key words:** preamplifier; DC offset; input-referred noise **PACC:** 2960C; 8700 **EEACC:** 1220; 1130; 7510D

#### 1 Introduction

There is a growing interest in developing an effective communication interface connecting the human brain with a computer, a brain-computer interface [1-3] (BCI), where a preamplifier is used to sample the brain 's neural signals. The design of such a preamplifier is complicated because of the electrode DC offset voltages resulting from the DC polarization of the electrode immersed in electrolyte:DC input voltages up to 100mV should not result in the saturation of the preamplifier [4.5]. In addition, to realize low equivalent input noise, monolithic integration, and small preamplifier dimensions, some characteristics are important to obtain a practical design: no severe demands should be put

on resistors, nor should any capacitors larger than 100nF be contained.

Some fully integrated CMOS neural recording preamplifiers<sup>[6]</sup> use diode-capacitor feedback to filter the electrode DC offset voltages. These preamplifiers are operated in open loop ,which makes the gain and output offset voltage difficult to control. Another approach commonly used to filter the electrode DC offset voltages involves loading the recording site with a high-resistance, reverse-biased diode so that this resistor and site capacitor form a high pass filter. The reverse-biased diodes suffer from optical sensitivity problems saturating the outputs of the preamplifiers ,and the input-referred noise is on the order of several  $\mu V_{rms}$  integrated from 0. 1 Hz to 1kHz.

In view of these disadvantages of the present

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (Nos. 2003AA302240, 2003AA312040) and the National Natural Science Foundation of China (No. 60536030)

Sui Xiaohong female, was born in 1980, PhD candidate. Her present research interest is in integrated circuits and systems in relation to braincomputer interfacing, such as fabrication of microelectrodes and design of neural recording specific preamplifiers.

preamplifiers, a monolithic integrated CMOS preamplifier is described in this paper. There are no resistors in this circuit, and its capacitors are on the order of pF. As a result, this preamplifier can be realized on a single die chip. The capacitive feedback configuration makes the gain of this preamplifier independent of process variations. Two AC-coupled capacitors are in combination with the large equivalent input resistor to suppress the DC offset of hundreds of mV at the electrode-electrolyte interface, while at the same time forming a high-pass filter.

# 2 Circuit architecture of the preamplifier

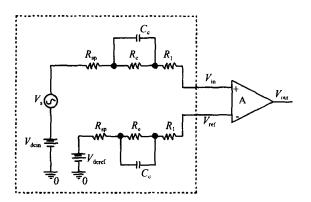

Microelectrodes are implanted in the brain cortex to extract neural signals much accurately. An electrical model of the electrode-electrolyte interface is shown in Fig. 1.  $V_{\rm in}$  and  $V_{\rm ref}$  represent the input and reference voltage signals of the preamplifier. Usually the reference microelectrode is attached to the electrically stable brain electrolyte, and the input microelectrode is implanted among some neurons in the brain cortex. The components in the dashed box represent the equivalent microelectrode input circuit<sup>[7]</sup>. The DC voltages  $V_{\text{dcin}}$  and  $V_{\text{dcref}}$  represent the DC offsets at the electrode-electrolyte interface. The signal source  $V_s$  is the requisite brain neural signal.  $R_{sp}$  (spreading resistor in saline) models the signal loss due to the distance between the microelectrode and the cell. Ce models the capacitor of the microelectrode-electrolyte interface. Re (leakage resistor) accounts for the charge carriers realistically crossing the double-layer.  $R_1$  represents the microelectrode resistor.

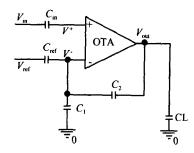

The circuit schematic of the preamplifier is shown in Fig. 2. Capacitors  $C_{\rm in}$  of 5pF and  $C_{\rm ref}$  of 100fF are used to reject the DC offsets  $V_{\rm dcin}$  and  $V_{\rm dcref}$ , respectively. Capacitors  $C_1$  and  $C_2$  configure the capacitive negative feedback loop. The in-band gain of the closed-loop preamplifier can be described as  $1 + C_1/C_2 - C_1/C_2$  ( $C_1 \gg C_2$ ,  $C_{\rm ref} \ll C_1$ ).

Fig. 1 Electrical model of electrode-electrolyte interface

With C<sub>1</sub> of 10pF and C<sub>2</sub> of 100fF, the AC in-band gain can almost reach 40dB.

Fig. 2 Circuit schematic of the capacitive-feedback preamplifier

## 3 OTA design methodology

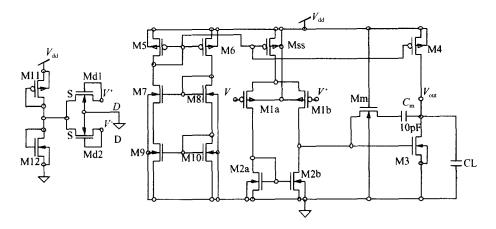

The preamplifier is composed of an OTA (operational conductance amplifier) and capacitors  $C_{\rm in}$ ,  $C_{\rm ref}$ ,  $C_{\rm l}$ , and  $C_{\rm 2}$  as seen in Fig. 2. The transistor-level schematic of this OTA is displayed in Fig. 3.  $V_{\rm dd}$  is the power supply source of 5V, while  $V^{-}$  and  $V^{+}$  are the negative and positive input ports of the OTA. The Miller capacitor  $C_{\rm m}$  and MOS transistor Mm operating in the linear region are for frequency compensation.

As the preamplifier uses a capacitive-coupled input structure and capacitive-feedback configuration, the OTA must have its own DC bias circuit as shown in the left circuit of Fig. 3. Diode-connected transistors M11 and M12 are in tandem to produce a DC voltage. It is clear in Fig. 1 that a large equivalent resistance exists at the electrode-electrolyte

Fig. 3 Transistor-level schematic of the OTA in preamplifier

interface, so a larger equivalent input resistance of the OTA is necessary to obtain the neural signals with a large enough amplitude. In this design, diode-connected transistors Md1 and Md2 with a negative voltage between the gate and source can realize a large resistance of over  $10^{11}$  with no effect on the inherent large resistance of the MOS input structure, and DC bias voltages  $V^+$  and  $V^-$  are generated at the same time.

Taking into account the weakness of the neural signals of  $50 \sim 500 \mu V$ , low noise is an essential requirement of this preamplifier and the OTA. The noise in this OTA comes from flicker noise and thermal noise existing in the MOS transistors [8~11]. Since frequencies of brain cortex neural potentials ranges from less than 1 Hz to several kHz, flicker noise is the primary noise source. The voltage of the flicker noise is shown in Eq. (1).

$$V^2 = \frac{K}{C_{\text{ox}}WL} \times \frac{1}{f}$$

(1)

where K is a process-dependent constant on the order of  $10^{-25} \, \text{V}^2 \, \cdot \text{F}$ , W and L denote the transistor width and length,  $C_{\text{ox}}$  is the transistor capacitance density, and f represents the operation frequency. From this equation, it is clear that increasing the product of W and L results in the decrease of noise voltage at the expense of the increased chip area. This causes a serious problem in our application because the input of the system or the equivalent impedance of electrode-electrolyte interface has a high level, and because the active neural probe usu-

ally contains multiple recording sites so that one preamplifier is required for each recording site. In this regard, it is very important to minimize the areas of devices at the input stage while meeting the specification of the noise characteristics required for the following system.

Since the input-referred noise of the cascadestage amplifier is dominated by that of the first amplification stage, the noise characteristics of the input stage in this OTA are emphasized and theoretically analyzed in detail in this paper. The inputstage thermal noise spectral density  $N_{\rm th}$  is

$$N_{\rm th} = \frac{16}{3} \times \frac{kT}{g_{\rm M1a}} (1 + \frac{g_{\rm M2a}}{g_{\rm M1a}})$$

(2)

where  $k = 1.38 \times 10^{-23} \,\mathrm{J/K}$  is the Boltzman constant. The flicker noise spectral density  $N_{1/f}$  is given by Eq. (3). The total noise power spectral density of the MOS transistors  $N_{\rm mos}$  is given by Eq. (4).

$$N_{1/f} = \frac{2}{C_{\text{ox}}} \times \frac{1}{f} \left( \frac{K_{\text{p}}}{W_{\text{M1a}} L_{\text{M1a}}} + \frac{K_{\text{n}}}{W_{\text{M2a}} L_{\text{M2a}}} \left( \frac{g_{\text{M2a}}}{g_{\text{M1a}}} \right)^{2} \right)$$

(3)

$$N_{\text{mos}} = N_{\text{th}} + N_{1/f} = \frac{16}{3} \times \frac{kT}{g_{\text{M1a}}} (1 + \frac{g_{\text{M2a}}}{g_{\text{M1a}}}) + \frac{2}{C_{\text{ox}}} \times \frac{1}{f} (\frac{K_{\text{p}}}{W_{\text{M1a}} L_{\text{M1a}}} + \frac{K_{\text{n}}}{W_{\text{M2a}} L_{\text{M2a}}} (\frac{g_{\text{M2a}}}{g_{\text{M1a}}})^{2})$$

(4)

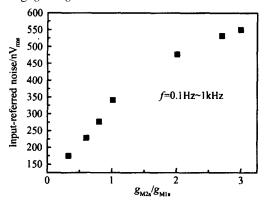

According to Eq. (4), increasing the transconductance  $g_{\rm M1a}$  and the device area will simultaneously decrease  $N_{\rm th}$  and  $N_{1/f}$ , then  $N_{\rm mos}$ . Another interesting phenomenon in this equation is that  $N_{\rm mos}$  is basically proportional to the ratio of  $g_{\rm M2a}$  and

$g_{\rm M1a}$ . Accordingly, reducing  $g_{\rm M2a}/g_{\rm M1a}$  leads to decrease of  $N_{\rm mos}$ . Figure 4 plots the curve of the input-referred noise versus  $g_{\rm M2a}/g_{\rm M1a}$  with frequency integrated from 0.1 Hz to 1 kHz. As shown in Fig. 4, the input-referred noise increases with increasing  $g_{\rm M2a}/g_{\rm M1a}$ .

Fig. 4 Input-referred noise versus  $g_{M2a}/g_{M1a}$

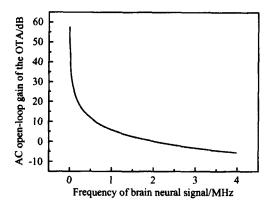

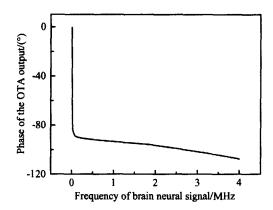

Transistor Mm and capacitor  $C_m$  compose the lead compensation configuration, and the amplitude and phase of the OTA output as functions of frequency are plotted in Figs. 5 and 6, respectively. From these curves, a satisfied phase margin of 83° is obtained.

In accordance with the above description, device parameters of this OTA are determined, and

Fig. 5 AC open-loop gain of the OTA versus frequency

Fig. 6 OTA output phase versus frequency

the ultimate device dimensions in this OTA determined by optimization design are listed in Table 1.

Table 1 Device dimensions of MOS transistors

| MOS transistor | Mss  | M1a   | M1b   | M2a  | M2b  | M3    | M4    | M5   | M6   | M7   | M8   | M9   | M10  | M11 | M12  | Md1 | Md2 | Mm  |

|----------------|------|-------|-------|------|------|-------|-------|------|------|------|------|------|------|-----|------|-----|-----|-----|

| W/ L (µm/ µm)  | 20/4 | 300/4 | 300/4 | 56/4 | 56/4 | 600/4 | 100/4 | 20/4 | 20/4 | 20/4 | 20/4 | 20/4 | 20/4 | 4/4 | 10/4 | 4/4 | 4/4 | 4/4 |

## 4 Simulation results of the preamplifier

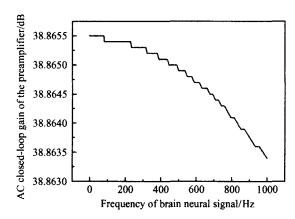

The whole circuit schematic of the preamplifier is the combination of Figs. 2 and 3. This preamplifier is simulated by the HSPICE simulator with model parameters from CSMC-HJ 0. 6 $\mu$ m CMOS double-metal-double-poly process technology, and the capacitors will be fabricated using double poly. With the MOS transistor dimensions listed in Table 1,  $C_1$  of 10pF and  $C_2$  of 100fF, simulation re-

sults show that the AC in-band gain of the preamplifier is 38.8 dB with frequency from 0.1 Hz to 1 kHz as shown in Fig. 7. Considering the signal loss due to capacitor  $G_{in}$ , the AC in-band gain of 38.8 dB is a little smaller than the theoretical value of 40 dB.

#### 5 Conclusion

A novel monolithic integrated CMOS preamplifier is presented in this paper. Two AC-coupled capacitors are used to eliminate the DC offset volt-

Fig. 7 AC imband gain of the preamplifier with frequency from 0. 1 Hz to 1k Hz

age in the electrode-electrolyte interface. A capacitive negative feedback circuit configuration achieves an adjustable AC in-band gain ,and its expression is also provided. A novel analysis is given to determine the noise power spectral density. Theoretical analysis shows that the noise power spectral density of the OTA used in the preamplifier is proportional to  $g_{\rm M2a}/g_{\rm M1a}$ , and this theory is verified by simulation results. The simulation results also show that the two-stage CMOS preamplifier in a closed-loop capacitive feedback configuration provides an AC in-band gain of 38. 8dB ,a DC gain of 0 ,and an input-referred noise of 277nV<sub>rms</sub> integrated from 0. 1 Hz to 1k Hz.

#### References

[1] Wolpaw J R ,Birbaumer N ,McFarland D J ,et al. Brain-computer interfaces for communication and control. Clin Neurophysiol ,2002 ,113:767

- [2] Wolpaw J R, McFarland D J, Vaughan T M. The wadsworth center brain-computer interface (BCI) research and development program. IEEE Trans Neural Systems and Rehabilitation Engineering, 2003, 11(2):204

- [ 3 ] Blankertz B, M üler K R, Curio G, et al. The BCI competition 2003:progress and perspectives in detection and discrimination of EEG single trials. IEEE Trans Biomedical Engineering, 2004, 51(6):1044

- [4] Sui Xiaohong, Pei Weihua, Chen Hongda, et al. Circuit design and simulation of a CMOS-based preamplifier for brain neural signals. First International Conference on Neural Interface and Control, 2005:108

- [5] Mohseni P, Najafi K. A fully integrated neural recording amplifier with DC input stabilization. IEEE Trans Biomedical Engineering, 2004, 51(5):832

- [6] Ji J, Wise K D. An implantable CMOS circuit interface for multiplexed microelectrode recording arrays. IEEE J Solid State Circuits, 1992, 27:433

- [7] Martinoia S, Massobrio P, Bove M, et al. Cultured neurons coupled to microelectrode arrays: circuit models, simulations and experimental data. IEEE Trans Biomedical Engineering, 2004,51(5):859

- [8] Kim K H, Kim S J. Noise performance design of CMOS preamplifier for the active semiconductor neural probe. IEEE Trans Biomedical Engineering, 2000, 47(8):1097

- [ 9 ] Harrison R R, Charles C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J Solid-State Circuits, 2003, 38 (6):958

- [10] Yao Fei, Cheng Buwen. Design of 1 GHz 0.5 \mu m CMOS low noise amplifier. Chinese Journal of Semiconductors, 2004,25(10):1291(in Chinese)[姚飞,成步文.1 GHz 0.5 \mu m CMOS 低噪声放大器的设计. 半导体学报,2004,25(10): 1291]

- [11] Huang Yumei, Hong Zhiliang. Design and test of a CMOS low noise amplifier in bluetooth transceiver. Chinese Journal of Semiconductors, 2004, 25(6):633(in Chinese)[黄煜梅,洪志良. 蓝牙收发器中的 CMOS 低噪声放大器的设计与测试. 半导体学报, 2004, 25(6):633]

### 提取神经电信号的单片集成 CMOS 前置放大器的仿真研究\*

#### 隋晓红 刘金彬 顾 明 裴为华 陈弘达

(中国科学院半导体研究所 集成光电子学国家重点联合实验室, 北京 100083)

摘要:提出一种用于提取神经电信号的新型单片集成 CMOS 前置放大器.在放大器输入端引入的交流耦合电容可以消除存在于电极-电解液之间的电极极化电压,栅源电压为负值的二极管连接的 nMOS 晶体管能够作为大电阻,并且占用很小芯片面积,可以通过此大电阻为前置放大器提供直流偏置,同时不影响输入阻抗值.通过对输入级进行理论噪声分析,确定了放大器中的各个器件参数.仿真结果表明,由于采用电容负反馈结构,此放大器的交流增益为38.8dB,无直流增益,在0.1 Hz~1k Hz 频率范围内,总输入等效噪声为277nVms.

**关键词**: 前置放大器; 电极极化电压; 等效输入噪声 **PACC**: 2960C; 8700 **EEACC**: 1220; 1130; 7510D

中图分类号: TN4 文献标识码: A 文章编号: 0253-4177(2005)12-2275-06

<sup>\*</sup>国家高技术研究发展计划(批准号:2003AA302240,2003AA312040)和国家自然科学基金(批准号:60536030)资助项目

隋晓红 女,1980年出生,博士研究生,研究方向是与脑机接口方面相关的集成电路与系统,主要包括提取神经电信号的微电极制作,以及神经电信号专用的前置放大器设计.