学

报

# A 2. 5Gb/s GaAs MESFET Clock Recovery and Decision Circuit\*

ZHAN Yan, XIA Guan-qun, WANG Yong-sheng, ZHAO Jian-long and ZHU Chao-song

(Shanghai Institute of Metallurgy, The Chinese Academy of Sciences, Shanghai 200050, China)

Abstract: A 2.5Gb/s depletion-mode GaAs MESFET clock recovery and decision circuit is described, which applies to the optical fiber communication. The circuit consists of a clock recovery circuit, including a preprocessor, phase detector (PD), low-pass filter (LPF) and voltage controlled oscillator (VCO) and a decision circuit, including a comparator and a latch. The SPICE simulation result confirms the high frequency 2.5GHz of the clock recovery and the high speed 2.5Gb/s of the decision circuit. The 2.5Gb/s decision circuit has proved to be able to deal with the input signal and produce a digital output signal after it being sampled by a clock signal.

Key words: GaAs; MESFET; clock recovery; decision

EEACC: 1265Z; 6260C

#### 1 Introduction

GaAs integrated circuits have some distinct advantages such as high speed, low power dissipation, wide operation temperature and high radiation hardness. And GaAs applies to the optical fiber communication, satellite communication, mobile communication, high speed test systems, etc<sup>[1]</sup>. Optical fiber communication, a new communication technique, is promising in acting as the core of B-ISDN (broad integrated services network)<sup>[2]</sup>, due to its broadband, large capacity, far transmitting distance, lightness antijamming and saving energy. The clock recovery and decision circuit plays an important role in the receiver of the communication system, which comprises a clock recovery circuit and a decision circuit. Some overseas papers have been found to report the clock recovery circuit<sup>[3-6]</sup> and the decision circuit<sup>[7,8]</sup>, but not including the clock recovery circuit or the decision circuit, while few domestic papers reported can be

found on the clock recovery circuit and the decision circuit.

We have designed a 2.5Gb/s depletion mode GaAs MESFET clock recovery and decision circuit. Proved by SPICE simulation, the clock recovery circuit can get a 2.5GHz clock signal from the input signal, while the decision circuit can get a 2.5Gb/s digital output signal after it being sampled by a clock signal after low or high level recognition. The test result shows that the decision circuit operates properly at the speed of 2.5Gb/s.

### 2 Circuit Design and Simulation

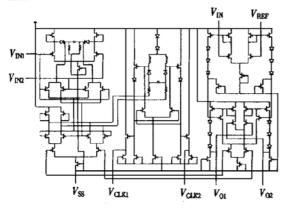

The clock recovery and decision circuit is shown in Fig. 1, which consists of a clock recovery circuit and a decision circuit. The former includes a preprocessor, phase detector (PD), low-pass filter (LPF) and voltage controlled oscillator (VCO), while the latter includes a comparator and a latch. The power supply Vss is -5.2V. A pair of double frequency signals is produced by using the prepro-

<sup>\*</sup> Project Supported by National Natural Science Foundation of China Under Grant No. 69676003 and National Ninth-Five Research Program.

ZHAN Yan born in 1974, PhD candidate. Her research interests include GaAs devices and circuits.

cessor after the pair of antiphase input signals, VINI and V<sub>IN2</sub>, has been pretreated. By using PD, the phase of the signal is compared with that of the VCO output signals before discrepancy is generated in signals due to the difference between these two phases. The signals having been filtered out of the high-frequency part by the LPF makes the output frequency of the VCO close to that of the pretreated signals. When the two frequencies are same, the phase difference will be stable and the VCO be latchdown, and then a pair of antiphase recovery clock signals,  $V_{\text{CLK1}}$  and  $V_{\text{CLK2}}$  are exported.  $V_{\text{IN}}$  is an input signal ( $V_{\text{IN1}}$  or  $V_{\text{IN2}}$ ).  $V_{\text{REF}}$  is the reference voltage. Whether the output of the comparator is low or high can be determined after V<sub>IN</sub> is compared with VREF. Sampled by recovery clock, the latch can generate the output of the whole circuit  $V_{01}$  and  $V_{02}$ .

FIG. 1 Schematic Clock Recovery and Decision Circuit

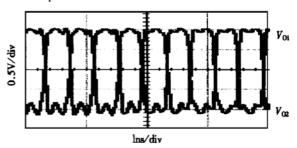

The clock recovery and decision circuit is simulated and optimized by SPICE. The power supply  $V_{SS}$  is -5.2V. Input  $V_{INI}(-3V--5V)$  and  $V_{IN2}(-5V--3V)$  are a pair of antiphase pulse signals. 2. 5GHz clock signals can be obtained from the input signals in the clock recovery part. Let  $V_{IN}$  of the decision part be  $V_{INI}$ .  $V_{REF}$  is -4V. When  $V_{CLKI}$  is low and  $V_{CLK2}$  is high, the latch is locked and  $V_{OI}$  and  $V_{O2}$  keep the original states. On the contrary, the latch can read the signals from the comparator. If  $V_{IN}$  is low,  $V_{OI}$  will be low and  $V_{O2}$  be high. Figure 2 shows the simulated transient curves

of the clock recovery and decision circuit at the transfer speed of 2.5Gbit/s.

FIG. 2 Simulative Transient Curves of Clock Recovery and Decision Circuit

### 3 Results and Discussion

Because of the restrictive condition, only the decision circuit can be fabricated by using lithography in seven steps. The process flow includes the semi-insulating GaAs substrate subdamage layer etch, direct double Si ion implantation, anneal at 900°C, mark etch, B ion isolation implantation, AuGeNi/Au ohmic metal deposition and anneal at 450°C, Ti/Pt/Au Schottky gate metal deposition, twice Cr/Au routing metal deposition, and polyimide isolation.

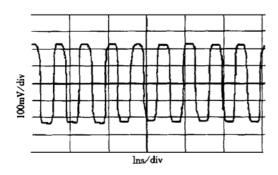

The corresponding testing board is also designed and fabricated. The chip pasted on the board with silver conduct-glue is connected with the board by aurum filament in the testing box. Tested with HP oscillogragh, the decision circuit shows the ability to deal with the input signal and produce the digital output signal when it has been sampled by a clock signal. The transfer speed of the circuit is 2.5Gbit/s. The circuit exports a pair of antiphase signals. Figure 3 shows one of the outputs Vol waveforms in the test.

#### 4 Conclusion

The clock recovery and decision circuit designed is confirmed by the SPICE simulation result. The clock recovery circuit can get a 2.5GHz clock signal from the input signal while the decision circuit can get a 2.5Gb/s digital output signal

946 半 导 体 学 报 22 卷

FIG. 3 Vol Waveforms Tested

sampled by clock signal after low or high level recognition. The test result shows that the decision circuit operates properly at the speed of 2.5Gb/s.

Acknowledgment The authors wish to thank Prof. Song Macheng of the 13th Institute of Information and Industry Ministry for the helpful discussion and suggestions.

#### References

- Shi Chang-xin, High-Speed GaAs IC, Shanghai: Shanghai JiaoTong University Publishers, 1991: 1—5.

- [2] Wang Tin-yao, Basic Optical Communication Equipment, Tianjin: Tianjin Science and technology Publishers, 1992: 1— 104.

- [ 3 ] Behzad Razavi, IEEE J. Solid-State Circuits, 1996, 31(4): 472—480.

- [4] Sal Nati, IEEE J. Solid-State Circuits, 1997, 32(9):1350— 1356.

- [5] M. Rau, IEEE J. Solid-State Circuits, 1997, 32(7):1156— 1159.

- [6] Vincent von Kaenel, IEEE J. Solid-State Circuits, 1996, 31 (11): 1715—1722.

- [7] Omar Wing, Gallium Arsenide Digital Circuits, Massachusetts: Kluwer Academic Publishers, 1990: 135—147.

- [8] Koichi Murata, IEEE J. Solid-State Circuits, 1995, 30 (10): 1101-1108.

## 2. 5Gb/s GaAs MESFET 定时判决电路\*

### 詹 琰 夏冠群 王永生 赵建龙 朱朝嵩

(中国科学院上海冶金研究所,上海 200050)

摘要: 设计了 2.5Gb/s 光纤通信用耗尽型 GaAs MESFET 定时判决电路. 通过 SPICE 模拟表明恢复的时钟频率达 2.5GHz,判决电路传输速率达 2.5Gb/s. 实验证明经时钟信号抽样后判决电路可产生正确的数字信号,传输速率达 2.5Gb/s.

关键词: GaAs; MESFET; 时钟恢复; 判决

EEACC: 1265Z; 6260C

中图分类号: TN43 文献标识码: A 文章编号: 0253-4177(2001)07-0944-03

<sup>\* 51.</sup>五"科技攻关和国家自然科学基金(批准号: 69676003) 资助项目. 詹 琰 1974年出生,博士研究生,从事 GaAs 器件与电路研究. 2000-09-03 收到, 2000-11-19 定稿