# Unified MOSFET Short Channel Factor Using Variational Method\*

CHEN Wen-song(陈文松), TIAN Li-lin(田立林) and LI Zhi-jian(李志坚)

(Institute of Microelectrics, Tsinghua University, Beijing 100084, China)

Abstract: A new natural gate length scale for MOSFET's is presented using Variational Method. Comparison of the short channel effects is conducted for the uniform channel doping bulk MOSFET, intrinsic channel doping bulk MOSFET, SOI MOSFET and double gated MOSFET. And the results are verified by the 2D numerical simulation. Taken all the 2-D effects on front gate dielectric, back gate dielectric and silicon film into account, the data validity of electrical equivalent oxide thickness is investigated by this model, as shows that it is valid only when the gate dielectric constant is relatively small.

Key words: Poisson's equation; variational method; deep submicron; MOSFET; short channel

effect

**EEACC**: 2530F; 2560B

CLC number: T N 386. 1 Document code: A Article ID: 0253-4177(2000) 05-0431-06

## 1 Introduction

It is well known that short channel effect is one of the most important constraints that determine the down scaling of MOSFET's. The relationship between the device structure configuration and short channel effect is first expressed empirically in Ref. [1]. And recently, due to its simplicity and physical insight, parabolic potential<sup>[2]</sup> and BOX<sup>[3]</sup> method are widely used<sup>[4-7]</sup> to analyze the short channel effect in the Deep Submicron MOSFET's. But they all neglect the two dimensional effects in the front and back gate dielectrics, which may be significant in thick high-permittivity insulators<sup>[8]</sup>. Another drawback in their deductions is that the source/drain boundary conditions are not fully satisfied<sup>[9]</sup>.

In the following section, a unified analytical model is established to simulate the short

<sup>\*</sup> Project Supported by National 9th Five-Year Plan on Science and Technology Program of China (Grant No. 97-760-

CHEN Wen-song (陈文松) was born in 1972. Currently he is a Ph. D candidate. His main research interests include MOSFET device physics, simulation and characterization.

channel effect in bulk and SOI MOSFET's using variational method first introduced in Ref. [10]. According to the method we applied, SOI and bulk MOSFET can be treated in the same analytical framework even when we considering the 2-D effect in the front and back gate (for SOI devices) dielectrics. So it is very suitable to do comparative study of 2-D effect in different MOS technologies, which is done in section 3. And the result is verified by 2-D numerical simulations. In section 4, the validity of electrical equivalent oxide thickness approximation is investigated with this model. The results show it lacks predictive accuracy when the gate dielectric constant is too large.

## 2 Derivation

The distinct feature of solving the Poisson's Equation with the Variation Method is

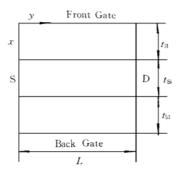

FIG. 1 Two Dimensional Area of a SOI MOSFET for Short Channel Effect Analysis

the ability to deal with the discontinuity of the dielectric constant at different material interface in the solution domain. Unlike the multi-zone approach we can consider the region constituted by different materials as one domain and solve it directly. For purpose of this derivation, the two-dimensional area for the potential analysis is approximated, as shown in Fig. 1, which includes front gate dielectric, fully depleted silicon film and back gate dielectric. For bulk and partial depleted SOI MOSFET, the silicon film and back gate dielectric parts are reduced to the channel depletion layer.

Using superposition, the potential distribution in this

area can be written as

$$\Phi(x, y) = \Phi(x) + \Delta \Phi(x, y)$$

where  $\Phi(x)$  is the 1-D, i. e., long-channel solution to Poisson's Equation satisfying the top and bottom boundary conditions; and  $\Delta \Phi(x,y)$  is the solution to Laplace's Equation, which accommodates the potential applied to the source and drain. Because  $\Delta \Phi(x,y)$  satisfies the Laplace's Equation, it must minimize the functional [12]

$$J[\Delta \Phi(x,y)] = \frac{1}{2} \int_{0}^{\infty} dy \int_{0}^{d} \epsilon(x) \left[ \left[ \frac{\partial \Delta \Phi(x,y)}{\partial x} \right]^{2} + \left[ \frac{\partial \Delta \Phi(x,y)}{\partial y} \right]^{2} \right] dx \tag{1}$$

where d is the sum of front gate dielectric thickness  $t_{\text{Bi}}$ , silicon film thickness  $t_{\text{Bi}}$  and the back gate dielectric thickness  $t_{\text{Bi}}(d = t_{\text{Bi}} + t_{\text{Bi}} + t_{\text{Bi}})$ , and  $\epsilon(x)$  is the permittivity function, which is defined as

$$\epsilon(x) = \begin{cases} \epsilon_{\text{I}} & \text{when } 0 \leq x < t_{\text{II}} \\ \epsilon_{\text{Si}} & t_{\text{II}} \leq x < t_{\text{II}} + t_{\text{Si}} \\ \epsilon_{\text{I}} & t_{\text{II}} + t_{\text{Si}} \leq x < d \end{cases}$$

where  $\epsilon$  is the front and back gate dielectric permittivity and  $\epsilon$ s is the silicon film dielectric permittivity. Though DIBL effect can be included in our deduction, for simplicity we

neglect the applied drain voltage. So the source and drain boundary conditions are the same. And we can meet the source/drain boundary condition simultaneously if we assume<sup>[10]</sup>

$$\Delta \Phi(x, y) = \Delta \Phi(x, 0) f(y) \tag{2}$$

and

$$f(0) = f(L) = 1$$

where

$$\Delta \Phi(x,0) = \Phi_{D}(x) - \Phi_{0}(x)$$

is the difference between the source/drain boundary condition  $\mathfrak{G}_{/D}(x)$  and 1-D solution  $\mathfrak{G}(x)$ . Substitute (2) into (1) and minimize it using Euler's condition (12), we get f(y) which satisfies following ordinary differential equation

$$l^{2} \frac{d^{2} f(y)}{dx^{2}} - f(y) = 0$$

(3)

where

$$l = \left[ \frac{\int_{0}^{d} \epsilon(x) \, \Delta \Phi_{\delta}(x, 0) \, \mathrm{d}x}{\int_{0}^{d} \epsilon(x) \left[ \frac{\mathrm{d}\Delta \Phi_{\delta}(x, 0)}{\mathrm{d}x} \right]^{2} \mathrm{d}x} \right]^{1/2}$$

(4)

(4) is the unified short channel factor for bulk and SOI MOSFET. From (3), we know l has the same physical meaning as the length scale used previously in Ref. [4, 5], i.e., the 2-D effect is small when l is small.

### 3 2-D Effect Comparison in Different MOS Structures

Due to its general validity, (4) can serve as a vehicle for different device structure to have a 2-D effect comparison. To get the value of l, only the source/drain boundary condition and 1-D solution are needed. So before further detailed numerical simulation we can get a concept of 2-D effect in new device structure, which is important in device design.

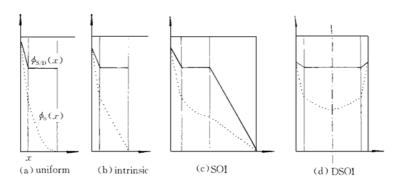

For an example, we compare the 2-D effect in the uniform doped-channel bulk MOSFET, intrinsic channel bulk MOSFET, SOI MOSFET and double-gated SOI MOSFET. Their schematic plot of 1-D solutions and source/drain boundary conditions are shown in Fig. 2. The boundary conditions at the dielectric edges are assumed to be linear [11] in this plot. To conduct a fair comparison, the thin silicon film of (c) is as thick as the depletion layer thickness of (a), (b). Due to the symmetry of the structure, two kinds of silicon film thickness for (d) are applied in this study, one (DSOI1) equals that of (c), and the other (DSOI2) is twice that of (c). The uniform channel doping concentration for (a) equals  $1 \times 10^{17} \text{cm}^{-3}$ , which determines the depletion layer thickness of (a) and (b) to be 0.  $10322\mu\text{m}$ . The other device parameters are as follows: front gate oxide thickness 10 nm, buried oxide thickness for SOI 200nm, the thin film doping concentration for SOI and double gated MOSFET being  $6 \times 10^{16} \text{cm}^{-3}$ . The difference between the source/drain

FIG. 2 Schematic Plot of 1-D Solutions and Source/Drain Boundary Conditions for (a) Uniform Channel Doping Bulk MOSFET, (b) Intrinsic Channel Doping Bulk MOSFET, (c) SOI MOSFET and (d) Double-Gated SOI MOSFET.

boundary condition and 1-D solution at the front gate/channel interface is about 0.2V (our calculation shows l is not sensitive to the gate bias). The calculated result of l is shown in Table 1. Also shown in this table is the result using the model in Ref. [4].

Table 1 Calculated Result of 1 for Different Device Structures (unit: m)

| Device Structure                            | DSOI1 | DSO12 | Intrinsic | U niform | SOI    |

|---------------------------------------------|-------|-------|-----------|----------|--------|

| Calculated $\boldsymbol{l}$ using our model | 0.048 | 0.084 | 0. 075    | 0.080    | 0. 089 |

| Calculated l using [4]'s model              | 0.039 | 0.056 | 0. 035    | 0. 035   | 0.056  |

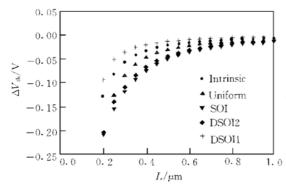

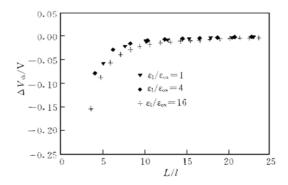

FIG. 3 Threshold Voltage Roll-Off for Different Device Structures

The discrepancy between the two model's results is apparent. Our model determines  $l_{DSO11} < l_{intrinsic} < l_{uniform} < l_{DSO12} < l_{SO1}$ , while Ref. [4] 's model determines  $l_{intrinsic} = l_{uniform} < l_{DSO11} < l_{DSO12} = l_{SO1}$ . To check the real situation, 2-D numerical simulation for these device structures is carried out using these device structures is carried out using where  $\Delta V_{th} = V_{th}(L) - V_{th}(3\mu m)$ . Threshold voltage  $V_{th}$  is defined as the gate voltage at drain current  $I_{ds} = W/L \times 0$ .  $1\mu A$  with  $V_{ds}$  being 0.05V. This figure agrees with our

model's result very well.

# 4 Investigation of Electrical Equivalent Oxide Thickness Approximation

In order to further increase the current driven ability and overcome the short channel effect in the ultra-short channel devices, sub-2nm gate oxide is applied in recent research.

But the ultra-thin gate oxide also introduces the unacceptable high tunneling gate current. To solve the problem, relative thick high- permittivity dielectric is suggested acting as an alternative to the gate oxide. This approach is motivated by the electrical equivalent oxide thickness concept, i. e., if the ratios of gate dielectric thickness to permittivity are the same, the device characteristics should be the same. Obviously, this conclusion reglects the 2-D effects in the gate dielectric and their action in thick high-permittivity dielectric is questionable. To demonstrate this point, we apply (4) to the different gate dielectric double-gated MOSFET short channel effect analysis. If the 1-D solution in the double-gated MOSFET silicon film is approximated as a constant (as is the real situation if the silicon film is intrinsic), (4) can be simplified as further

$$l = \left[ \frac{1}{3} \left[ \frac{\epsilon_{\rm I} t_{\rm ox}^{\rm eq}}{\epsilon_{\rm ox}} \right]^2 + \frac{\epsilon_{\rm Si}}{2\epsilon_{\rm ox}} t_{\rm Si} t_{\rm ox}^{\rm eq} \right]^{1/2}$$

(5)

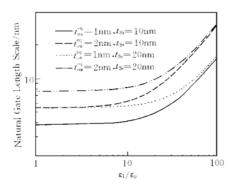

where  $\epsilon_{ox}$  is the gate dielectric permittivity,  $t_{ox}^{eq} \equiv t_1 \epsilon_{ox}/\epsilon_1$  is the electrical equivalent oxide thickness, where  $t_1$  is the front and back gate dielectric thickness. Figure 4 shows the dependence of the scale length l on the gate dielectric constant  $\epsilon_l/\epsilon_0$  for several values of  $t_{SI}$  and  $t_{ox}^{eq}$ , where  $\epsilon_0$  is the permittivity of the free space. This plot suggests that the equivalent oxide thickness approximation only be valid at a relative small dielectric constant (approximately < 10), and the effectiveness of applying high-permittivity dielectric as gate material would degrade out of this range. The numerical simulation result further confirms our conclusion, which is shown in Fig. 5. The uniform distribution of these points confirms our model can model the 2-D effect in the gate dielectric for a wide range of  $\epsilon_1$ .

FIG. 4 Plot of Natural Gate Length Scale Versus Dielectric Constant for Some Different Values of Equivalent Oxide Thickness  $t \mathbb{S}_1$  and Silicon Film Thickness  $t \mathbb{S}_1$

FIG. 5 2-D Simulation Result of  $\Delta V_{\rm th}$  Versus L/l for Different  $\epsilon$ :

The silicon film doping concentration is  $6\times 10^{16}{\rm cm}^{-3}$  and  $t_{\rm eq}^{\rm eq}=2{\rm nm}$ ,  $t_{\rm Si}=20{\rm nm}$ .

#### 5 Conclusion

In conclusion, we present a simple unified scaling theory in this paper, which applies to different device structures. Compared to other quasi-2-D methods, our approach also includes the 2-D effects in the front and back gate dielectrics. 2-D effect comparisons between different device structures and different gate dielectric constant are conducted in this work, and all the model predictions are confirmed by 2-D numerical simulations.

#### References

- [1] J. R. Brews, W. Fichtner, E. H. Nicollian and S. M. Sze, IEEE Electron Device Lett., 1980, EDL-1: 2-4.

- [2] K. K. Young, IEEE Trans. Electron Devices, 1989, 36: 399-402.

- [3] Z. Liu, C. Hu, J. Huang, T. Chan, M. Jeng, P. Ko and Y. Cheng, IEEE Trans. Electron Devices, 1993, 40: 86.

- [4] R. H. Yan, A. Ourmazd and K. F. Lee, IEEE Trans. Electron Devices, 1992, 39: 1704-1710.

- [5] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie and Y. Arimoto, IEEE Trans. Electron Devices, 1993, 40: 2326-2329.

- [6] C. P. Auth and J. D. Plummer, IEEE Electron Device Lett., 1997, 18:74-76.

- [7] Zhang Wenliang and Yang Zhilian, Chinese Journal of Semiconductors, 1997, **18**(11):877—880(in Chinese)[张文良, 杨之廉, 半导体学报, 1997, **18**(11):877—880].

- [8] D. J. Frank, Y. Taur, H. P. Wong, IEEE Electron Device Lett., 1998, 19(10): 385-387.

- [9] Chen Wensong, Tian Lilin, Z. Yu and Li Zhijian, Chinese Journal of Electronics, 1998, 17(2): 152-157.

- [10] J. M. Pimbley, J. D. Meindl, IEEE Trans. Electron Devices, 1989, 36(9): 1711-1720.

- [11] J. Y. Guo and C. Y. Wu, IEEE Trans. Electron Devices, 1993, 40(9):1653—1661.

- [12] G. Arfken, Mathematical Methods for Physicists. Orlando, Florida: Academic Press, 3rd edition, 1985.

- [13] MEDICI: Two dimensional device simulation program, ver. 2. 0, TMA Inc. 1994.